- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

FPGA和EZ-USB FX2在采集 像数据中的应用

摘 要:利用FPGA和EZ_15SB FX2(CY7C68013)将MT9M112(Sensor)数据准确无损地传给PC机。方案使用CY7C68013控制器工作在Slave FIFO从机方式,用Verilog HDL语言在FPGA中产生相应的控制信号,最终实现对数据的快速传输,在上位机得到Sensor采集的清晰画面。该方案的传输速度快,数据准确,可扩展到其他需要通过USB进行快速数据传输的系统。与其他采用异步通信方案相比,设计利用FPGA缓冲作用,使数据无丢失传输,最终在上位机得到的图像更加清晰流畅。该设计方案和产品达到国际先进水平。

关键词:同步传输;异步传输;数据流;FIFO_Core;slave FIFO

由于一维码、二维码以及图像扫描处理等方面都涉及到了PC机和下位机间的数据传输,而传输数据阻塞问题又是制约图像效果的根本原因,该方案很好地解决了这个问题。设计采用美光的CMOS图像传感芯片MT9M112作为图像采集部分,通过EZ_USB。FX2的USB微控制器芯片68013a将采集到的数据传送到PC机,由PC机对二维码图像进行显示并做解码处理。由于MT9M112输出的是8位的串行图像数据流,直接与68013a的从FIFO接口对接不能保证数据完整不丢失,并且无法在数据中加入帧识别信息。在这种情况下采用了FPGA完成此部分逻辑功能。通过FPGA对图像数据做相应的调整再交给68013a传送到上位机。

1 详细设计方案及性能分析

1.1 硬件系统框图

硬件系统框图如图1所示,实现了各模块数据信号和控制信号的链接。

1.2 Sensor输出部分说明

MT9M112的输出具有以下的特性:MT9M112内部有一个PLL锁相环,通过相应的寄存器设置可调整输出数据的同步时钟,默认输出ITU_R BT.656(YCbCr)格式的数据流。LINE_VALlD指示一个行有效数据输出周期,FRAME_VALID指示一个帧输出周期,在帧和行同时有效时以像素时钟PIXCLK为基准输出8位的图像数据,根据时序,只要行有效为高,输出总线有图像数据,这样就可以将FPGA的写是能改为高有效(默认低有效),直接将行有效信号连接到写使能管脚,从而控制向FPGA FIFO的写。

1.3 FPGA内部模块及主要原理

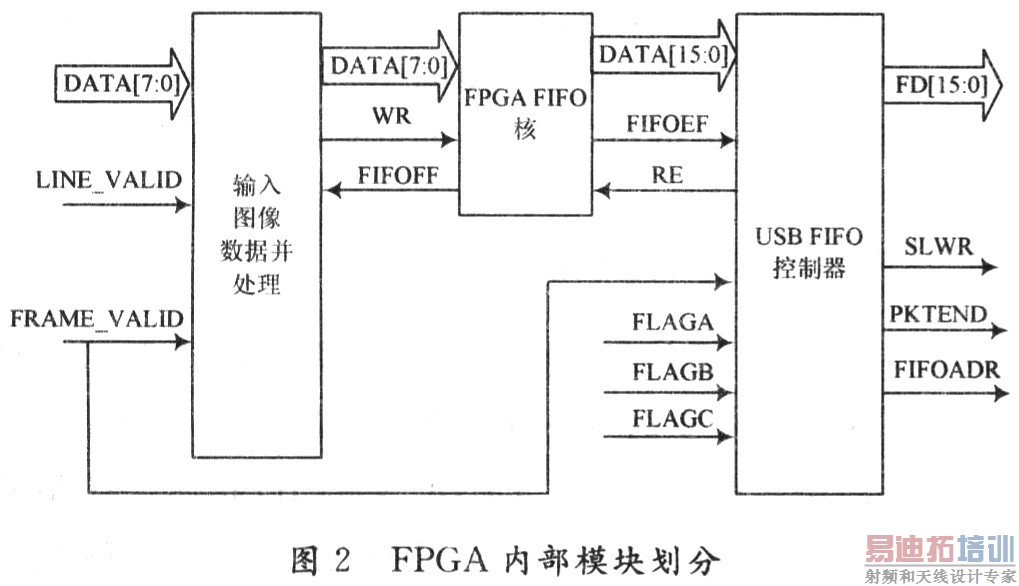

在FPGA开发工具中创建F1FO_Core,设置其输入数据位宽为8 b格式,输出数据宽度为16 b格式,目的是在控制时钟不变的情况下加快传输数据速率。时钟选为single clock,即FPGA FIFO核的读和向USB FIFO的写用同一时钟.PIXCLK,同时利用Verilog HDI,语言实现其内部模块互连。脱机解码时上位机程序为了识别一个有效的帧数据段,在下位机传递数据时,在每帧图像数据间插入了16 B的同步数据(该数据可由工作人员决定),以鉴别一帧图像开始。设计将同步数据中将同步信息分为4个4 B数据。第一个数据为同步头,向上位机发数据固定为0xAA550000,第二个数据表示图像的比例,高字节为行,低字节为列。第三以及第四个数据为保留字目前为O。FPGA除负责传输有效的帧图像外还要在两个图像帧数据之间插入同步数据。是在FRAME_VALID的下降沿到来后(即一帧数据传输结束后发同步信息)并且FPGA的FIFO empty_flag有效时发送,以此来判断下一帧数据的开始,FPGA FIFO核与USB及图像数据关系如图2所示。

1.4 68013a从FIFO接口

Sensor采集的数据经过FPGA做处理写到EZ_LISB FX2 68013A的从FIFO,由EZ_USB FX2 68013A将数据打包放送到上位机。由于上位机的数据同步为固定的同步信息,不涉及到FPGA回读上位机数据部分,所以此处只涉及到写EZ_USB FX2 68013A的从FIFO。数据总线FD可编程选择为8位或是16位的位宽(该方案通过FPGA的FIFO_Core将总线数据转换为16位格式,从而在控制时钟不变的情况下加快传输数据速率),同步传输时钟由外部提供时,通过外部对IFCLK引脚引入PIXCLK时钟(同步电路)。EZ_USBFX2 68013A有4个端点,通过FIFOADR设置选择数据总线与EP6对应,并可编程调整对应的FIFO深度。通过固件编程可将FLAGA,FLAGB,FLAGC调整为对应哪个内部FIFO的对应满空状态。PKT、END用于手动打包传输数据,当固件程序设置68013a的EPx-AUTOINLENH:L为512 B,当ALITOIN=1时68013a将自动以512 B为单位打包传输到USB上。在异步传输时SLWR用于锁存总线数据,在同步传输时SLWR做为使能信号,在SLWR为低,每个IFCLK上升沿锁存总线数据,至此完成这个项目的数据流控制设计。

2 结 语

通过以上设计,成功地实现了MT9M112,FPGA和。EZ_USB FX2 68013A之间的通信,该方案将CMOS图像传感芯片MT9M112的数据完整地传输到PC机,在PC机经数据处理(可选择提取Y信号或将全部信号),解码后可得清晰的灰度或彩色图像。方案通过FPGA的FIFO_Core实现了8位数据向16位数据的转换,然后利用EZ_USB FX2 68013A Slave FIFO的EP6端口把数据传给PC机,实现了同步通信。与目前社会上用DSP处理器异步通信相比,利用FPGA不仅降低了成本而且解决了数据传输过程中易阻塞的问题,实现了数据无缝传输,得到的图像也更为清晰流畅。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...