- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于DSP的MEMS陀螺仪信号处理平台设计

0 引 言

陀螺仪是一种能够精确地确定运动物体方位的仪器,它是现代航空、航海、航天和国防工业中广泛使用的一种惯性导航仪器,它的发展对一个国家的工业,国防和其他高科技的发展具有十分重要的战略意义。

近年来随着MEMS(微机电系统)技术的发展,MEMS陀螺仪的研究与发展受到了广泛的重视。MEMS陀螺仪具有体积少、重量轻、可靠性好、易于系统集成等优点,应用范围广阔。但是目前MEMS陀螺仪的精度还不是很高,要想大范围应用必须对MEMS陀螺仪的信号进行处理。

本文选用TI公司的TMS320VC33作为MEMS陀螺仪信号处理平台的核心芯片,同时引入DSP/BIOS实时操作系统提供的多任务处理机制,在对陀螺仪信号进行数据采集的间隙同时对先采集来的信号数据进行处理和传输,确保数据采集和处理的实时性,大大提高了信号处理平台的工作效率,在高速实时数据采集和处理领域具有一定的应用价值。

1 MEMS陀螺仪信号处理平台的硬件结构

1.1 信号处理平台的硬件结构及工作原理

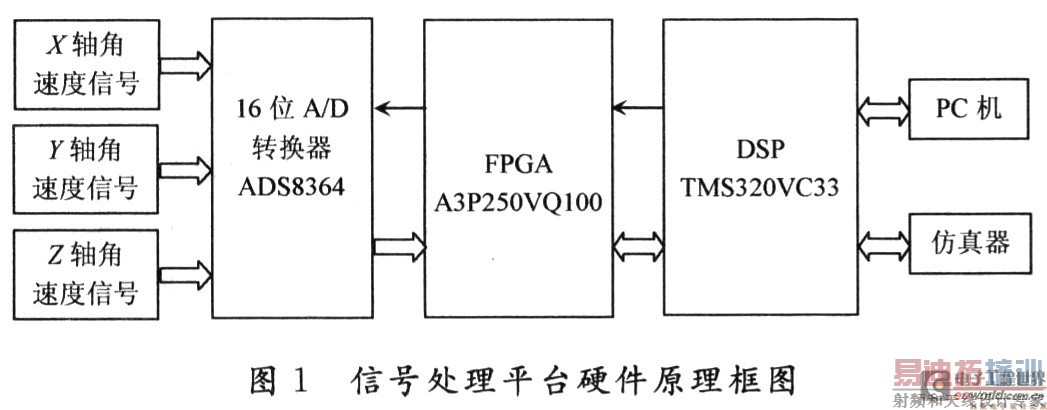

MEMS陀螺仪信号的处理平台的硬件系统应该包括以下几个部分:DSP模块,数据采集模块,上位机通信模块和JTAG调试接口模块。

数据采集模块由两部分组成:6路16位模/数转换器ADS8364和同步时序控制器FPGA(A3P250VQ100)。FPGA(A3P250VQ100)一方面是控制各个单元时序,另一方面是为了对A/D采集来的陀螺信号进行预处理。

模/数转换器ADS8364通过FPGA与DSPVC33相连,采集三轴陀螺信号。

DSP主要完成对陀螺信号的降噪运算。陀螺信号经DSP处理后再由SCI接口传送到上位机。

系统设计的原理框图如图1所示。

在图1中三路陀螺模拟信号经过各自的信号调理、抗混迭滤波后进入多通道A/D转换器,在FPGA的控制下选择一路信号进行转换,转换结果送入FPGA片上FIFO缓存,由DSP读取数据并进行数字信号处理。同时FPGA对A/D转换器传过来的信号进行预处理,再送到DSP进行信号降噪处理,保证了MEMS陀螺信号处理系统处理的实时性。然后DSP把处理后的结果送至上位机和经过串口输出,完成数字输出和模拟输出,满足不同的应用要求。

1.2 信号处理平台A/D电路设计

在整个MEME陀螺信号处理平台中,A/D转换器是整个系统数据采集部分关键核心器件,信号处理系统中选用了美国德州仪器(TI)公司的ADS8364作为MEMS陀螺信号处理平台的A/D转换器。ADS8364是TI公司推出的高速、低功耗、6通道16位A/D转换芯片,共有64个引脚。其时钟信号由外部提供,最高频率为5 MHz,对应的采样频率是250 kHz。数字电源供电电压为3~5 V,即可以与3.3 V供电的微控制器接口,也可以与5 V供电的微控制器接口。所以ADS8364非常适合应用在精度要求较高,结构简单的嵌入式信号处理系统中。

ADS8364的时钟信号由外部提供,这里由FPGA提供时钟信号,主要是考虑到FPGA可以灵活地改变时钟频率,进而改变系统的采样频率。A/D转换完成后产生转换结束信号EOC。将ADS8364的BYTE引脚接低电平,使转换结果以16位的方式输出。地址/模式信号(A0,A1,A2)决定ADS8364的数据读取方式,可以选择的方式包括单通道、周期或FIFO模式。将ADD引脚置为高电平,使得读出的数据中包含转换通道信息。考虑到数据采集处理系统的采样频率一般较高,如果用DSP直接控制ADS8364的访问,将占用DSP较多的资源,同时对DSP的实时性要求也较高。因此在本系统设计中,用FPGA实现ADS8364的接口控制电路,并将转换结果存储在FPGA中,用DSP实现FPGA芯片的输出接口。图2为ADS8364与FPGA的接口电路设计图。

[p]

[p]

1.3 DSP的串行通信接口设计

TMS320VC33 DSP中的串口是一种同步串行接口,串行通信接口(SCI)是采用双线通信的异步串行通信接口,即通常所说的UART口,VC33内部带有串行通信模块,该串口支持16级接收和发送FIFO,可以与PC和其他异步通信外设进行数字通信,在信号处理平台系统中采用RS 232通信方式将数据发给上位机,与TMS320VC33接口的外设选用MAX3232。

2 MEMS陀螺仪信号处理平台系统任务分析

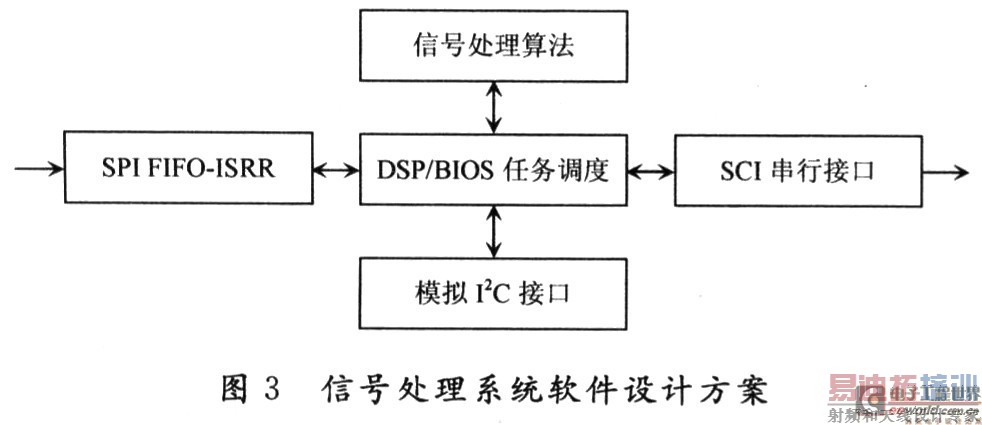

MEMS信号处理系统划分为三个独立的任务:数据采集任务、陀螺信号处理任务和上位机通信任务。各个任务之间通过DSP/BIOS的旗语信号量进行同步和协调。

数据采集任务是负责对MEMS陀螺的信号进行采集。该任务是系统的关键部分,优先级最高,执行时间比其他任务短,因此选用DSP/BIOs的硬件中断模块(HWI)。硬件中断模块(HWI)具有严格的实时性和高优先级,一旦SPIFIFO接收寄存器被外部ADC写满,立即产生相应的中断,CPU立即挂起当前的任务,调用相应的中断服务程序数据采集任务,将FIFO缓冲区内的采样值读入接收数据缓冲区,启动后续采样。这时中断服务程序退出,CPU的控制权返还给先前的任务。

陀螺信号处理任务负责对采集到的数字量信号进行小波除噪和温度补偿等算法处理。在设计时引入了DSP/BIOS的另一种线程类型TSK来实现。任务是独立使用的CPU进程,真正体现了多线程的思想,支持阻塞和优先级抢断。

TSK共有15个优先级,每个任务均有自己独立的堆栈,响应延时比较长,适合对实时性要求不是很高的进程。TSK对象的优先级低于硬件中断(HWI),可根据任务的优先级和当前执行状况调度或抢占任务。陀螺信号处理任务在数据采集任务的空闲周期执行,也就是在采样值写入FIFO缓冲区这段时间执行。当数据采集任务执行完成,发送旗语信号量SEM_PROC陀螺信号的处理任务,对数据缓冲区内的采样值进行处理,如果没有收到旗语信号量SEM_PROC任务自动挂起。

上位机通信任务负责系统与外部通信,将处理完成的数据通过SCI接口传输给上位机。上位机通信任务同样采用DSP/BIOS中的TSK线程实现。上位机通信任务的优先级低于任务陀螺信号处理任务,在数据采集和信号处理的间隙执行。陀螺信号处理任务执行完成,发送旗语信号量SEM-XMIT上位机通信任务,将数据送出。

3 MEMS信号处理平台软件设计方案

MEMS陀螺仪信号处理平台的软件设计包括DSP程序设计、FPGA控制和时序程序设计。DSP编程的主要任务是初始化、管理板上的资源,并实现前端数字信号处理的算法。这里以TI公司提供的功能强大的CCS(Code Composer Studio)为集成开发环境。

系统上电复位后。首先完成DSP自身的初始化,包括配置RAM模块,设置I/O模式、定时器模式、中断等,然后程序进人循环状态,等待中断。

FPGA的软件设计主要包括对A/D的采集控制、数据存储与传输的控制、信号的预处理和同步时序的产生与控制。首先由FPGA把A/D采集来的MEMS陀螺仪的数据存储在FPGA中,然后由FPGA对采集来的信号进行预处理,然后等待DSP的控制信号把预处理的信号送入DSP中进行信号处理和传输。系统软件的设计方案如图3所示。

4 结 语

本文设计的MEMS陀螺信号处理平台,能够完成三轴陀螺信号的采集和处理,并将处理过的MEMS陀螺信号发送给主机,由于采用了TI公司高性能的DSP芯片TMS320VC33,并在软件设计中采用了DSP/BIOS多任务机制,使得该信号处理平台具有体积小,精度高,实时性好等优点,能够满足对MEMS陀螺信号处理,在实际应用中具有一定的参考价值。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...