- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于Camera Link接口的 像跟踪系统的设计

目前使用的图像跟踪系统前端输入信号一般都是PAL制式的标准全电视信号,每20 ms一场,每40 ms一帧。模拟信号经过视频解码器转换成720×576大小的数字信号后,再对其中的目标进行分割、识别和跟踪,并准确计算出目标的位置角度偏差,并传给伺服机构。在某系统中要求能对3×3像素大小的小目标进行精确跟踪,为了达到跟踪精度,可以提高图像输入的帧频和提高图像输入的分辨率,因此前端采用了 DALSA公司的一款基于Camera Link接口的数字摄像机,该相机的帧频为100 Hz,分辨率高达1 400×1 024。这样帧处理时间就只有10 ms,考虑到系统的实时性,我们采用了TI公司的高性能的DSP芯片TMS320C6414和高性能FPGA芯片EP2S30F672为核心的硬件处理平台。

1 系统硬件结构和工作原理

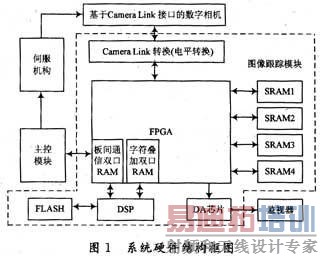

整个图像跟踪模块的结构图如图1中虚线框所示,整个系统包括以FPGA为核心的图像采集和预处理单元,以DSP为核心的图像处理单元以及由FPGA控制的图像显示单元。

由于采集、处理、显示均要访问存储器,为了降低成本,用普通的异步SRAM构成。按照功能来分可分为采集处理用SRAM组和采集显示用SRAM组,每组分别包括两片SRAM,其读写逻辑由FPGA控制,采用乒乓方式进行切换。

对于采集处理部分,第K帧时,SRAM1由FPGA控制写入图像数据,同时SRAM2由DSP读数进行处理;第K+1帧时则相反,SRAM2由FPGA控制写入图像数据,同时SRAM1由DSP读数进行处理。

对于采集显示部分,第K帧时,SRAM3由FPGA控制写入图像数据,同时SRAM4由FPGA读数进行显示;第K+1帧时则相反,SRAM4由FPGA控制写入图像数据,同时SRAM3由FPGA读数进行显示。

整个系统工作过程都是这样的:其中图像采集单元经由差分转换芯片后变成LVTTL信号,直接连至FPGA,由FPGA控制数字图像的采集,进行图像预处理后,将图像数据存储在SRAM中,给DSP发出中断信号,DSP响应中断后,从SRAM中读取一帧图像数据后,进行图像分割、目标提取、目标跟踪算法,计算出方位和高度角偏差分量,将结果通过FPGA的片内的板间通信双口RAM传递给主控模块,主控模块再调整伺服机构保证被跟踪的目标处于视场中心。

主控模块还可以将系统的一些状态变量实时的通过板间通信双口RAM传给DSP,DSP根据这些状态生成需要显示的字符,将这些字符写入到FPGA片内字符叠加双口RAM中。FPGA读取显示RAM中的图像数据和片内字符叠加双口RAM内的数据,在原图上叠加十字丝和波门,以及系统的一些状态字符信息,按照 PAL制式时序向DA芯片送视频数据,这样监视器就可以输出标准的PAL制式的图像。

2 各个单元设计

2.1 基于Camera Link接口的图像采集和预处理单元

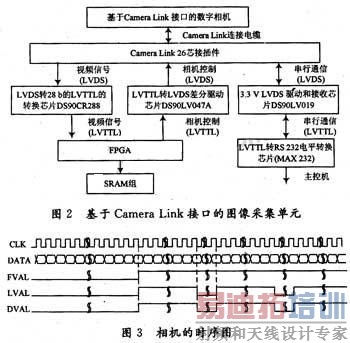

Camera Link是一种基于视频应用发展而来的接口,它解决了视频数据输出和采集之间的速度匹配问题。Camera Link数据的传输率非常高,可达1 Gb/s,采用了LVDS格式,抗噪性能好。Camera Link的信号包括三个部分:串行通信部分、相机控制部分、视频信号部分,基于Camera Link接口的图像采集单元详图见图2,每个部分采用专门的差分转换芯片。串行通信部分则将异步串口转换成标准的RS 232电平,这样可以由主控机对相机的曝光时间、对比度等设置进行调节。相机控制部分包括4对差分信号,用来对相机进行控制,比如相机的外同步信号输入控制,可以由FPGA进行控制。视频部分的28 b LVTTL信号是关键控制部分,它们直接接在FPGA上,由FPGA来控制采集的时序。 [p]

这28 b数据中包括3个数据端口:A口(8 b)、B口(8 b)、C口(8 b),和4个视频控制信号FVAL(帧有效)、DVAL(数据有效)、LVAL(行有效)、SPARE(空,暂时未用)。至于经过Camera Link芯片转换后的时钟信号,则是整个相机的同步驱动信号,所有的数据和视频控制信号都是和该时钟信号同步的,相机的时序图见图3。

相机可以配置成8 b或10 b的输出位宽,40 MHz像素时钟或80 MHz像素时钟,2×40 MHz或2×80 MHz的数据输出速率。关于Camera Link的采集数据的逻辑代码,关键之处在于产生存储器的地址信号、存储器写信号以及在对应的地址处将数据稳定地写进存储器。我们用像素时钟产生列地址计数器,行同步信号产生行地址计数器,二者拼接产生存储器的地址信号。这样产生的有效地址虽然不连续,但意义明确,而且有利于显示部分的隔行隔列显示。对于 8 b的数据,可将4个有效数据拼接成32 b后再存储,这样可以降低FPGA读写存储器的速度。

2.2 基于FPGA的图像预处理单元

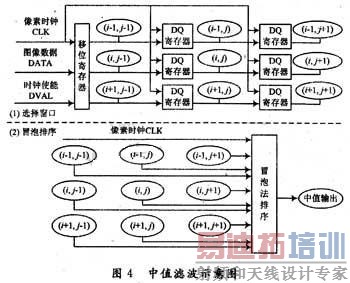

针对图像预处理阶段运算结构比较简单的特点,用FPGA进行硬件实现无疑是理想的选择,这样同时兼顾了速度和灵活性,大大减轻了DSP的负担。这里采用的预处理算法主要是中值滤波,中值滤波器是一种非线性滤波器,与均值滤波器和类似其他形式的滤波器相比,中值滤波器具有能够彻底滤除尖波干扰噪声同时又能够较好地保护目标图像边缘等优点。中值滤波的具体实现过程一般为:

(1)选择一个n×n的滑动窗口(通常为3×3或者5×5),使其沿图像数据的行或者列方向逐像素滑动(通常为从左至右,从上到下逐行移动)。

(2)每次滑动后,对窗口内的像素灰度值进行排序,用排序所得的中间值代替窗口中心位置像素的灰度值。

用硬件实现二维中值滤波,很重要的一点是能可靠地存储实时图像数据,并且使延时最短。在存储n-1行图像数据后便开始处理,其中n为窗口大小,在本设计中,选用3*3窗口的中值滤波器,即n=3。这样设计的好处是,FPGA可以以串行流水方式实现该模块,节省了许多时间,为实时处理创造了有利条件。

为了尽量节约资源,充分利用硬件设计中的“模块复用”原则,需设计1个移位寄存器、1个dq寄存器、1个二值比较器,然后在像素时钟的驱动下,首先调用移位寄存和dq寄存器产生窗口数据,然后对3×3模板里的数据多次调用dq寄存器和2值比较器进行冒泡排序输出中间值。中值滤波模块示意图见图4。

2.3 基于DSP的图像处理单元

TI公司的TMS320C6414芯片是一款高性能定点DSP处理器,其主频可以高达720 MHz,片内具有丰富的RAM资源,同时通过EMIFA和EMIFB口可以扩展很多存储芯片。这里主要扩展的是程序FLASH芯片,用于存放固化的程序代码。

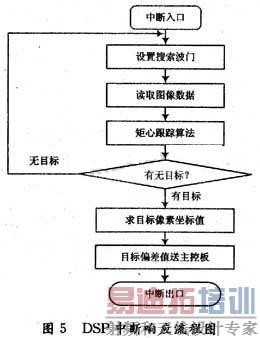

前面已经说明了FPGA如何控制SRAM读写逻辑的,DSP的主要工作是响应FPGA发出的中断信号,读取图像数据进行处理,虽然每一帧读取的实际的 SRAM不同,但是通过FPGA的映射后,对于DSP来说,SRAM始终在DSP片外的一端固定地址范围内。DSP响应中断的流程图见图5。 [p]

以常用的最简单的矩心跟踪算法为例,DSP每次响应中断后,主要进行的工作是:首先设定搜索的波门,将波门内的数据通过DMA方式快速搬移到片内存储器,然后用矩心跟踪算法进行处理,直至搜索出目标后,将目标的像素的位置偏差计算出来并送给主控板。

2.4 基于FPGA的图像显示单元

系统要求输出标准的PAL制式的模拟视频,由于PAL制式视频场频为50 Hz,帧频为25 Hz,所以对于前端高分辨率高帧频的数字图像,必须降频输出,且分辨率也要降低。选用专用的图像DA芯片ADV7123,该芯片输入位宽为10 b,可以转换的数据速率可达240 MHz。因为标准的PAL制式视频一帧只能显示有效行576行,对于1 024行的数据图像只能隔行显示512行,且奇场256行,偶场256行。所以对于采集的图像来说行方向上是降低了分辨率,但在列的方向上不降低分辨率。

由前面可知,由于采集显示采用乒乓结构,但是由于显示是隔行抽点显示的,且显示的频率帧频为25 Hz,所以在采集部分时,应当隔行取数据存储,且每2帧才更新一次采集的数据。不像采集处理部分一样,每帧都要更新采集的数据。

控制ADV7123的时钟信号、复合同步信号、复合消隐信号均由FPGA产生。与电视相关的行、场同步和消隐信号正是PAL制式模拟视频信号生成的关键。

FPGA 认通过对数字相机下来的80 MHz时钟倍频后,经过时钟计数和逻辑组合运算获得所需要的各种同。步时序信号。ADV7123的时钟信号根据80 MHz时钟先2倍频后蒋5分频而成,即像素时钟频率为32 MHz,周期为31.25 ns。生成的图像大小为1 400×576像素,即每场图像有288行,每行有1 400个像素点。系统采用PAL制式的隔行扫描方式,场周期时间为20 ms,行周期为64μs,所以每场包含312.5个行周期,但场消隐的高电平持续288个行周期,只要调整场消隐信号的起始位置,就很容易使视频图像的输出位于屏幕的正中间。行场同步信号和消隐信号的实现思路基本上一样:对时钟计数,计到某一个数值时,使输出的信号翻转(由低电平到高电平或者由高电平到低电平),计数器的周期和翻转的周期根据不同的参数而有所不同。由于这些时序是在FPGA中编程实现,很容易调整和修改。

至于字符叠加过程,DSP按照在图像上实际叠加字符的位置和大小将要叠加的字符点阵写入到FPGA片内双口RAM中(显示字符的地方写二进制的1,显示图像的地方写二进制的0),显示输出的每一帧,FPGA读取字符叠加双口RAM,根据其值来决定是输出采集的图像还是输出叠加字符。这样通过DSP和FPGA 的配合,可以灵活地叠加任何字符,DSP可以根据系统的任何状态变化来改变字符叠加RAM中的值,因此保证系统具有良好的人机交互界面。

3 结语

以高性能DSP和FPGA为核心,对Camera Link接口的数字相机进行图像采集,采用数字图像处理技术,建立了一个实时的图像跟踪系统。该系统体积小、重量轻、可靠性高,具有良好的人机交互界面,已经成功地应用在实际项目中。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...