- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

FPGA多接口功能在航姿计算机中的应用

引言

捷联惯导中的航姿计算机实现数字平台导航,需要在复杂运算的同时还能够高速、准确地完成多种传感器测量数据的采集以及航姿结果和系统状态的传送。通常的做法都是用一片或多片 DSP芯片来完成,但是当数据接口较多而且数据传输频率较高时,这类系统的实时性就难以得到保证;而 FGPA具有丰富的硬件资源,能够真正实现多模块并行工作,而且可以达到较高的工作频率。另外,用 FPGA 设计航姿计算机,还具有以下突出的优点:低成本、低功耗、小体积、可重新编程、升级方便、VHDL 设计电路可复用等。本文详细介绍了在接口较多的航姿计算机中,怎样设计 FPGA使得多种通讯接口功能都能实时可靠地实现,具有实际工程意义。

1系统总体设计

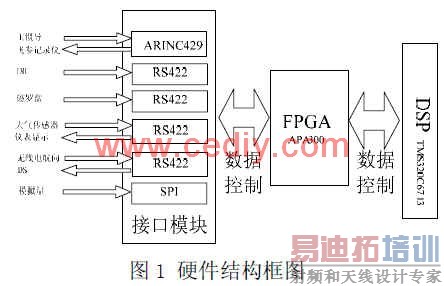

图 1为该捷联航姿系统的硬件结构框图。该系统需要高速、实时地采集多种传感器(包括大气传感器、IMU、磁罗盘)的测量数据,以及一些有关的模拟量,用于 DSP中高精度的航姿解算,同时也需要将航姿信息和系统信息发往多个设备(包括飞参记录仪、显示仪表和DS)发送。采集数据需要同时用到的接口包括ARINC429、RS422、SPI、与 DSP并行接口等多种接口;如此多数量、多种类的接口的完成还必须保证准确性和实时性。这整个系统的时序、逻辑控制都是由 FPGA完成的,DSP(选用 TI公司的TMS320C6713)作为从处理器专门用于航姿解算。本系统中选用的 FPGA芯片为 ACTEL公司 PA系列中的 APA300芯片,用 VHDL语言在 LibroIDE环境下对该芯片进行开发。

2多种工业接口的 FPGA实现

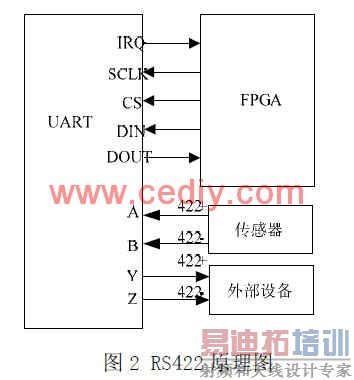

(1)RS422通讯接口。RS422标准是利用差分传输方式提高通信距离和可靠性的一种通信标准。该航姿计算机需要用 RS422接口与IMU、大气传感器、磁罗盘、无线电航表等六个外部设备通讯。由于 RS422可以支持双工工作模式,为了充分利用资源,因此设计了四个完全相同的并行的接口模块,其中每一个接口模块都是通过 FPAG控制 MAX3140芯片得以实现(如图2);同时出于设计效率的考虑,只设计了一个通用的实体,而让每一个控制模块都作为该实体的一个实例。这样,虽然这四个模块的结构完全相同,但是在顶层实体中施加不同的控制,就实现了两个单工和两个双工的工作模式。该通用的实体按照 MAX3140的工作时序图,通过控制和监测 UART的五个管脚(SCLK数据接收时钟、CS片选信号、DIN控制数据输入、IRQ中断、DOUT数据输出),完成对芯片的上电自检和对信号的接收发送;顶层实体并行地控制四个实体的工作,从而互不影响地实现了上述多路信号的接收和发送。

[p]

[p]

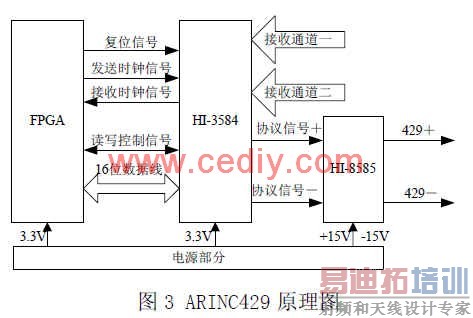

(2)ARINC429通讯接口。ARINC429协议规定了航空运输工业、航空电子系统等系统间的数字数据传输标准,是航空系统电子通讯中一种重要的接口。本系统需要通过 ARINC429接口接收主惯导的测量数据,同时通过 ARINC429接口将飞行参数发送给记录仪。出于对通讯可靠性的要求,本设计中同样采用控制接口制芯片的方式实现;通过对市面上为数不多的 429芯片进行长期的试验验证,最终采用美国 HARRIS公司的 HI-3584和 HI-8585芯片组合的形式。该芯片也支持双工模式。在 FPGA中按照 HI-3584的工作时序图,设计了一系列并行进程,用于控制和监测 HI-3584的复位信号、发送接收时钟信号、读写控制信号和 16位的数据信号(如图3)。从而完成对 HI-3582的上电自检、一个通道 429信号的接收和一个通道429信号的发送。

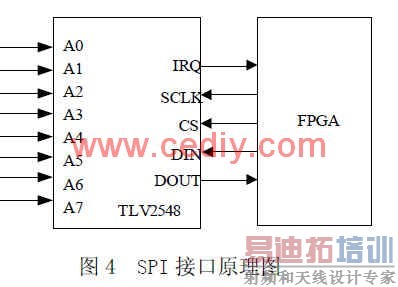

(3)SPI接口。SPI接口是一种高速、串行、全双工、同步传输方式。一般由一个主设备和一个或多个从设备通过中断、时钟、输入数据、输出数据和片选信号等 5个管脚实现。本设计需要用 AD采样芯片采集模拟量,所选的 AD芯片就是以 SPI方式与 FPGA通讯的。该 AD采样芯片为TI公司的TLV2548芯片,8通道、12位、采样频率200ksps。在FPGA中按照TLV2548的工作时序图,设计了一系列并行进程,用于控制和监测 TLV2548的中断信号、接收时钟信号、片选信号、数据输入信号和数据输出信号(如图4)。从而完成对 8路模拟量的采集。本设计最初选用外部参考,发现用于分压的精密可调电阻会随时间改变阻值,较严重影响精度,因此最后使用内部参考,真正确保了模拟量的可靠性。另外,所用的内部晶振提供高频采样,使得数据更新率高于1M,从而保证了数据的实时性。

[p]

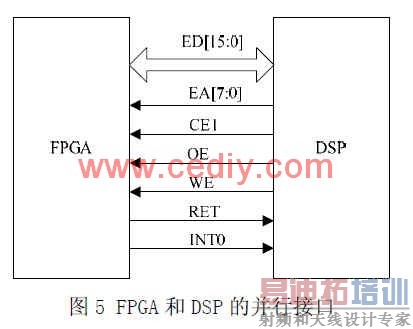

(4)与 DSP的并行接口。并行接口是最常用的一种通讯方式之一。FPGA和DSP之间的数据通讯通过 16位并行接口完成(原理图如图5)。首先,根据 DSP的时序,系统上电后需要对DSP进行不小于 200ms的复位。在系统正常工作时期,当 WE=0写有效、CE1=0片选有效、 a21=1数据有效时,FPGA从总线上读取 DSP的数据,当 OE=0读有效, CE1=0片选有效, a21=1数据有效时,FPGA将数据放在总线上等待 DSP读取。FPGA读、写数据都根据 DSP的 EA信号来标识所操作的数据地址。虽然系统中的数据量比较大,但是为了提高实时性和可靠性,在FPGA中没有使用 FIFO或者 RAM来存储数据,而只是用 FPGA中的变量来临时存储,本设计中也最终证明了该设计的可用性,这样也让 FPGA的硬件资源更合理利地得以使用。

3整体时序的实现

本系统的实时性和复杂性对于正确实现总体时序和工作逻辑提出了比较大的挑战。现从以下几个方面说明本设计的实现方法:

1 高速实时性。总体的并行设计,各个通讯模块几乎完全独立地工作,互不占用资源,从而使得高效性和实时性的要求得到了极大地满足。

2 总体时序有序。该航姿计算机的整体时序和整体逻辑都是让 FPGA中的顶层实体来控制实现的。系统大致时序和逻辑如下:上电后,FPGA控制系统完成各部件的上电自检后,各接口开始并行工作,按照自己的工作时序接收、发送数据。其中,IMU数据大约每 10ms发送一次,FPGA每次接收完 IMU数据后,与 DSP通过并行接口进行一次通讯。FPGA将最新的传感器测量值发送给DSP,而 DSP将最新的航姿信息回传给 FPGA,最终FPGA通过 ARINC429接口传给外部。这样的设计保证了系统时序稳定、逻辑可靠。

3 数据准确性。数据的准确也要求考虑到具体硬件上的问题。由于 FPGA中的逻辑门是有时间延迟的,在这样实时的系统中就必须严格考虑门电路的延时,否则,很容易出现如下类似的一些问题,例如,把刚接收到一组测量数据赋给变量是需要几纳秒到十几纳秒的时间来稳定的,如果此时正好遇上操作改变量的时钟触发,偶尔就会引起野值数据,这些不确定的野值随时可能造成整个航姿结算的错误,因此需要根据具体时序修改,以保证杜绝这类问题。

该系统的 FPGA设计已经经过模拟数据仿真试验、跑车试验得以验证,在数据准确性、实时性方面都得到了较好的满足。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:车载系统在110移动视频指挥系统中的应用

下一篇:智能车载信息系统设计