- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

有用ECO To PCB 从原理图导PCB的请进

录入:edatop.com 点击:

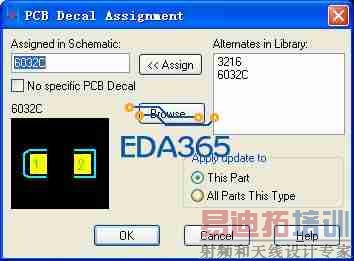

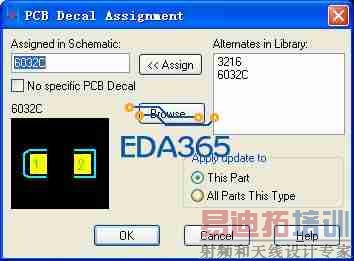

pads Logic上有一个电容元件CAPACITOR,里面设了两个pcb封装:3216和6032C,如图一

某张原理图用到了两个CAPACITOR元件,其中一个元件C181将PCB封装设为3216,另一个C108设为6032C,如图二、三

生成网表,可以找到两个PCB封装指定语句:

C181CAPACITOR@3216

C108CAPACITOR@6032C

在PCB上导入这个网表,生成的两个元件封装完全正确:一个是3216,另一个是6032C

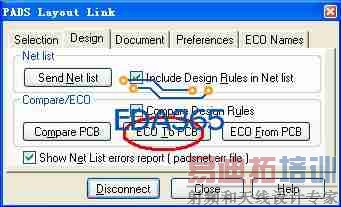

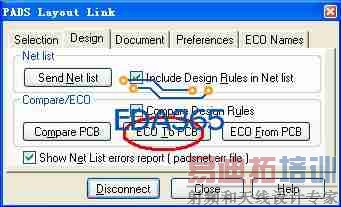

现在的问题是,我不用导入网表的方法新建PCB,而是用logic上的“ECO To PCB ”功能新建PCB,如下图

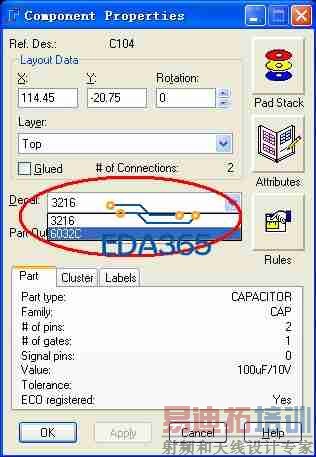

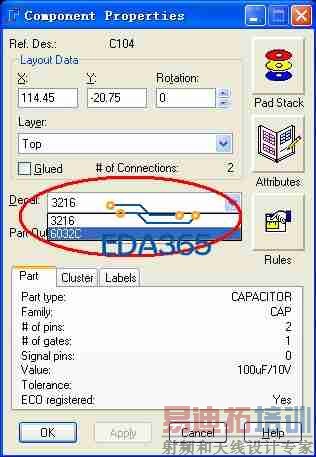

生成的PCB文件两个元件的封装都是3216,另一个则需要手动去修改,如图

是ECO哪个地方设置有误导致要手动指定而不是自动生成?

某张原理图用到了两个CAPACITOR元件,其中一个元件C181将PCB封装设为3216,另一个C108设为6032C,如图二、三

生成网表,可以找到两个PCB封装指定语句:

C181CAPACITOR@3216

C108CAPACITOR@6032C

在PCB上导入这个网表,生成的两个元件封装完全正确:一个是3216,另一个是6032C

现在的问题是,我不用导入网表的方法新建PCB,而是用logic上的“ECO To PCB ”功能新建PCB,如下图

生成的PCB文件两个元件的封装都是3216,另一个则需要手动去修改,如图

是ECO哪个地方设置有误导致要手动指定而不是自动生成?

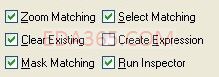

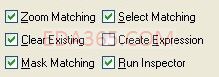

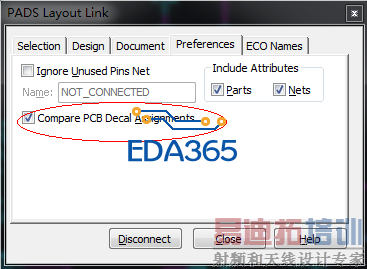

不知是不是这里

谢谢楼上! 在这个选项打上勾就可以了;

应该PADS logic在用ECO的时候没去检查封装,而导网表则会去核对封装。

:xuexi

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

射频和天线工程师培训课程详情>>