- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

详解差动放大器

简介

经典的四电阻差动放大器 (Differential amplifier,差分放大器) 似乎很简单,但其在电路中的性能不佳。本文从实际生产设计出发,讨论了分立式电阻、滤波、交流共模抑制和高噪声增益的不足之处。

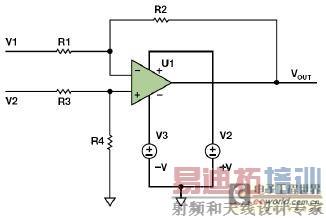

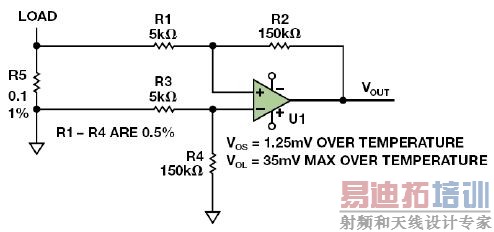

大学里的电子学课程说明了理想运算放大器的应用,包括反相和同相放大器,然后将它们进行组合,构建差动放大器。图 1 所示的 经典四电阻差动放大器非常有用,教科书和讲座 40 多年来一直在介绍该器件。

图 1. 经典差动放大器

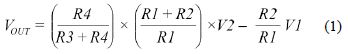

该放大器的传递函数为:

若R1 = R3 且R2 = R4,则公式 1 简化为:

这种简化可以在教科书中看到,但现实中无法这样做,因为电阻永远不可能完全相等。此外,基本电路在其他方面的改变可 产生意想不到的行为。下列示例虽经过简化以显示出问题的本质,但来源于实际的应用问题。

CMRR

差动放大器的一项重要功能是抑制两路输入的共模信号。如图1 所示,假设V2 为 5 V,V1 为 3 V,则4V为共模输入。V2 比共模电压高 1 V,而V1 低 1 V。二者之差为 2 V,因此R2/R1的“理想”增益施加于2 V。如果电阻非理想,则共模电压的一部分将被差动放大器放大,并作为V1 和V2 之间的有效电压差出现在VOUT ,无法与真实信号相区别。差动放大器抑制这一部分电压的能力称为共模抑制(CMR)。该参数可以表示为比率的形式(CMRR),也可以转换为分贝(dB)。

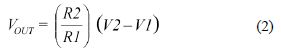

在1991 年的一篇文章中,Ramón Pallás-Areny和John Webster指出,假定运算放大器为理想运算放大器,则共模抑制可以表示为:

其中,Ad为差动放大器的增益, t 为电阻容差。因此,在单位增益和 1%电阻情况下,CMRR等于 50 V/V(或约为 34 dB);在 0.1%电阻情况下,CMRR等于 500 V/V(或约为 54 dB)-- 甚至假定运算放大器为理想器件,具有无限的共模抑制能力。若运算放大器的共模抑制能力足够高,则总CMRR受限于电阻匹配。某些低成本运算放大器具有 60 dB至 70 dB的最小CMRR,使计算更为复杂。

低容差电阻

第一个次优设计如图 2 所示。该设计为采用OP291 的低端电流检测应用。R1 至R4 为分立式 0.5%电阻。由Pallás-Areny文章中的公式可知,最佳CMR为 64 dB.幸运的是,共模电压离接地很近,因此CMR并非该应用中主要误差源。具有 1%容差的电流检测电阻会产生 1%误差,但该初始容差可以校准或调整。然而,由于工作范围超过 80°C,因此必须考虑电阻的温度系数。

图 2. 具有高噪声增益的低端检测

针对极低的分流电阻值,应使用 4 引脚开尔文检测电阻。采用高精度 0.1 Ω电阻,并以几十分之一英寸的PCB走线直接连接该电阻很容易增加 10 mΩ,导致10%以上的误差。但误差会更大,因为PCB上的铜走线温度系数超过 3000 ppm。

分流电阻值必须仔细选择。数值更高则产生更大的信号。这是 好事,但功耗(I2R) 也会随之增加,可能高达数瓦。采用较小的 数值(mΩ级别),则线路和PCB走线的寄生电阻可能会导致较 大的误差。通常使用开尔文检测来降低这些误差。可以使用一 个特殊的四端电阻(比如Ohmite LVK系列),或者对PCB布局进行优化以使用标准电阻。若数值极小,可以使用PCB 走线,但这样不会很精确。

商用四端电阻(比如Ohmite或Vishay的产品)可能需要数美元或更昂贵,才能提供 0.1%容差和极低温度系数。进行完整的误差预算分析可以显示如何在成本增加最少的情况下改善精度。

有关无电流流过检测电阻却具有较大失调(31mV)的问题,是“轨到轨”运算放大器无法一路摆动到负电源轨(接地)引起 的。术语“轨到轨”具有误导性:输出将会靠近电源轨--比经典发射极跟随器的输出级要近得多--但永远不会真正到达电源轨。轨到轨运算放大器具有最小输出电压VOL,数值等 于VCE(SAT) 或RDS(ON) × ILOAD。若失调电压等于 1.25 mV,噪声增益等于 30,则输出等于:1.25 mV × 30 = ±37.5 mV(由于存在VOS,加上VOL导致的 35 mV)。根据VOS极性不同,无负载电流的情况下输出可能高达 72.5 mV。若VOS 最大值为 30μV,且VOL 最大值为 8 mV,则现代零漂移放大器(如 AD8539)可将总误差降低至主要由检测电阻所导致的水平。

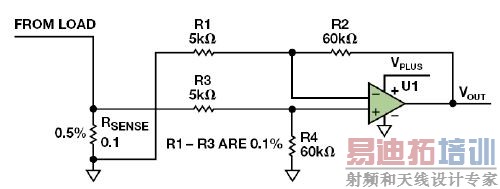

另一个低端检测应用

另一个示例如图 3 所示。该示例具有较低的噪声增益,但它使 用 3 mV失调、10-μV/°C失调漂移和 79 dB CMR的低精度四通道运算放大器。在 0 A至 3.6 A范围内,要求达到±5 mA精度。若采用±0.5%检测电阻,则要求的±0.14%精度便无法实现。若使用 100 mΩ电阻,则±5 mA电流可产生±500 μV压降。不幸的是,运算放大器随温度变化的失调电压要比测量值大十倍。哪怕VOS 调整为零,50°C的温度变化就会耗尽全部误差预算。若噪声增益为 13,则VOS的任何变化都将扩大 13 倍。为了改善性能,应使用零漂移运算放大器(比如 AD8638、 ADA4051或 ADA4528)、薄膜电阻阵列以及精度更高的检测电阻。

图 3. 低端检测,示例 2 高噪声增益

图 4 中的设计用来测量高端电流,其噪声增益为 250。OP07C运算放大器的VOS最大额定值为 150 μV.最大误差为 150 μV × 250 = 37.5 mV。为了改善性能,采用 ADA4638 零漂移运算放大器。该器件在-40°C至+125°C温度范围内的额定失调电压为 12.5 μV。然而,由于高噪声增益,共模电压将非常接近检测电阻两端的电压。OP07C的输入电压范围(IVR)为 2 V,这表示输入电压必须至少比正电轨低 2 V.对于ADA4638 而言,IVR = 3 V。

图 4. 高端电流检测

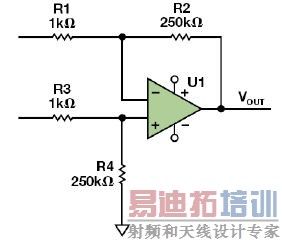

单电容滚降

图5 中的示例稍为复杂。目前为止,所有的等式都针对电阻而言;但更准确的做法是,它们应当将阻抗考虑在内。在加入电容的情况下(无论是故意添加的电容或是寄生电容),交流CMRR均取决于目标频率下的阻抗比。若要滚降该示例中的频率响应,则可在反馈电阻两端添加电容C2,如通常会在反相运算放大器配置中做的那样。

图 5. 尝试创建低通响应

如需匹配阻抗比Z1 = Z3 和Z2 = Z4,就必须添加电容C4.市场上很容易就能买到 0.1%或更好的电阻,但哪怕是0.5%的电容售价都要高于1 美元。极低频率下的阻抗可能无关紧要,但电 容容差或PCB布局产生的两个运算放大器输入端 0.5 pF的差额可导致 10 kHz时交流CMR下降 6 dB。这在使用开关稳压器时显得尤为重要。

单芯片差动放大器(如AD8271、 AD8274或 AD8276)具有好 得多的交流CMRR性能,因为运算放大器的两路输入处于芯片上的可控环境下,且价格通常较分立式运算放大器和四个精密电阻更为便宜。

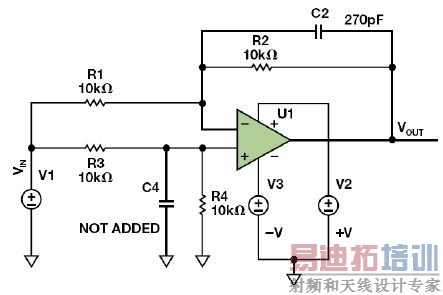

运算放大器输入端之间的电容

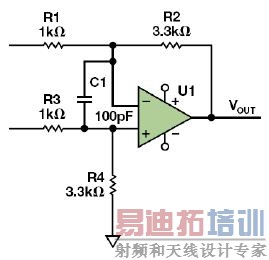

为了滚降差动放大器的响应,某些设计人员会尝试在两个运算放大器输入端之间添加电容C1 以形成差分滤波器,如图 6 所示。这样做对于仪表放大器而言是可行的,但对于运算放大器却不可行。VOUT将会通过R2 而上下移动,形成闭合环路。在直流时,这不会产生任何问题,并且电路的表现与等式 2 所描 述的相一致。随着频率的增加,C1 电抗下降。进入运算放大器输入端的反馈降低,从而导致增益上升。最终,运算放大器会在开环状态下工作,因为电容使输入短路。

图 6. 输入电容降低高频反馈

在波特图上,运算放大器的开环增益在-20dB/dec处下降,但噪声增益在+20 dB/dec处上升,形成-40dB/dec交越。正如控制系统课堂上所学到的,它必然产生振荡。一般而言,永远不要在运算放大器的输入端之间使用电容(极少数情况下例外,但本文不作讨论)。

结论

无论是分立式或是单芯片,四电阻差动放大器的使用都非常广泛。为了获得稳定且值得投入生产的设计,应仔细考虑噪声增益、输入电压范围、阻抗比和失调电压规格。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:DIY达人送上自制充电器定时插座设计

下一篇:交流稳压电源分类介绍