- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

三相SPWM波形发生器的设计与仿真

摘要:本文提出了一种采用VHDL硬件描述语言设计新型三相正弦脉宽调制(SPWM)波形发生器的方法。该方法以直接数字频率合成技术(DDS)为核心产生三相SPWM信号。并且利用VHDL设计了死区时间可调的死区时间控制器,解决了传统的模块电路等待方法很难产生带精确死区时间控制的SPWM信号的问题。该方法在Quartus II 9.1环境平台下进行了仿真验证,并将设计程序下载到DE2-70实验板进行实验测试,用示波器测试得到了死区时间可控制的SPWM波形。

引言

三相正弦脉宽调制(SPWM)技术在三相逆变电源系统、交流电机调速系统等领域有着广泛的应用[1] ,并且发挥着核心的作用。SPWM发生器是应用系统设计中的一个难点,目前SPWM波形发生器的设计方法有以下几种:(1)采用模拟电路的方法,用分立元件构成三角波、正弦波信号发生器,再通过LM311等比较器进行自然采样后输出SPWM波形。该方法对元件参数稳定性和电路可靠性要求过高,且输出信号的精度不高。(2)采用专门的SPWM波形发生器集成电路芯片,如SLE4520、SA4828等[2],但这些专用芯片的功能单一,使用不灵活。(3)随着数字芯片的发展,复杂可编程逻辑器件(CPLD)、现场可编程门阵列(FPGA)等器件得到广泛的应用。因此设计基于CPLD/FPGA器件的波形发生器是目前流行的方法[3] 。在SPWM信号发生器的设计中,产生死区时间可任意调节的SPWM信号一直是一个难点。本文利用VHDL语言设计了死区时间控制器,使得输出的两路SPWM信号的死区时间可以任意调节。本文在Quartus II 9.1平台下,采用VHDL语言与DDS技术相结合设计了一种带死区时间控制器的三相SPWM波形发生器,并在DE2-70实验平台下进行了验证。

1 方案设计

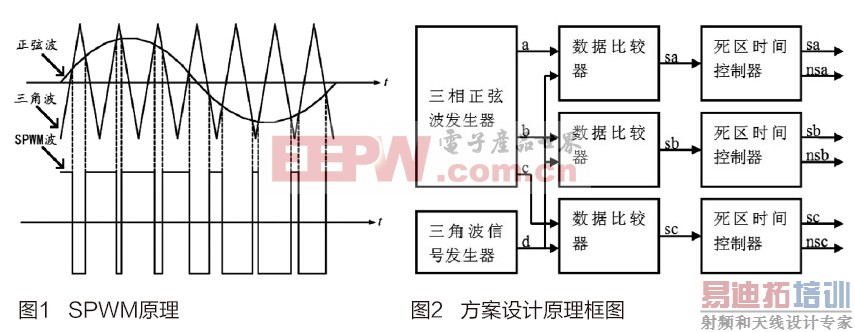

采用三角波为载波,对正弦波进行自然采样比较的方法输出SPWM,其采样的原理如图1所示。

本文设计思想为在FPGA/CPLD内存中分别存储了离散的三角波数据、正弦波数据,再利用DDS技术输出三角波数据和正弦波数据,设计一个数据比较器对以上两种波形数据进行实时比较,如果正弦波数据大于三角波数据,SPWM信号输出高电平,反之则输出低电平。根据以上原理,利用DDS技术产生相位差为120o的三相正弦信号分别与三角波信号进行比较,就能输出三相SPWM波形。

系统的总体框图如图2所示。信号a、b、c为三相正弦波数据,分别与信号d三角波数据进行比较后输出sa、sb、sc为三相SPWM波,再经过死区时间控制器后,最终得到6路SPWM波形输出。其中sa与nsa波形为反向,sb与nsb波形为反向,sc与nsc波形为反向。

2 三相正弦波发生器模块

三相正弦波发生模块如图3所示,该模块根据传统的DDS模块框图进行优化与改进。其原理是由时钟信号fclk控制累加器模块按顺序生成ROM的地址,将存储在ROM中的正弦波形数据逐个输出。

本设计中地址累加器模块地址宽度N为二进制16位,该累加器主要完成频率控制字的累加功能,从而得到ROM的寻址地址;正弦波ROM的数字位宽为8位,存储深度为256;相位控制器设置模块主要完成设置三个正弦波a、b、c的初相位差为120o的功能。由于正弦波ROM的地址线宽度为8位,而地址累加器地址宽度为16位,所以本文取地址累加器的高8位与正弦波ROM的地址线相连接。

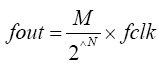

[p]本文设置正弦波a、b、c的输出频率fout为工频信号频率50Hz,令时钟信号fclk为10kHz,频率控制字M由以下公式计算。

(1)

(1)

公式转换得:

(2)

(2)

此将数据代入公式(2),可计算出频率控制字M等于327.68,取整数等于328。

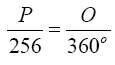

三路正弦波的初始相位设置由相位控制字设置模块完成,该模块主要完成将地址累加器的输出地址分别加上三个相位控制字再输出到正弦ROM。设相位控制字为P,对应初相为O,则计算公式如下:

(3)

(3)

因此,根据已知三相正弦波初相O分别为0o、120o、240o,代入公式(3),可求得对应的相位控制字取整数后分别为0、85、171。

3 三角波发生器模块

三角波发生器模块的设计通常有两种方法完成:(1)采用计数器方法,利用VHDL语言设计一个向上向下计数器,从0开始计数,当计数到256后再向下计数,当计数为0时,再重复以上过程。将计数器的数据输出就得到三角波数据输出,这种方法得到的三角波频率由计数器时钟决定。(2)采用DDS原理方法,具体的实现与正弦波发生器实现的原理一样,区别在于将正弦波原理框图中ROM的正弦波数据换成三角波数据。三角波频率的选择可以根据实际电路设计需要来确定,本设计中设置了三角波输出频率为3KHz,三角波频率越大,对正弦波的采样率越高,使输出的SPWM波形经过LC滤波还原为正弦波时谐波越小。

4 数据比较器模块

数据比较器模块主要完成将正弦波数据与三角波数据进行比较,输出SPWM波形。数据比较器的位宽为8位。

5 死区时间控制模块

为了防止后级H桥上下开关功率管同时闭合而造成功率管或者其它器件损坏[4] ,需要在SPWM与反向NSPWM的输出端加一个死区时间控制器,提高了后级电路的可靠性。

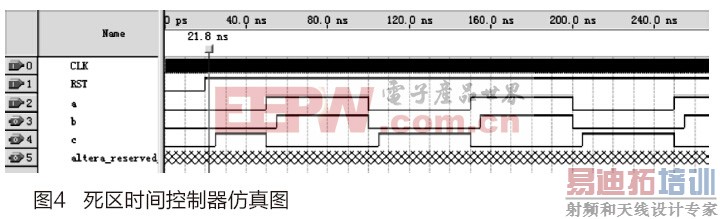

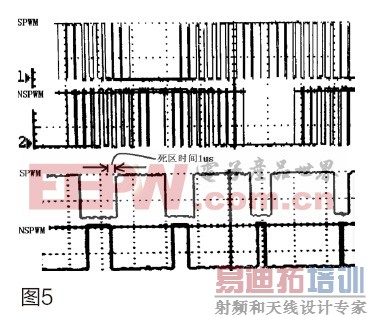

死区时间控制器的设计思想是当SPWM信号由高电平跳变为低电平时,NSPWM不是立刻由低变高,而是延时一段时间后再变为高电平。同理,SPWM信号由低变高时SPWM信号的输出也不能立刻输出,而是先让NSPWM由高变低,延时一小段时间后再让SPWM变为高电平。这一小段延时时间称为死区时间。死区时间的长短应根据开关管的开关速度来选择。本设计中设置死区时间为1uS。死区时间控制器模块在Quartus II 9.1环境的仿真如图4所示,其中a为输入的方波信号,b、c为输出反向带死区时间的控制信号输出。

6 测试

本设计使用了台湾友晶公司生产的FPGA实验板(型号为DE2-70)进行验证。实验表明该方法能够很方便地产生三相SPWM波形,并且载波与调制波信号均可任意调节。图5上部分为示波器测试其中1路的SPWM与NSPWM信号的示波器波形,下部分为示波器测量SPWM与NSPWM信号死区时间为1uS时的信号。

7 结束语

设计了一种基于数字系统的三相SPWM波形发生器的方法。结合DDS技术原理与VHDL语言可对SPWM的载波频率、调制波频率进行调节。并且设计了死区时间控制器,利用FPGA设计了死区时间可精确调节的SPWM信号发生器,解决了传统器件在设计SPWM信号发生器时对死区时间控制不精确、不稳定等问题,本设计在Quartus II 9.1环境进行了仿真,并最终下载到DE2-70实验平台进行了实验测试验证了该方法的可行性,并且该信号发生器输出SPWM波形稳定,可根据后级选用的开关管参数来精确调节输出信号的死区时间,可降低开关管的损耗。

参考文献:

[1] 王春侠,聂翔 . 基于面积等效法的SPWM 发生器的设计[J] . 微计算机信息, 2008(24) : 216-217

[2] 李晓宁 . 基于FPGA的SPWM波形控制器设计[J] . 实验技术与管理,2010(27) : 60-61

[3] 陈湘令,张莹.基于DSP变频器的SPWM控制算法[J].微计算机信息,2007,23:134-136

[4] [美]Ron Lenk著 王正仕等编译 实用开关电源设计[M].北京:人民邮电出版社,2006.4:15-20

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:高压浪涌抑制器取代笨重的无源组件

下一篇:高耗电移动设备的发展