- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

异步时钟切换电路

问题: 2个频率无关的时钟,在sel的选择下做切换。

有时一个看起来简单,实际上是在考验ASIC工程师的问题。

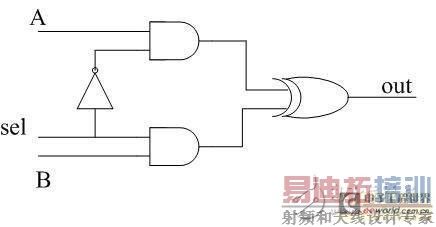

1.简单的讲就是做信号的2选1么,那么我们就先做一个简答的2选1吧。

这是一个逻辑图,实际的2选1是由3个门电路过程的,比如2个与一个或:

这个电路显然不能用于时钟的选择,因为这将导致输出时钟存在毛刺,后级电路是不能直接用的。

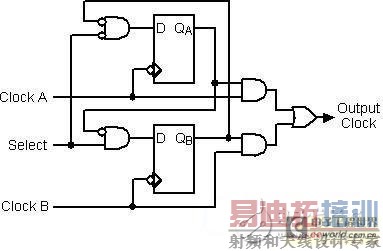

2. 我们很自然的会想到,要是能在时钟低时切换到另一个时钟低电平,就能保证时钟的品质。这样在时钟切换时就必然要经历4个阶段:1)选择信号改变、2)在clk1为低时停掉clk1的选择 、3)在clk2为低时打开clk2的选择端、3)正常工作,完成切换。

这样一想,似乎要写一个状态机了。但是这里面有一个问题先要解决:clk的低电平用什么来检测?当然,如果你有更高频率的时钟,确实是可以写一个状态机的,但是恐怕多数时候是没有那个高频时钟的。那我们就只能用时钟的下降沿来检测时钟的低电平的到来了。于是我们就基本有了方向。

这个电路是比较经典的,其思考过程也很屈折,关键就在于寄存器前的那个与门,它的位置非常关键。

是不是这就可以了呢?当然不完全。我们考虑了输出时钟的完整性,但是我们忘了,图上的这2个寄存器本身就是跨时钟域的寄存器,其本身也存在压稳态的问题。而且这个压稳态会随着输出的时钟扩展到很远。芯片恐怕是承受不了的。

3. 所以,我们还需要一点特殊处理(图就不画,有点烦,但是这一步很重要),就是在寄存器输出端到另一个寄存器前的与门之间用相应的时钟锁存2次(这是最通常的做法,地球人恐怕都知道)。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:LTM4612两相并联12V/10A设计

下一篇:两级共射极放大器组成的宽频放大器