- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

DDR3板子跑不了高频

颗DDR3(128*8);一个是两颗DDR3的(256*16)。两个案子DDR3的主频跑到336M左

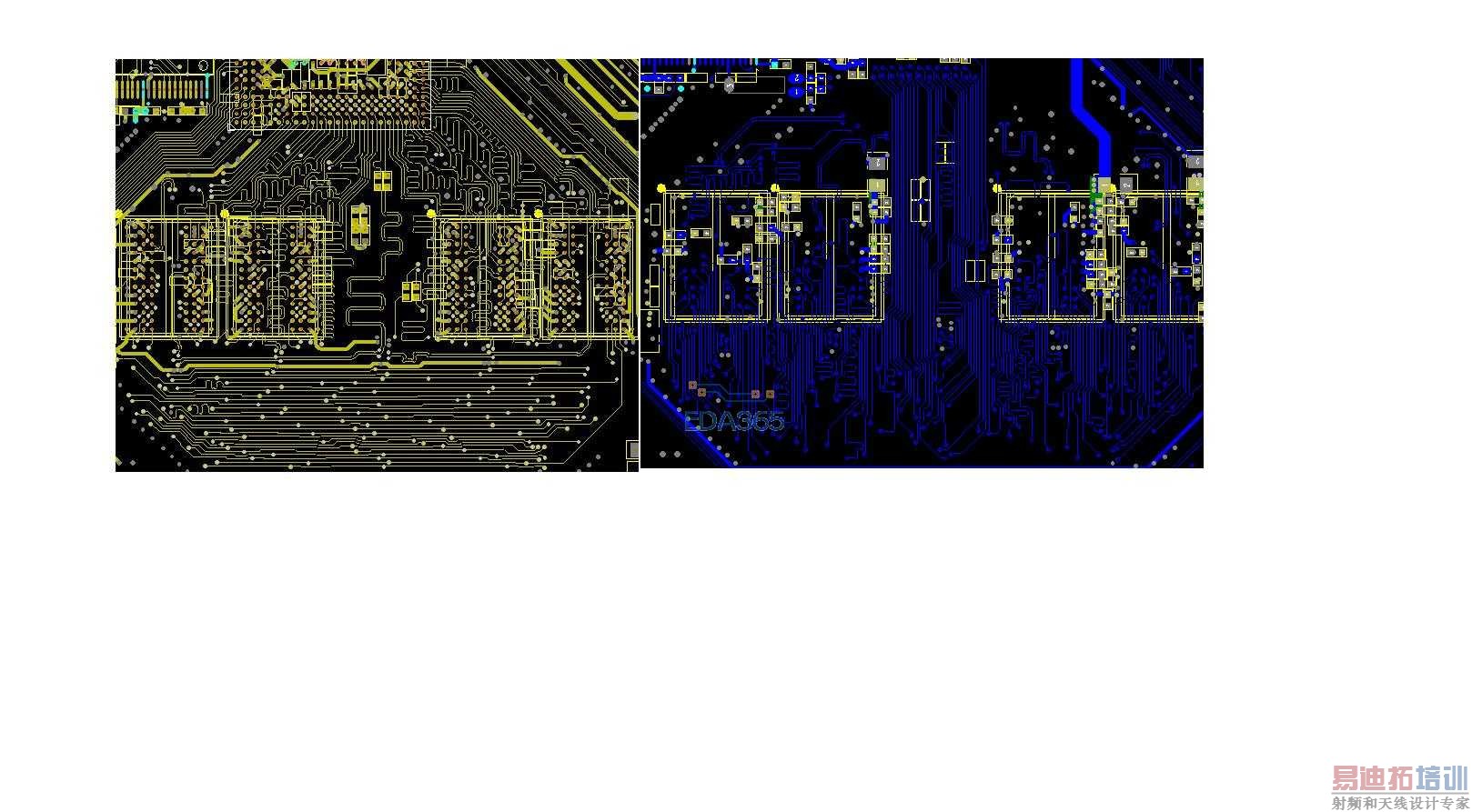

右就跑不上去了。板子的走线情况如下:

1、信号线有做等长控制(最长减去最短的):数据线公差1mil;地址、控制线

40mil

2、有做阻抗控制:数据线、地址线做50欧姆单端阻抗控制;差分线做100欧姆阻

抗控制

3、数据线线宽5mil,线距6mil以上;地址线线宽5mil,线宽5mil以上

4、两颗DDR3:数据线总线长838mil;地址线总线长1430mil。四颗DDR3:数据线

总长1100mil(将过孔等效线长计算在内),地址线总线长2500mil

5、走线在表层,第二层为完整的地,第三层为电源,第四层的DDR3走线参考第

三层的1.5V(DDR3供电电源),DDR3信号没有跨越电源分割平面。

请有经验的大侠分析一下这两块板子跑不上高频可能是哪方面的原因,也请分

享一下DDR3这一块走线的经验和方法,在此先谢谢各位了!

要了解DDR资料,按照要求做是不是有好些!

数据线有没有做到两组包地,有空间最好做到2W规则,两线间距是线宽的两倍,你走线5MIL,那间距最好做到10mi以上l,地和走线的间距最好是5MIL.这是我的经验之谈,供参考。

一根线上5个孔?

两颗DDR3的:数据线上一根线2个孔,地址线到每一个分支共有4个

四颗DDR3的:数据线上一根线2个孔,地址线到每一个分支共有4个

已经做到了2W原则

根本不可能的事 ! 呵呵要是真的那就奇怪了!

钢筋网

看得出来,这是一个layout高手的杰作,走线布局都和规范,提出的问题也很详细,也有比较全的图让人去分析。

我有过几个DDR2/3的设计,算是有点经验吧,谈一谈我的看法:

1. 关于时钟线,时钟线是最最重要的走线,你的T型走法显然不对,如果按你的走法,DRAM端应该终端有终结才行;(图太小,我只能看到2xDDR的那个)

2. 关于地址线,(以后再写)。

在JEDEC标准中DDR3的拓扑结构是fly-by,T型拓扑在amlogic的aml8726-m3中有用到,也是DDR3的,在这个方案中可以跑高频。在amlogic的方案中走线这些都没有做的很严格,但是效果反而比全志的好,具体效果应该跟主控有比较大的关系。菊花链拓扑应该比我现在用T型的拓扑要好的。我比较困惑的是两颗那块板,线长很短了,间距也不是很小的那种,数据线大概有7mil那样子,走蛇形线的时候,间距也是很大的,基本上都是30mil以上的,走线拐角处基本上都是用大圆弧。电源滤波方面也有考虑,不知道问题主要是出在哪一点上。

简单回一下,我这里太晚了.

你说的ddr时钟t型方案我没见过,如果有,应该是要做终端阻抗匹配。

应该说,如果你是layout工程师,你做的很不错了,调试分析是硬件工程师的事情;如果你是硬件设计工程师,那你在出错调试的时候,多用仪器分析信号的事情,而不仅仅把注意力放在layout上.

解决方案(仅建议):增加层数,把线都走在内层,且每跟线都要有地做为参考平面。地址线做成菊花链,末端加一个电阻。所有数据线的误差在10MIL的范围。

调整DDR_CLK差分线上的电阻为0R试验下?

哪里有等长,相差那么大!

ddr3应该使用菊花链,而且走线要满足3w,数据等长为10mil,地址和控制信号等长为25mil

没有找出原因之前,建议不要乱改设计。应该找个示波器看看,应该按顺序看下面的参数:时钟的眼图和抖动;地址控制线的时序,DQS/DQ的读和写的眼图和相对时钟的时序,主板应该跑到最大能过的时钟来测,一定可以看出问题。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:打不开文件

下一篇:pads layout中手动覆铜问题?