- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于LPC2294处理器的嵌入式PLC体系设计方案

1 嵌入式PLC的硬件结构设计

1.1 微控制器芯片的选取

CPU是PLC的核心,它能够识别用户按照特定的格式输入的各种指令,并按照指令的规定,根据当前的现场I/O信号的状态,发出相应的控制指令,完成预定的控制任务。本设计选用的是Philips公司生产的LPC2294微控制器。LPC2294是一款基于32位ARM7TDMI-S,并支持实时仿真和跟踪的CPU芯片,它带有256kB嵌入的高速Flash存储器,16kB 片内SRAM.LPC2294采用144脚封装、具有极低的功耗以及多达112个通用I/O 口,9个边沿或电平触发的外部中断引脚,最大为60MHz的工作晶振,多个32位定时器,PWM 单元,实时时钟和看门狗,转换时间低至2.44μs的8通道10位ADC、4 路高级CAN 接口, 另外具有2 路UART(16C550),高速I2 C (400kbit/s)及2路SPI总线。LPC2294丰富的硬件资源和完善的功能使这款微控制器特别适用于汽车、工业控制应用以及医疗系统和容错维护总线等场合。

1.2 硬件系统的整体结构

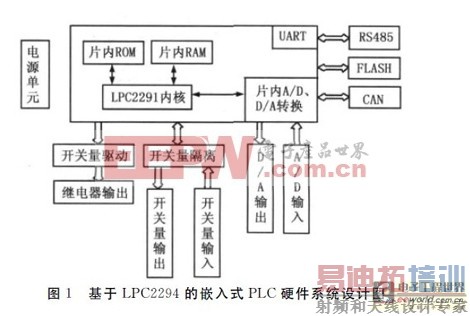

本系统以ARM 芯片LPC2294为CPU,设计为14路PNP型输入、10路继电器输出的基本模式。硬件总体结构包括:

电源及复位模块、ARM 微控制器、Flash存储器扩展模块、开关量输入输出模块、模拟量输入输出模块、RS485接口及CAN接口通信模块等。系统的结构如图1所示。

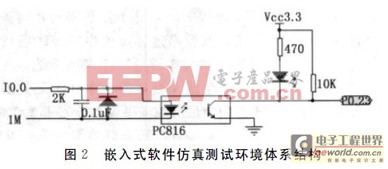

1.2.1 开关量输入输出接口电路

图2所示为一路开关量输入图。此部分电路前端为R、C组成的一阶滤波电路,防止外部干扰信号进入系统中。输入端外接的输入控制开关信号(直流24V)通过输入点10.0经限流电阻输入到光电耦合器(PC816)的输入端,M 为输入点10.0~10.7的公共输入端。因P0.23口被设置为输入模式且口线内部无上拉电阻,所以需要外接上拉电阻,防止口线悬空。当10.0输入端为24V时,光电耦合器中的光敏二极管导通,光敏晶体管输出端被拉为低电平,指示该路输入状态的LED被点亮,P0.23被置为低电平。当CPU访问该路信号时,将该输入点对应的输入过程映像寄存器的值置为 1.10.0输入端为0V时,P0.23为高电平,当CPU访问该路信号时,则将该输入点对应的输入过程映像寄存器的值置为0.其余各个输入点所对应的电路及工作原理均相同。

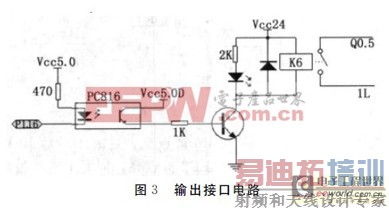

图3所示为继电器输出模块图,图中并联在继电器线圈两端的二极管这里起续流作用。该模块的工作原理如下:当内部输出过程映像寄存器为时,LPC2294端口P1.16输出0,光敏晶体管导通,继电器线圈得电,输出点接通;反之当内部输出过程映像寄存器为0时,端口P1.16输出1,继电器线圈失电,输出点断开。

图3所示为继电器输出模块图,图中并联在继电器线圈两端的二极管这里起续流作用。该模块的工作原理如下:当内部输出过程映像寄存器为时,LPC2294端口P1.16输出0,光敏晶体管导通,继电器线圈得电,输出点接通;反之当内部输出过程映像寄存器为0时,端口P1.16输出1,继电器线圈失电,输出点断开。

需要注意的是,当LPC2294的GPIO 口初上电时,其输出端口(如本图中的P1.16)的电压不稳定,这样易导致外部继电器误动作而引起外部设备工作不稳定。为此,我们设计了图4电路用来提高继电器输出的稳定性。

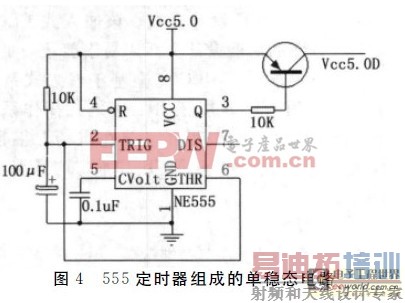

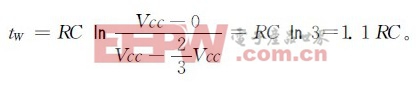

这是一个由NE555 定时器组成的单稳态电路,其中VCC5.0D端接图3中光电耦合器的集电极。其工作原理为:系统上电初始,2、6管脚电平不能突变,保持为低电平。分析 NE555的内部电路可知,此时输出端3管脚输出高电平,电路开始对R、C电路进行充电,随着时间的推移,管脚2、6的电平不断升高,当升至23VCC 时,输出端3管脚将翻转至低电平,使三极管导通,VCC5.0D输出5V。这样,系统上电后经过一段时间,I/O口的电平稳定下来之后,光电耦合器才得电开始工作。暂稳态的持续时间tW取决于外接电阻R 和电容C的大小。tW等于电容电压在充电过程中从0上升到23VCC所需要的时间,即:

1.2.2 模拟量输入电路设计

1.2.2 模拟量输入电路设计

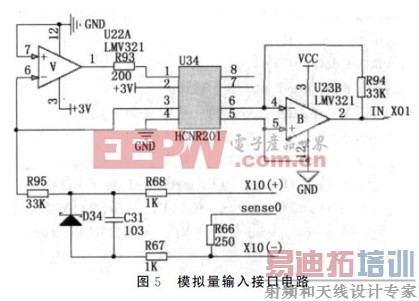

先通过电阻R66,将现场传感器输出的电流信号转换为0~5V电压信号进行采集。考虑到抗干扰及对微处理器电路的保护,在转换电路的输出端加了线性光耦HCNR201.硬件电路如图5所示。

1.2.3 串行通讯接口电路设计

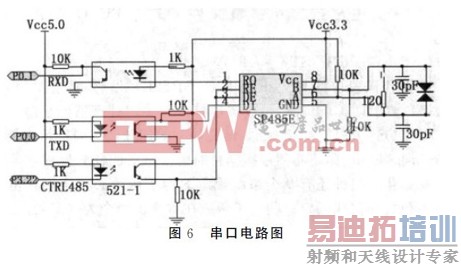

为了能与其它工业控制产品兼容,我们设计时采用了RS-485接口标准。为了将TTL电平转换成 RS485电平,选用了SP485E 收发器。SP485E 芯片的数据传输速率可高达10Mbps,其最大的特点是在为发送器输出和接收器输入管脚提供了ESD保护电路。接口电路如图6所示。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于VB6.0的MSP430单片机与PC机串口通信设计

下一篇:实现单片机和FPGA的位移装置高精度测量实用方案