- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

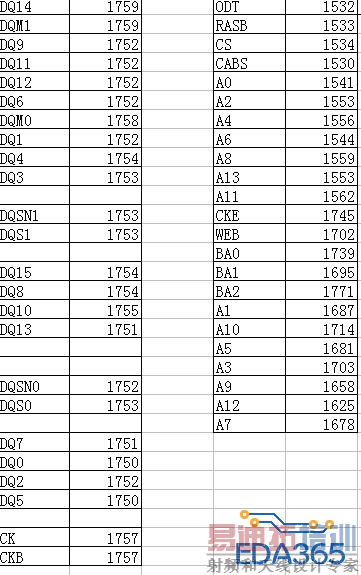

DDR数据

录入:edatop.com 点击:

感谢楼上几位的回复,lisa说的也是,不能因为别人的PCB走线误差大能跑起来,就觉得自己这样走也OK,现在正在想办法更改下,争取误差控制在+-100MIL之间,同组信号误差控制在+-5MIL之间

请兄弟们帮忙查看附图,数据走线长度是否有什么问题?

是DDR2芯片,由于板子面积问题,地址线误差较大,这样有没有影响?

个人认为,没啥大影响,

谢谢楼上,请大家多帮忙评评

要看是DDR1还是DDR2,3吧,一般的DDR1可以做+-100mil的地址误差,2 3 就不推荐做这么大的

现在是DDR2芯片,请高手们帮看看啊

我几个月前画的一块板子用的是DDR3内存,用了四片内存,总容量为1GB,由于内存摆放位置比较靠近CPU,所以当时地址线长度比较短,在650左右,所有数据线长度都在640到650之间,长度控制得比较狠,目前我们的板子测试得到最高位460Mhz,而我们需求的是400Mhz,余量还是比较大的,但是感觉还是没有想象中的高

那还照楼主的经验,我这个数据会不会有什么影响,因为板子面积问题,地址线拉出来直走就那么长了,因为现在地址线与数据线相差还是有些大的,但看到有的板子,批量过的,也是DDR2,误会差有的达到了700MIL,也没发现有什么问题,困惑中。

兄弟们发表一下意见啊

个人认为,做技术不能存在侥幸心理,不能因为别人的PCB走线误差大能跑起来,就觉得自己这样走也OK,严格按照LAYOUT GUIDE来布线还是很有必要的,不怕一万,就怕万一

控制的真够很的,发张照片看看,拜读一下!

DDR2的最大工作频率是533MHz,也就是说周期是不到2ns。所以差200mil应该是没有问题的。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

射频和天线工程师培训课程详情>>