- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

OTN帧头定位电路优化研究

引言

在ITU-T G.709协议中,ITU-T规定了OTN的网络帧结构。OTN使用了和SDH类似的帧结构,帧定位信号(Frame Alignment Signal)也是相同的。但是由于OTN的信号速率非常高,如OTU2的速率达到10Gbps以上,OTU3速率达到43Gbps以上,不能直接使用SDH的帧定位电路。以OTU2为例,在Serdes将串行信号变为并行信号后,如果还按照8bit的数据宽度,则信号速率需要达到1.25Gbps左右,这无论对于FPGA处理还是ASIC,速率都是过高而不能处理的,所以需要将数据宽度进一步加大,以降低信号速率。在本项目中,使用了64位的数据宽度,这时的信号速率为167Mbps。对于这样高速而且宽位数的数据处理,如果还按照传统的帧头定位电路来处理,电路的速度上不去,会导致电路处理不能达到要求,所以需要简化帧头定位电路,以达到高速率、高位宽的信号处理要求。

传统的帧定位处理方法

OTN帧结构

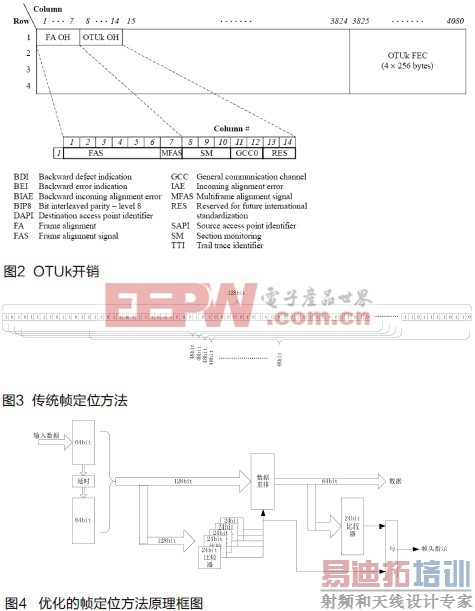

在ITU-T的G.709协议中,ITU-T规定了OTN的帧结构,如图1所示。

OTUk帧结构是4行,4080列的结构。在每一帧的开始处,首先是帧定位信号(FAS),然后是复帧定位信号(MFAS)和其它开销字节。详细如图2所示。

在OTUk帧数据中,FAS信号是不经过扰码的,除FAS信号外的信号,都是经过扰码的。所以只要在整个数据中,只要找到了FAS(即0xF6F6F6282828)信号,就将整个帧头找到了,整个帧的结构就随之确定了。

[p]OTUk帧结构是以字节为定位基准的。但是在Serdes将串行数据转换为64bit并行数据后,只是将64个bit随机的放在一起,并不是按字节对齐的,所以在Serdes电路后边,紧跟着的是一个将64bit随机排列的数据按字节对齐的方式重新处理的电路。

传统的帧定位方法

在Serdes后边的并行数据侧,48bit的FAS信号,可能处于一个时钟周期的64个bit内,也可能处于两个连续的64个bit数据中,所以需要在连续的两个64个bit内,查找FAS信号。然后在这128个bit内,使用64个48bit的比较器来和FAS信号进行比较。如图3所示。

在电路处理时,首先把第一个时钟周期的64bit数据缓存,再与下一个周期的64bit组合成为图3中的128bit数据。在此128bit数据中,需要64个48bit的比较器,第一个比较器比较第1bit到第48bit的数据是否和FAS相同,第二个比较器比较第2bit到第49bit的数据是否和FAS相同,依此类推,第64个比较器比较第64bit到第112bit的数据是否和FAS相同。在下一个时钟周期时,上述128bit的第65到128bit移动到图3的第1到第64bit,重复上述过程。

在上述比较过程中,当某个比较器的输入数据和FAS相同时,给出指示信号。后续电路以输出指示信号的比较器的第一个bit,作为整个输出64bit的第1个bit,将上述输入的128bit数据重新排列,送往下级电路。到此,整个帧定位电路的工作完成了。

从上述描述中,可以看到,传统的帧定位电路,需要64个48bit的比较器同时工作,电路的规模大,功耗大。所以,需要对上述传统帧定位电路进行优化,以降低电路规模,减小电路功耗,提高电路工作速率。

优化的帧定位方法

寻找FAS的过程,其实就是在并行的128bit数据中寻找0xF6F6F6282828的过程,对帧定位过程进行优化,可以考虑对48位的比较器进行优化。

本文提出了一种优化的帧定位处理方法,原理框图如图4所示。

首先,输入进来的64bit先延时一拍,再和下一周期来的数据组合起来,成为128bit数据。在此128bit数据中,使用64个24位比较器,每个比较器和0xF6F6F6进行比较。第1个比较器接128bit数据的第1到第24位,第2个比较器接第2位到第25位……,第64个比较器接第64位到87位。当其中任何一个比较器找到0xF6F6F6时,给出指示信号,后边的数据重排电路,根据给出指示信号的比较器的位置,对数据进行重新排列,将此比较器输入的第1bit作为整个输出数据的第1bit,依次排列64bit数据进行输出。

在数据重排电路输出的64bit数据后,需要再连接一个24bit的比较器,这个比较器,对重新排列后的数据的第25到48bit进行比较,看数据是否为0x282828。当前面的比较器和后一个比较器同时给出指示信号时,即表示同时找到了0xF6F6F6和0x282828,并且这两个数据是相连接的。即找出了FAS信号,此时给出帧头指示信号。

仿真验证

对以上描述的过程使用Modelsim进行仿真,仿真图如图5所示。

从图5可以看出,在输入数据DataIn中含有FAS信号时,24bit比较器给出了指示信号SelBus,SelBus由原来的全0变化为其中一个bit变为1,此时数据重排电路已开始工作,将输出的数据按SelBus指示信号进行输出重排,并且在重排后,对数据排列的顺序进行锁定。在下一个时钟周期中,后续的比较器对重排的数据的第25bit开始进行比较,比较正确后,输出了FAS指示信号

结束语

随着通信技术的发展,数据传输的速率越来越高,电路规模越来越大。而大规模的电路要同时进行高速运行时,无论对于FPGA还是ASIC,都是巨大的挑战,有时甚至不能成功,所以就需要对电路的规模进行优化以降低电路规模。本文提出的帧定位电路,对原有的帧定位电路有很大的优化。

参考文献:

[1] ITU-T. G.709/Y.1331. Interfaces for the Optical Transport Network[S].2012

[2] 吕瑾,徐东明,张云军.SDH传输系统中帧定位电路设计[J].中国集成电路,2010,(10)

[3] 孟李林.用流水线技术实现STM-16帧定位电路设计[J].光通信研究,2008,(1)

[4] 孟李林,蒋林等.SDH帧头检测及数据重排电路[P].2005

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...