- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

PADS LOGIC与LAYOUT同步的问题

录入:edatop.com 点击:

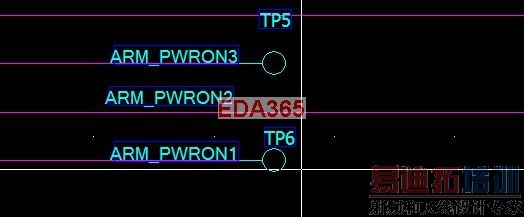

在做pads LOGIC与LAYOUT同步的时候,发现会将原来pcb中的过孔测试点及同这个测试点连接的网络全部删除,不知道是为什么,我检查了,发现网络是一样的。

我将过孔设成锁定,同步时,还是会删除,郁闷!

问题还没有解决,帖子沉得太快了。

你确认下你那个过孔测试点是不是作为元件加进PCB的,而 Logic中未添加。

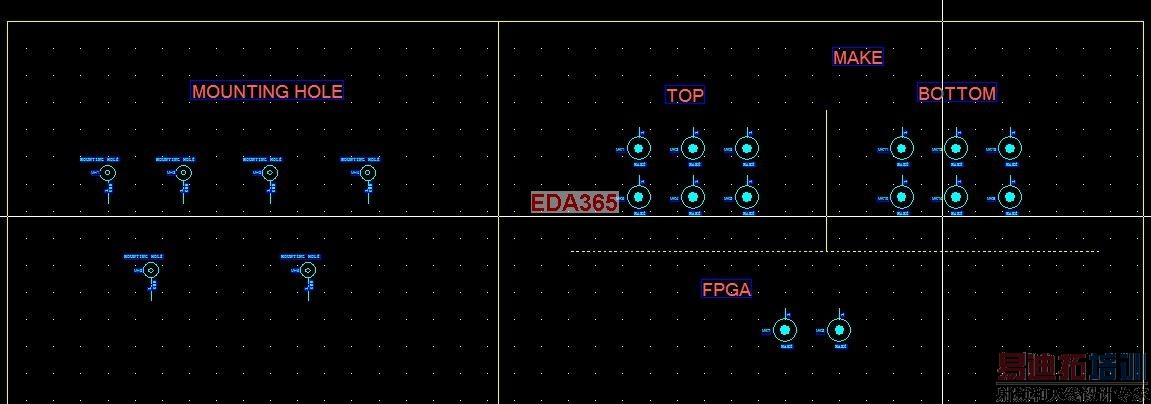

测试点,定位孔,make点,都作出元件,加入原理图,一劳永逸!直观也方便检查

此问题同如下帖子应该是一个原因

就是在同步时,或者在ECO下删除元件,和元件相连的线及线上的过孔一起都删除了,但我检查网络名称是一样的,不知道如何解决,请高人指点。

难道都没有遇到过?

同意4楼跟5楼,把测试点做成原件加到原理图中,然后导进PCB就不会丢了

测试点补起了,连测试点的线业不丢了,但不是测试点的线还是丢,难道我得把每条线都加一个测试点。

把测试点作为元件加在原理图中就OK了

改成元件估计就不会掉了

收藏一下

没看明白

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:核心板的接口未做封装,网络表导入pads后无连线,该怎么处理?

下一篇:关于pads使用过程中遇到的小问题,不知道是操作问题还是安装问题///

射频和天线工程师培训课程详情>>