- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

浅析AD9522时钟分频电路原理

在集成度高度发展的今天,不能靠多个晶振源来解决问题,而且一旦晶振固定那么它的灵活性和可移植性必然受到很大影响,所以一些时钟分频芯片应运而生,今天我们将举一个很有代表性的AD9522时钟分频芯片的典型应用来达到一个抛砖引玉的作用。

一、AD9522简介

1.外部特性

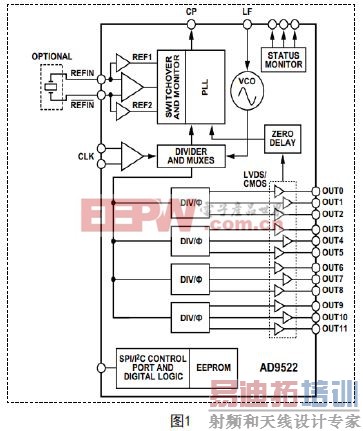

A D 9 5 2 2是一个多路时钟输出和分配功能的芯片,本身支持亚皮秒抖动性能,在芯片内部还集成了PLL(PhaseLockedLoop)和VCO(压控振荡器)。VCO的调谐范围是 2.02GHz~2.335 GHz.AD9522串行接口支持SPI与I2C的数据总线,芯片内部的EEPROM可通过串口进行编程,可以用来存储用户配置的寄存器数据从而使输入时钟分频。AD9522具有12路的LVDS电平输出,可以分成4组,每组输出都有分频器,分频比1-32之间可以在其范围内随意设置。如图1所示。

2.内部特性

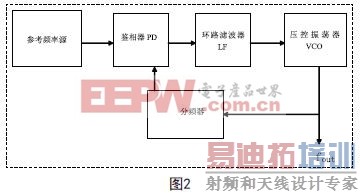

AD9522外部的输入时钟是晶振供给的,内部时钟的倍频和分频都是由锁相环PLL和压控振荡器VCO控制的。例如压控振荡器给出一个信号,一部分作为输出,另一部分通过分频与PLL产生的本振信号作相位比较,为了保持频率不变,就要求相位差不发生改变,如果有相位差的变化,则PLL的电压输出端的电压发生变化,去控制VCO,直到相位差恢复,达到锁频的目的。如图2.

二、单片机配置

1.寄存器配置

我们提到了AD9522可以配置SPI与I2C的数据总线来达到分频的目的,那么配置数据总线就可以用单片机来配置了。我们选用C8051F320作为配置AD9522的内部寄存器,原因是单片机编程比较直观也比较容易。如图3.

写完成后设置断点观测写入和读取值是否相同,验证好读取没有问题后开始配置寄存器。配置的时候要注意的是0×18地址寄存器配置锁定检测周期数选择大一些,有可能一些设置参数或者环路滤波带宽设置导致锁定时间比较长,导致读取0 x 1 F地址时锁定状态不是最终状态,现在设置该寄存器为0×66,将检测周期数设置为最大值255.

VCO校验需要先设置0×180>为0然后更新,再设置0×180>为1再次更新。等待校验完成读取0x1F地址数据。0x1D7>需要设置为0,S t a t u s引脚显示状态才为0 x 1 7地址配置状态。否则引出的时钟观测不到。配置完成后读取0x1f地址状态,配置完成后需要等待一定时间再读取0x1f地址数据,因为vco校验需要一定时间,读取太快会导致读取状态不正确。

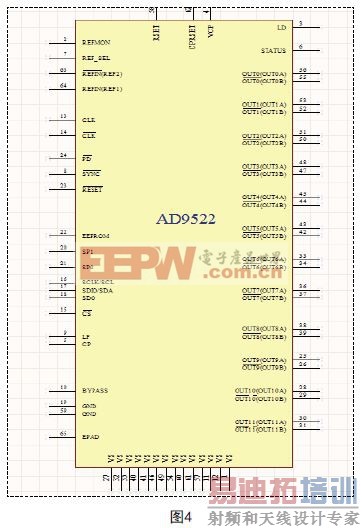

如图4所示,在引脚上下拉方面VCP需要上拉,PD,SYNC,RESET需要上拉,使这些引脚无效。EEPROM使内部寄存器数值不从EPROM加载。SP1,SP0需下拉,将内部寄存器数据加载配置模式设置为I2C加载。CS下拉使数据片选信号一直有效。REF_SEL下拉选择输入参考时钟为refrence1.

[p]

[p]

2.程序设计

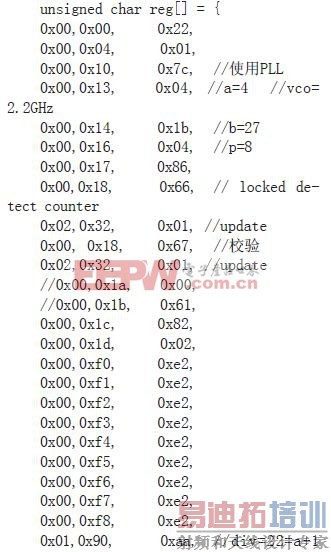

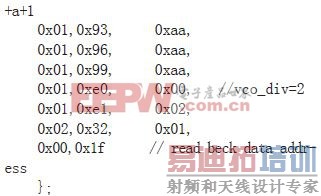

单片机源程序寄存器配置部分主要配置a,b,p,div和vco div的值,那么我们就可以根据公式fvco=ref*(a+b*p)决定fvco的值,然后根据我们的分频公式fout=fvco/vco div/div就可以得到我们需要的时钟频率。寄存器配置部分程序如下:

三、环路滤波设计

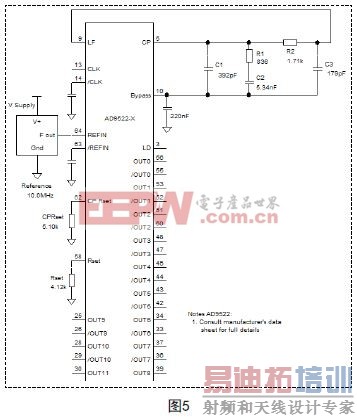

那么我们不得不提到的是AD9522的环路滤波参数的设置必须和上面的寄存器配置要一致,这样我们才能锁定频率,使得我们分频出来的时钟频率稳定而且是我们需要的时钟频率。设置环路滤波可以用ADIsimCLK软件来处理。如图5.

四、结束语

经过上面的讨论我们可以得出AD9522是一个很好用的分频的芯片,它可以根据我们给的输入时钟,由内部锁频、倍频、分频来得到12路我们需要的时钟频率,可以说极大的方便了设计,它可以提供更多的时钟源供我们后续设计中使用,它的寄存器的配置是我们借鉴和学习的地方。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...