- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

由开关电源驱动的高速ADC设计

系统设计人员正面临越来越多的挑战,他们必须在不降低系统元件(如高速资料转换器)性能的情况下让设计最大程度地实现节能。设计人员们可能转而採用许多以电池供电的应用(如某种手持终端、软体无线设备或可携式超音波扫描器),也可能缩小产品的外形尺寸,因而必须寻求减少发热的诸多方法。

极大降低系统功耗的一种方法是对高速资料转换器的电源进行最佳化。资料转换器设计和製程技术的一些最新进展,让许多新型ADC可直接由开关电源来驱动,因而达到最大化功效的目的。

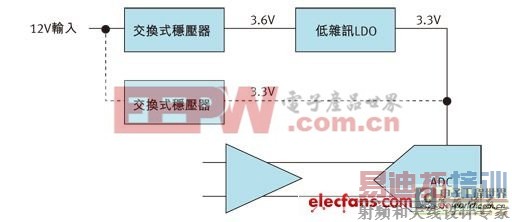

系统设计人员们习惯在交换式稳压器和ADC之间使用一些低杂讯、低压降稳压器(LDO),以清除输出杂讯和开关频率突波(请参见图1)。但是,这种乾净的电源设计代价是高功耗,因为LDO要求压降余量来维持正常的执行。最低压降一般为200到500mV,但在一些系统中则可高达1到2V(例如,ADC的3.3V电压轨产生自一个使用LDO的5V开关电源时)。

图1:从传统电源转到最大功效电源。

就一个要求3.3V电压轨的资料转换器而言,300mV的LDO压降增加约10%的ADC功耗。这种效应在资料转换器中更加显着,因为它具有更小的製程节点和更低的电源电压。例如,1.8V时,相同300mV压降增加约17%(300mV/1.8V)的ADC功耗。因此,将该链路的低杂讯LDO去除可产生巨大的节能效果。去除LDO还可以降低设计板级空间、热量以及成本。

本文阐述包括超高性能16位元ADC在内的一些TI高速ADC可在ADC性能无明显降低的条件下直接透过交换式稳压器驱动。为了阐述的方便,我们对两款不同的资料转换器(一款使用高性能BiCOM技术(ADS5483),另一款使用低功耗CMOS技术(ADS6148),以进行开关电源杂讯的感应性研究。本文的其他部份对所得结果分别进行介绍。

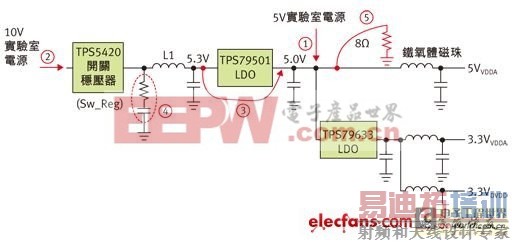

採用BiCOM技术的ADC

这种製程技术实现宽输入频率範围下的高讯号杂讯比(SNR)和高无突波动态範围(SFDR)。BiCOM转换器一般还具有许多晶片去耦电容器和非常不错的电源抑制比(PSRR)。我们对ADS5483评估板(ADS5483EVM)进行了电源研究,其具有一个使用TPS5420交换式稳压器(Sw_Reg)的板上电源;一个低杂讯LDO(TPS79501);以及一个外部实验室电源使用选项。我们使用图2所示不同结构实施了5次实验,旨在确定ADS5483透过一个交换式稳压器直接执行时出现的性能降低情况。由于ADS5483类比5V电源到目前为止表现出对电源杂讯的最大感应性,因此该研究忽略了3.3V电源的杂讯。ADS5483产品说明书中列出的PSRR支援这种情况:两个3.3V电源的PSRR至少高出5V类比电源20dB。

图 2:使用ADS5483EVM的5次实验电源结构。

5次实验的结构变化配置如下:

实验 1:

一个5V实验室电源直接连接到5-V类比输入,同时绕过交换式稳压器(TPS5420)和低杂讯LDO(TPS79501)。使用一个板上LDO(TPS79633)产生ADS5483低感应度3.3V类比及数位电源的3.3V电压轨。

实验2

将一个10V实验室电源连接到TPS5420降压稳压器,其使用一个5.3V输出。这样可为TPS79501提供一个300mV 压降,因而产生一个5V电压轨。

实验3

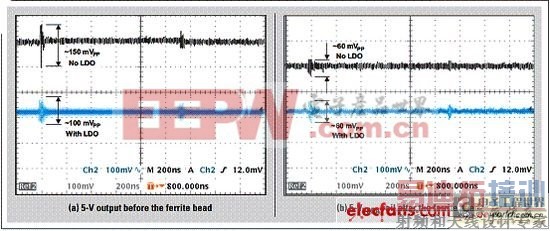

使用TPS5420,从10V实验室电源产生一个5V电压轨。本实验中,我们绕过了TPS79501低杂讯LDO。图3a显示,如‘实验2’连接的LDO较好地减少了交换式稳压器的5.3V输出峰值电压。但是,图3b显示5VVDDA电压轨铁氧体磁珠之后输出没有巨大的差异。

图3:实验2(使用LDO)和实验3(无LDO)的示波器截图对比。

实验 4

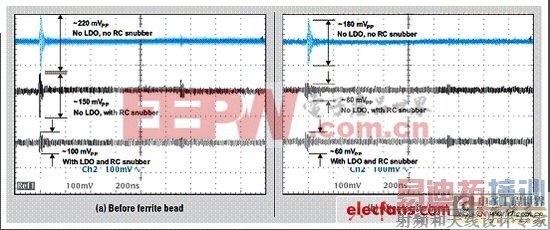

本实验配置方法与‘实验3’相同,但去除了TPS5420输出的RC缓衝器电路,其会引起高振铃和大开关频率突波。

我们可在图4中清楚的观察到RC缓衝器电路的影响。去除LDO并没有在铁氧体磁珠之后表现出明显的差异,而去除RC缓衝器电路则会导致更大的清洁5VVDDA 电压轨电压峰值进入ADC。我们将在稍后详细研究RC缓衝器电路的影响。

图4:5VVDDA电压轨的电源杂讯。

实验 5

将一个8Ω功率电阻连接到5V电源,类比如现场可程式设计闸阵列(FPGA)等额外负载。TPS5420必须提供更高的输出电流,并更努力地驱动其内部开关,因而产生更大的输出突波。通过重复进行‘实验2’、‘实验3’和‘实验4’可以测试这种配置。 测量结果

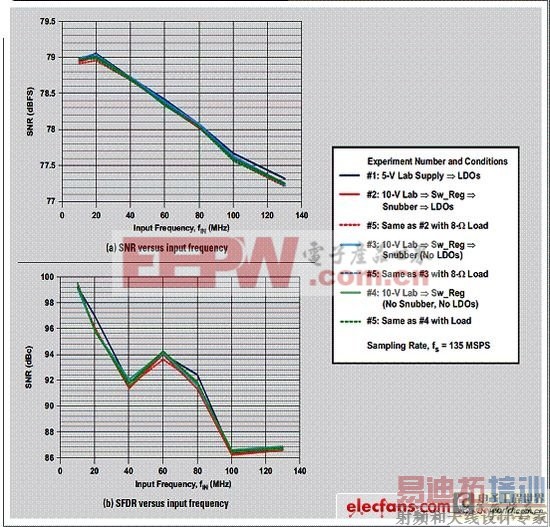

我们利用输入讯号频率扫描对比了5个实验。先使用135MSPS採样速率然后使用80MSPS採样速率对叁个ADS5483EVM实施了这种实验,均没有观察到巨大的性能差异。

在使用135MSPS採样速率情况下,SNR和SFDR的频率扫描如图5所示。在10到130MHz输入频率下SNR的最大变化约为0.1dB。SFDR结果也非常接近;在某些输入频率(例如:80MHz)下,可以观测到下降1至2dB。

图5;10到130MHz输入频率扫描。

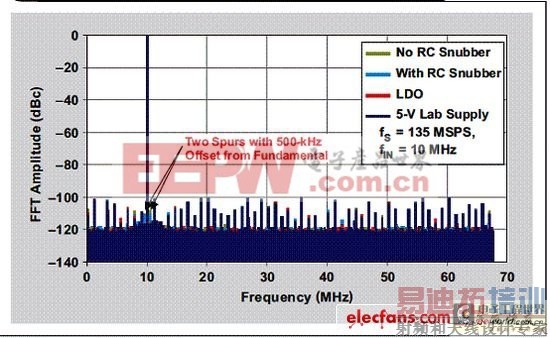

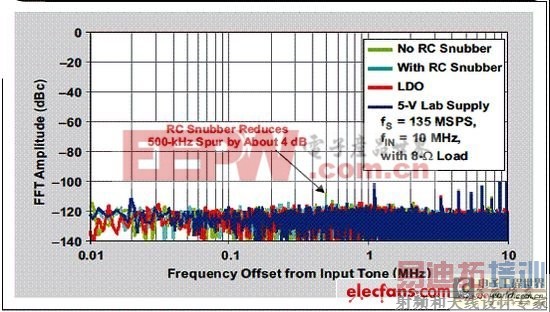

5个实验的FFT曲线图对比(请参见 [p] 图6)显示杂讯底限或突波振幅没有出现较大的增加。使用LDO清除开关杂讯使得输出频谱看起来几乎与乾净5V实验室电源完全一样。去除LDO以后,我们观测到从交换式稳压器产生了两个突波,其具有一个来自10MHz输入音调的约500kHz频率偏置。RC缓衝器电路降低这些突波振幅约3dB,从约-108dBc降到了约-111dBc。这一值低于ADS5483的平均突波振幅,其显示ADS5483可在不牺牲SNR或SFDR性能的情况下直接由一个交换式稳压器来驱动。

图6:500kHz偏置突波65k点FFT图。

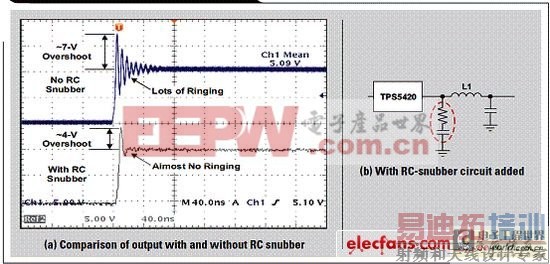

RC缓冲器

降压稳压器输出能够以相当高的开关速度对非常大的电压实施开关作业。本文中,将TPS5420的输入电压轨设定为10V,我们可在输出端观测到许多过衝和振铃,如图7a所示。为了吸收一些电源电路电抗能量,我们将RC缓衝电路添加到了TPS5420的输出(请参见图7b)。该电路提供了一个高频接地通路,其对过衝起到了一些阻滞作用。图7a显示RC缓衝器降低过衝约50%,并且几乎完全消除了振铃。我选用了R=2.2Ω和C=470pF的元件值。稳压器的开关频率範围可以为500kHz到约6MHz,具体取决于製造厂商,因此可能需要我们对R和C值进行调节。这种解决方案的代价是带来一些额外的分流电阻AC功耗(儘管电阻非常小),其降低稳压器总功效不足1%。

图7:TPS5420交换式稳压器。

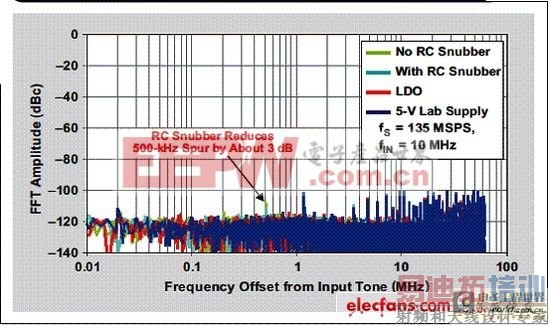

我们将10MHz输入讯号标準化FFT图绘製出来,以对比‘实验1’到‘实验4’(请参见图8)。TPS5420的突波在约500kHz偏置时清晰可见。缓衝器降低突波振幅约3dB,而低杂讯LDO则完全消除了突波。需要注意的是,RC缓衝器(无LDO)的突波振幅约为-112dBc,远低于ADS5483平均突波振幅,因此SFDR性能并未降低。

图8:‘实验1’到‘实验4’的标準FFT图。

在‘实验 5‘中,我们将一个8Ω功率电阻添加到5-VVDDA电压轨,旨在模拟电源的重负载。标準化FFT图(请参见图9)并未显示出很多不同。去除RC缓衝器以后,突波增加约4.5dB;其仍然远低于平均突波振幅。

图9:添加 8Ω负载的标準化FFT图。 采用CMOS技术的ADC

当关注如何在保持较佳的SNR和SFDR性能的同时也尽可能地降低功耗时,我们一般利用CMOS技术来开发高速资料转换器。但是,CMOS转换器的PSRR一般并不如BiCOM ADC的好。ADS6148产品说明书列出了25dB的PSRR,而在类比输入电源轨上ADS5483的PSRR则为60dB。

ADS6148EVM使用一种板上电源,其由一个交换式稳压器(TPS5420)和一个低杂讯、5V输出LDO(TPS79501)组成,后面是一些3.3V和1.8V电源轨的低杂讯LDO(请参见图10)。与使用ADS5483EVM的5个实验类似,我们使用ADS6148EVM进行了下面另外5个实验,其注意力只集中在3.3VVDDA电压轨的杂讯上面。1.8VDVDD电压轨外置TPS5420实验显示对SNR和SFDR性能没有什么大的影响。

图10:使用ADS6148EVM的5个实验电源结构。

实验6

将一个5V实验室电源连接到两个低杂讯LDO(一个使用3.3V输出,另一个使用1.8V输出)的输入。LDO并未对实验室电源带来任何有影响的杂讯。

实验7

将一个10V实验室电源连接到TPS5420降压稳压器,其与一个5.3V输出连接,像‘实验2’连接ADS5483一样。TPS79501产生了一个过滤后的5.0V电压轨,对于3.3V输出和1.8V输出LDO提供输入,如图10所示。

实验8

所有3.3VVDDA电压轨LDO均被加以旁路。TPS5420配置为一个3.3V输出,该输出直接连接到3.3VVDDA电压轨。TPS79601产生1.8VDVDD电压轨,并透过一个外部5V实验室电源供电。

实验9

该实验配置方法与‘实验8’相同,但去除了TPS5420输出的RC缓衝器电路。

实验10

一个4Ω功率电阻连接到TPS5420的3.3V输出。这样做可大幅增加TPS5420的输出电流,因而类比一个附加负载。另外,像‘实验5’的ADS5483一样,它带来了更高的开关突波和更多的振铃。

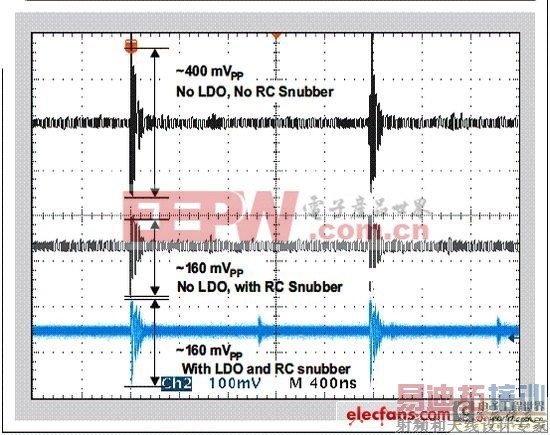

图11显示了‘实验7’、‘实验8’和‘实验9’产生的一些3.3VVDDA 输出波形。有或无LDO的峰值电压振幅存在一些差异,但RC缓衝器可降低60%的峰值杂讯。

图11:铁氧体磁珠后测得3.3VVDDA 电压轨实验示波器截图对比。

测量结果

利用输入讯号频率扫描,透过比较‘实验6’到‘实验10’,我们可以研究ADS6148对电源杂讯的感应性。先使用135MSPS然后使用210MSPS的採样速率(fs)对叁个ADS6148EVM进行数次实验。我们并未探测到较大的性能差异。

使用135MSPS採样速率,SNR和SFDR的频率扫描如图12所示。高达300MHz输入频率下SNR的最大变化为0.1到0.2dB。但是,一旦移除了RC缓衝器电路,杂讯便极大增加,因而降低SNR约0.5到1dB。

图12b显示了5次ADS6148实验输入频率的SFDR变化。我们并未观测到较大的性能降低。

图12:10到300MHz的输入频率扫描。

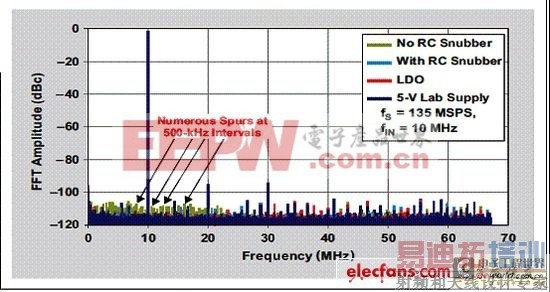

比较图13所示FFT图,我们知道无RC缓衝器SNR稍微减少的塬因。去除RC缓衝器电路后,在ADS6148输出能谱中,我们可看到分佈间隔约为500kHz(TPS5420开关频率)的众多小突波,如图13所示。相较于ADS5483,这些小突波更具主导性,并且因为ADS6148的固有低PSRR SNR大幅降低。但是,图13所示FFT图还显示添加的RC缓衝器电路较好地弥补了这一不足。

图13:大批突波的65k点FFT图。

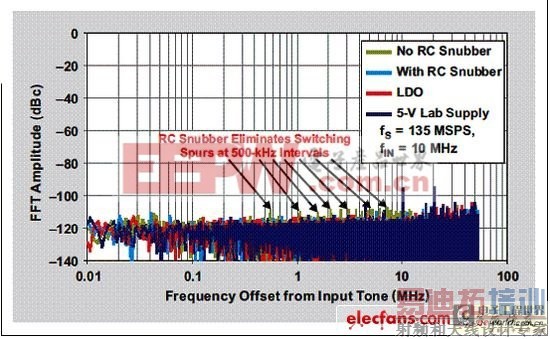

图14所示标準化FFT图显示交换式稳压器的突波高出ADC平均杂讯层约5到6dB。其非常低,以至于其对SFDR减少无法产生影响,但却明显地影响了ADC的SNR。

图14:标準化FFT图显示使用RC缓衝器的好处。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...