- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

具有自适应开机和冬眠功能的电源管理设计

摘要:消费类电子产品主控SoC芯片内电源管理部分的设计对产品整机的功耗控制至关重要。为降低产品功耗和节省成本,设计了与任意片外开机使能电平相匹配的自适应开机接口使电子产品的开关机电路得到简化;并通过软硬件协作实现了冬眠功能,其特点是在待机状态下,SoC上除电源管理单元和实时时钟外全部关电,而后能响应用户请求迅速恢复系统运行。

关键词:SoC芯片;电源管理;“自适应”开机;“冬眠”功能

0 引言

随着科技的进步,手机,MP3/MP4,PDA等消费类电子产品的智能化程度越来越高,功耗越来越低而价格越来越便宜。与此趋势相应的就是此类产品的电源管理方案更加复杂和灵活。

以手机为例,起初手机的电源管理只包括简单的电源开通/关闭功能,由系统级印刷电路板(以下简称PCB)上独立于主控芯片(以下简称SoC)之外的控制电路和电源管理芯片(PMIC)实现,其中PMIC的基本功能是把手机电池的单电压输入(手机锂电池的电压为3.6V)转换成多路电压输出给PCB上各部件供电(有的需要3.3 V,有的需要1.8 V,每种电压所需路数不等)。这种电源管理方式的缺点是方案成本较高,功耗控制简单即PMIC的电源输出同时开或同时关。基于此种简单的电源管理,SoC的主要功耗控制方式是降低时钟频率和关停时钟。

如今的智能手机都将电源控制部分集成到主控芯片内部作为电源管理单元(PMU),其优点是节省成本,和能够实现灵活的电源控制:包括灵活控制开关机、灵活调节各路电源输出的电平(比如软件可以在不需要SDRAM工作的时间段,通过PMU控制外部PMIC将输出给SDRAM的电压从3.3 V降到2.7 V,以减少SDRAM的功耗并保持其内容不丢失)和动态启停PMIC的某一路或某几路电源输出。基于此类PMU,SoC可以实现包括降低电压和关断电源在内的更多功耗管理模式。

冬眠(Hibernation)是SoC最省电的一种功耗模式,在此模式下,SoC中除RTC(实时时钟单元)和PMU仍然保持工作外,SoC其余部分的供电被关断从而进入功耗最省状态;同时在SoC外部,动态存储器(SDRAM)保持供电且处于自刷新(Self-Refresh)状态以维持其记忆体内容不变。当冬眠唤醒(Wakeup from Hibernation)被触发后,PMU恢复SoC的正常供电并指示软件从SDRAM直接启动系统。

另外,在PMU的开关机控制中存在一个细节问题:PMU所输出的开机使能电平是固定的,或为高或为低;在系统设计中必须保证PMU所输出的开机使能电平与电源管理控制器(PMIC)所要求的电平一致,否则就需要在PCB上添加反相器或重新选择符合要求的PMIC。注意这个有效开机使能电平的确定难以通过软件的方法来解决,因为软件必须在SoC正常上电之后才能运行,如果在芯片上电之前,PMU中预定的开机使能电平与实际PMIC要求的电平不符,则无法正常开机。

笔者在其公司最新设计的SoC中改进了PMU的设计,实现了自适应开机和冬眠功能。其中,自适应开机就是无论外部PMIC所要求的开机使能电平是高是低,PMU通过自身硬件进行自动判别并记忆,然后输出正确的开机使能电平;同时PMU实现了特殊硬件机制使得系统开发人员能通过软硬件结合轻松实现冬眠功能。

1 电源管理单元

首先给出PMU的接口和寄存器设置,读者由此可以把握本PMU设计的基本规范(spec)。如图1所示。

1.1 PMU接口

VDDP/GNDP:专门给PMU供电的管脚,一直有电(Always on Power);与之对应,VDDM/GNDM给外部SDRAM以及“冬眠”唤醒部件供电,VDDC/GNDC为主电源,给SoC其他功能模块和系统其他部件供电。

RSTn:复位输入,低电平有效;在PCB上有一个由主电源VDDC供电的复位发生器(PoR)。当VDDC掉电时,RSTn将保持为低;当VDDC上电时,RSTn经过一段延迟(如50 ms,不同复位发生器延迟不一样)由低变高并停在高电平直到VDDC掉电。

CLK:32 kHz时钟输入,用于给按键计时;(此时钟为复用RTC模块的低功耗高精度实时时钟)。

PSI[1:0]:2个按键输入接口,PSI[0]用于开关机键,PSI[1]用于“冬眠”唤醒键;输入值为低表示相应键有按下。

PSO[1:0]:2个电源使能输出接口,PSO[0]使能VDDC,PSO[1]使能VDDM。[p]

1.2 PMU寄存器

PVL:存储电源有效使能电平,即指示电源VDDC和VDDM的有效使能电平;在手机初次上电或发生电源失效后恢复使用时,此寄存器值可能不正确;每次开机时,其值由“自适应开机”逻辑来校正;该寄存器值也允许软件修改。

PCR[1:0]:电源控制寄存器,PCR[0]控制VDDC的使能/关断,PCR[1]控制VDDM的使能/关断;其值由软件控制:1为使能,0为关断;当PCR为“使能”时,PSO输出PVL指示的电平,否则输出为高阻状态(要求PCB上PSO被拉至“关断”状态)。

PPR[23:0]:常数寄存器,仅当复位结束且其值非固定值24h’C5ADA5时由硬件自动写入该固定值;PPR用于指示电池供电是否正常,当电池被拔出或其供电失效时,PMU也失去供电(VDDP无电),该寄存器值无法保持,当VDDP恢复供电后,PMU根据此寄存器的值判断自身状态并进行必要初始化处理。

PFR[19:0]:软件可设的按键时间阈值寄存器,其中PFR[19:9]指示开关机键PSI[0]的按键有效时间阈值,PFR[8:0]指示“冬眠”唤醒键PSI[1]的按键有效时间阈值;达到阈值按键有效;阈值计算公式为(单位:s):

(PFR+1)x64×CLK周期=(PFR+1)/29

在手机初次上电或发生电源失效后恢复使用时,PFR[19:9]被初始化为2 s,手机正常开启后,软件可写入合适的阈值,此阈值应远大于上电后的复位延迟(一般为20~200 ms)。

PSR[31:0]:数据寄存器,软件在控制SoC进入冬眠模式前,可将关键性数据(如SDRAM中操作系统的启动地址)写入此寄存器,当冬眠唤醒时,软件据此寄存器值做出相应处理。

2 自适应开机功能

本功能是对智能手机主控芯片内部开关机控制逻辑的改进,通过特殊硬件机制对外部电源管理芯片(PMIC)的有效开机电平进行自动判别和记忆,使得PMU输出正确的开机使能电平。

2.1 功能框图和接口、构件说明

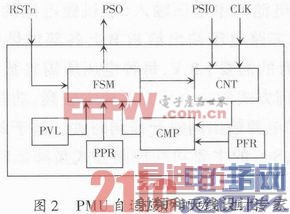

自适应开机功能框图如图2所示。

图2中,PSIO即前述PSI[0],为开关机键输入;FSM为开关机控制有限状态机;CNT[16:0]为按键时间计数器;CMP是比较器。

2.2“自适应开机”过程

初始状态:系统处于关机状态,除PMU,RTC仍然保持有电外,SoC其他模块均处于掉电状态,具体初始信号如下:

PSIO:开关机键值保持高,即没有按下;

CLK:32 kHz时钟一直有效;

RSTn:系统复位输入保持为低,即复位有效;

PSO:电源使能输出高阻,即关机;

FSM:开关机控制有限状态机处于“关机”状态;

CNT:按键时间计数器保持清零状态。

启动开机:用户持续按下开机键,触发硬件逻辑变化,具体信号和状态变化如下:

PSIO:开关机键输入为低电平,即该键按下;

CNT:计数器开始计数(每隔一个CLK周期,计数器加1);

CMP:比较器在每个CLK周期都将CNT值与{PFR[19:9],6’b111111}进行比较,并将比较结果送给FSM;

FSM:当收到比较相等的信号,FSM进入“开机尝试”状态,即控制PSO输出PVL所指示的电平,同时复位计数器使之重新开始计数;

PSO:输出PVL所指示的电平,即尝试使能开机上电;

RSTn:如果PVL所存值正确,上述上电过程成功,手机正常上电,经过复位延迟后,复位变为无效idianndiane:按键键;FSM进入“开机成功”状态(等待开关机键再次按下,然后进入“关机”状态)。

初次或异常开机过程:在手机初次上电或发生电源失效后恢复使用时,PVL寄存器的值可能错误;此时开机过程基本同上,只是FSM进入“开机尝试”状态后,PSO输出与PMIC期望相反的电平,此后的过程说明如下:

CNT:在FSM进入“开机尝试”状态后,重复开始计数;

CMP:当按键时间第二次达到阈值,比较器将再次输出比较相等的信号;

FSM:FSM在“开机尝试”状态再次收到比较相等的信号,将PVL值取反存入PVL寄存器;

PSO:保持输出PVL所指示的电平,使能开机上电;

RSTn:上电过程成功,经过复位延迟后,复位变为无效idianndiane按键键;FSM进入“开机成功”状态。易知在此异常开机过程中,用户需要持续按住开机键至少两倍于阈值所定的按键时间。以上开关机控制有限状态机变化图如图3所示。

3 冬眠功能

冬眠(Hibernation)是一种独特的省电模式。其特点之一是功耗极低近乎关机,与关机状态不同的是在PCB上SDRAM和用于唤醒的部件仍然有电,其中SDRAM处于低功耗的自刷新状态;特点之二是快速唤醒,为了保证良好的用户体验,系统要从SDRAM快速启动并快速回到冬眠前的现场。显然,实现冬眠功能需要SoC(主要是PMIC)、SDRAM和系统PCB上硬件机制的支持和软件的配合。[p]

3.1 功能框图和信号、构件说明

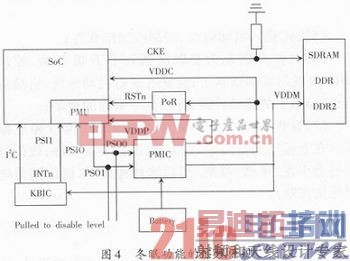

冬眠功能的实现框如图4所示。

图4中的部件:SoC为主控芯片;PMU为主控芯片内的电源管理单元;PMIC为电源管理芯片;SDRAM为动态存储器,包括DDR/DDR2/DDR3等;PoR为复位发生器;KBIC为键盘控制芯片,用于唤醒“冬眠”,其INTn与PSI1相连,I2C连到SoC的相应接口;KBIC由VDDM供电;图4中的信号:VDDP/VDDM/VDDC为PMIC的电源输出,分别给PMU,SDRAM/KBIC和其他部分供电;CKE是从SoC输出至SDRAM的控制信号,用于控制SDRA M的自刷新状态;SoC的电源使能输出PSO0/PSO1被拉到关断状态(如果使能电平为高,拉到GNDP,否则拉到VDDP)。

3.2 冬眠功能实现过程

3.2.1 进入冬眠

(1)软件保存快速启动代码和当前程序现场到SDRAM;

(2)软件控制SDRAM进入自刷新模式(CKE=0并保持到唤醒之后);

(3)软件控制SoC预备进入“冬眠”模式(包括停时钟,关PLL等);

(4)软件将快速启动的初始地址写入PSR;

(5)软件将2’bI0写入PCR(即关VDDC,保持VDDM);

(6)硬件上PSO0输出高阻,PSO1输出有效使能电平;由于VDDC掉电,RSTn拉低复位有效;CKE输出为高阻,由下拉保持在低电平使SDRAM维持自刷新状态。

3.2.2 唤醒冬眠

(1)用户按下指定键导致PSI1拉低达到阈值时间,触发冬眠唤醒逻辑;

(2)硬件控制PSO0输出有效使能电平使VDDC上电;

(3)SoC进入复位阶段,其中CKE的复位值为0;

(4)PoR在经过固定延迟后太高RSTn,使复位失效;

(5)SoC进入启动阶段,控制权交给软件;

(6)软件判断此为冬眠唤醒而非开机启动,控制SDRAM跳出自刷新状态;读PSR获得启动地址,直接运行SDRAM上的启动代码,并回到冬眠前的现场;

(7)软件判断引起冬眠唤醒的原因,执行相应操作。(在上述功能框图中,KBIC被用作唤醒部件,按任意键都会引发“冬眠”唤醒,然后软件通过I2C读出键值确定所按何键)。

4 结语

自适应开机功能简化了PCB上供电电路的设计,也使系统设计者能自由选择性价比更高的PMIC从而有助于降低整机成本;自适应开机的实现方法已由笔者所在公司申请专利保护。

本文所公开的冬眠功能已成功用于电纸书的应用:读者阅读当前页时,SoC进入冬眠状态,超级省电;当读者按动翻页键(PgDn或PgUp)时,SoC快速复活并显示下一页或上一页的内容,然后又开始冬眠。当使用Mobile SDRAM作为外部动态存储器时,笔者测量其电纸书参考系统的普通待机功耗为2.2 mA,而在“冬眠”状态下的待机功耗为180μA(主要来自Mobile SDRAM的自刷新功耗)。由是,利用冬眠功能本电纸书一次充电后的使用时间可从数周延长到数月。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:低功耗无线检测

下一篇:漏电保护器测试系统的设计