- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

一种夹层电阻结构及其应用

1 引言

在集成电路的线路设计中,特别是模拟电路的设计中,不可避免地都会需要用到电阻。对于低阻值的应用,一般可以用铝线电阻、多晶电阻、N+电阻或者P+电阻等实现。对于更大一点的电阻,则可以用N阱电阻、P阱电阻或者高阻多晶等实现。对于更高阻值要求,或者阻值要求高但是占用面积要小且精度要求不高,这时候可以用倒比的MOS管或者夹层电阻来实现。顾名思义,夹层电阻就是被其他层次夹在中间的电阻,夹层电阻的方块阻值一般在5~50 kΩ,随着电压的提高,还可以到100 kΩ或更高。

2 夹层电阻结构及原理特性分析

2.1 夹层电阻的结构

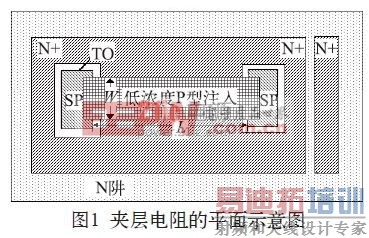

在集成电路工艺中,实现夹层电阻有很多种方法。本文研究的夹层电阻就是其中的一种,它不需要通过额外增加光刻MASK层就能实现。图1为该夹层电阻的平面示意图。

图1中,夹层电阻区为低浓度的P型注入区,它主要利用工艺中的现有层次实现,比如Pbase层或者Pbody层。该P型夹层电阻区被N+和N阱完全包围,因此该结构就是一个被N+和N阱两个层次夹在中间的P型夹层电阻。

2.2 夹层电阻的特性

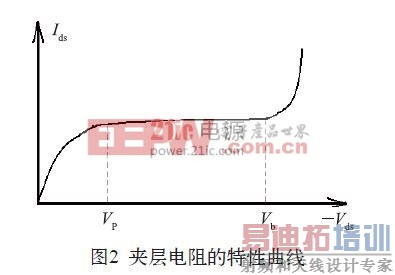

夹层电阻的优势是阻值很高,缺点是对电压比较敏感。对该夹层电阻进行I-V扫描,起始电压为0 V,步进为0.5 V,结果发现如下特性:当电阻两端电压从0开始增加时,夹层电阻的阻值迅速上升,但是到电压超过4 V左右后,电阻阻值虽然还是继续增加,但是此时呈现出线性上升的特性,即电阻跟随电压呈比例地上升,当电压到14~15 V左右时,电阻开始急剧减小,呈现出击穿效应。把上述电阻测试时的I-V数值进行曲线拟合,得到图2.

图2中,拐点Vp约为4 V,拐点Vb约为14~15 V.

2.3 夹层电阻的原理分析

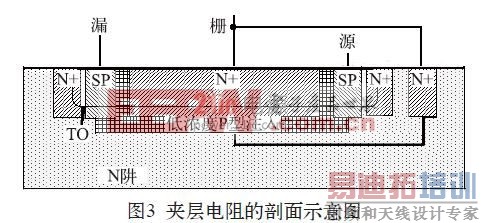

观察该曲线,发现它很像MOS管的输出特性曲线。进一步分析其纵向结构发现,该夹层电阻实际上可以理解成一个P沟道的JFET管(结型场效应管),它的纵向剖面示意图如图3所示。

图3中,JFET管的沟道区为低浓度的P型注入区,P型沟道被N+和N阱上下夹住,因此可以把N+和N阱看成JFET管的栅极(Gate),把两个SP注入区一个看成JFET管的源端(Source),另一个看成JFET管的漏端(Drain)。

因此在图2中,拐点Vp就是该P沟道JFET管的夹断电压,当-Vds电压超过Vp后,JFET管产生夹断,源漏电流开始趋于稳定。拐点Vb为该P沟道JFET管的击穿电压,当-Vds电压大于Vb后,JFET管产生击穿,Ids增大。

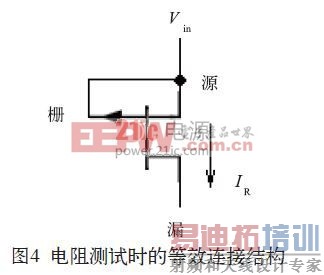

在前面的夹层电阻测试时,实际上是把PJFET管的栅端(Gate)和源端(Source)短接,形成了图4所示的连接结构。

由图4可知,只要把该JFET管的栅源短接且都接到输入工作电压Vin上,则当电压在Vp和Vb之间变化时(即Vp

一般来说,Vp在3~4 V左右,而Vb可以在10~15 V左右甚至更高,当然,由于不同工艺间的差异,Vp和Vb的大小会有所不同。

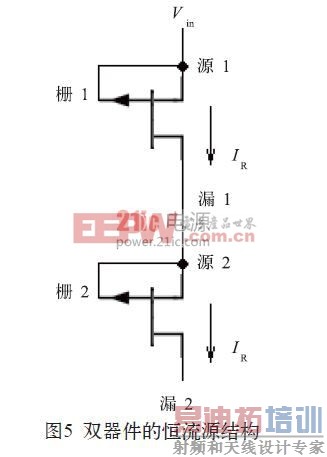

上述单器件电流源能满足输入电压在4~15 V左右之间变化时,输出恒定电流。为了获得更宽的电压范围,需要对上述电路进行改进,如图5.

[p]

[p]

如图5所示,通过把两个相同大小的JFET管串联,可以适应更大的电压变化范围,此时,可以让Vin在2Vp和2Vb之间变化时(即2Vp

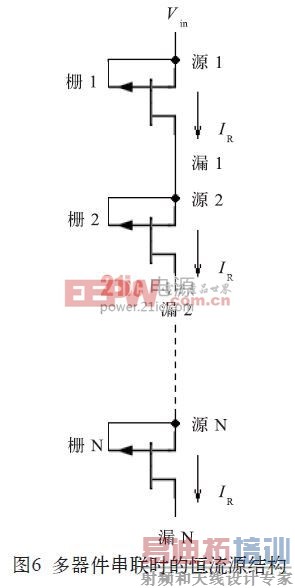

根据上述原理进行类推,当串联JFET管的个数为N(N为自然数)时(见图6),它允许的工作电压范围就是N×Vp~N×Vb,而且当N×Vp

3 振荡器的设计

3.1 振荡器的原理

利用该夹层电阻的特性,下面开始设计一款振荡器。该振荡器的设计要求为:工作电压范围为3~25 V,振荡器功耗越低越好,最好在微安级,且希望当电压在9~25 V之间变化时,振荡器的输出频率是恒定的。

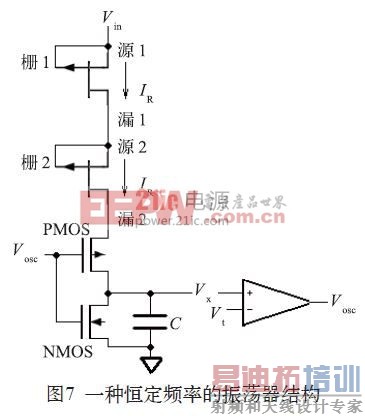

在该振荡器中,由该夹层电阻(等效为P沟道JFET管)来提供恒流源,用于芯片内部振荡器的电容充放电电流。由于振荡器的振荡频率主要取决于电容充放电的电流大小,因此一旦电流恒定,则振荡频率就不变。电路要求的电压最高为25 V,根据前面的分析,单个器件的耐压会不够,因此采用双器件串联结构,理论耐压应该可以接近30 V.电路设计如图7.

图7是振荡器的简单原理示意图,实际线路在此基础上还会增加一些辅助线路。在图7中,Vosc用于控制电容的充放电状态,JFET管提供恒定电流源IR对电容C进行充电,Vx则输出到后级的电压比较器。电路工作的时候,一开始Vosc为低电平,此时PMOS管打开,基准电流IR开始给电容C进行充电,电容C上的电压Vx逐渐上升,一旦Vx达到门限电平Vt,则比较器就翻转,从而使Vosc也发生翻转变为高电平,这时,PMOS管关断,NMOS管打开,由于NMOS管放电能力较强,电容C上的电压瞬间就被放到GND,此时Vosc又翻转变为低电平,NMOS管关断,PMOS管开始充电。就这样,通过保持充电电流的恒定,使得振荡器的振荡频率也始终保持恒定。

3.2 振荡器的实现和优化

在电路的实际实现中,采用了0.8 μm的高压工艺。经过对出片电路的实际测试,发现随着电压升高,振荡器频率逐渐变快,当电压超过10 V后,频率开始维持不变,一直到电压接近30 V,频率始终不变。也就是说当电压在10~30 V之间变化时,振荡器频率恒定,振荡器的工作电流在整个电压变化范围内不超过3 μA.

显然,频率稳定的最低电压为10 V,高于设计要求的9 V.从前面夹层电阻的原理分析部分可以知道,为了降低频率稳定的最低电压,可以采用两种思路:一种是降低夹层电阻的夹断电压Vp;另一种是采用单个夹层电阻来实现恒定电流。第一种思路,夹断电压Vp主要取决于JFET沟道区的P型注入浓度,以及P型注入、N阱、N+这几个的结深,结深一般不好调节,而浓度也较难控制,因此实施有困难,而且最低电压为2×Vp,实施效果也很有限。第二种思路,主要是要提高夹层电阻的击穿电压Vb.根据对该夹层电阻的纵向结构分析可以知道,该夹层电阻的击穿首先发生在低浓度的P型注入区和上层的N+之间,也即击穿电压Vb就是N+和P型沟道区的击穿电压。

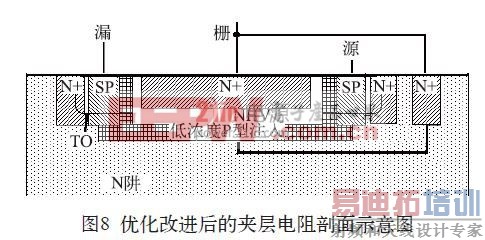

因此,尝试在低浓度的P型沟道区域上层N+的下方,用一个低浓度的N型区来外包N+,如图8.

该低浓度N型区用工艺中现成的高压N注入(即NHV)来实现,以此来提高夹层电阻的耐压。

3.3 优化改进结果

电路改进设计后,经过试验验证,采用此种优化结构后,振荡器可以工作在3~30 V的工作范围,而且当电压大于5.5 V以后,振荡器的输出频率就不再变化,也即当电压在5.5~30 V之间变化时,振荡器频率恒定,同时振荡器最大工作电流约为2.5 μA.至此,该振荡器的各项指标全部达到了设计要求。

4 结束语

夹层电阻是一种比较特殊的电阻。在低电压工作场合,夹层电阻一般都被当做高阻值的电阻来使用。但是在高电压工作场合,或者是宽范围工作电压的场合,此时夹层电阻就相当于是一个JFET管,利用该特性,在很多设计中,特别是模拟电路的设计中,可以把电路设计得更精巧或者实现更低的功耗。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:埋嵌式元件共面度测量方法研究(

一)

下一篇:埋嵌式元件共面度测量方法研究(

二)