- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

计算机电源 “白金“ 化

80+TM 和计算机产业拯救气候行动计划 (Climate Savers Computing) 给计算机电源设立了一个强有力的效率标准。这些标准的"白金"级别规定计算机电源在 20% 额定负载状态下必须有 90% 的效率,50% 额定负载时效率必须达到94%,而在 100% 负载时效率必须达到 91%。为了满足这些标准,一些电源设计人员选择使用一个具有同步整流的相移、全桥接 DC/DC 转换器。这种拓扑结构是一种比较好的选择,因为它可以在主 FET 上实现零电压开关 (ZVS)。一种普遍使用的驱动同步整流器的方法是利用已经存在的信号驱动主 FET。这样做存在的唯一问题是要求主 FET 时滞,以实现零电压开关。这会导致两个同步整流器在快速续流期间同时关闭,从而允许过多的体二极管导电,最终降低系统效率。本文的目的是建议使用不同的时序,驱动这些同步整流器,从而减少体二极管导电并最终提高整体系统效率。

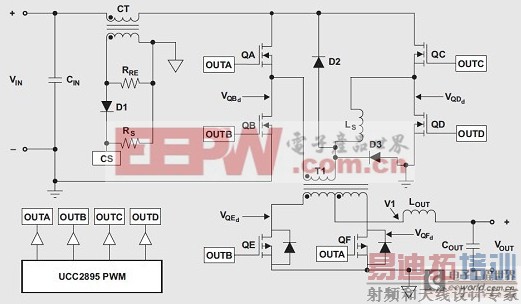

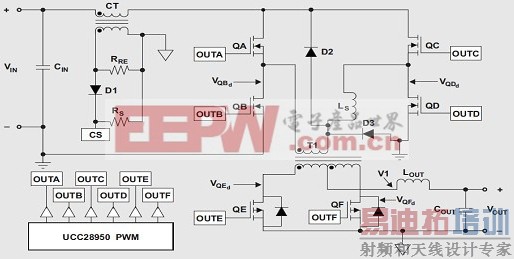

市场上有一些脉宽调制器 (PWM),其设计目标是用于控制相移、全桥接转换器,而非驱动同步整流器 (QE 和 QF)。工程师们发现他们可以通过 PWM 控制器的控制信号OUTA和OUTB来控制同步 FET,这样便可以在本应用中使用这些控制器。图 1 显示了其中一款转换器中的一个功能示意图。

图 1 同步整流改进型相移、全桥接转换器

问题

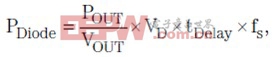

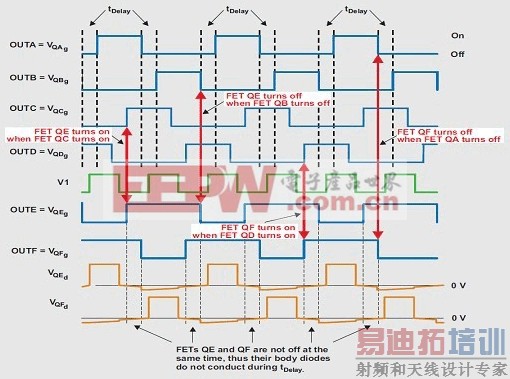

通过延迟H桥接(QA、QB、QC、QD)的 FET 导通,PWM 控制器有助于在这些转换器中实现 ZVS。FET QA 和 QB 导通和断开转换过渡之间的延迟 (tDelay) 会使同步 FET QE 和 Q F同时断开,从而允许其主体二极管实施上述导电行为。下列方程式较好地估算了续流期间 QE 和 QF 的主体二极管传导损耗

其中 POUT 为输出功率,VOUT 为输出电压,VD 为主体二极管的正向压降,而 fs 为电感开关频率。

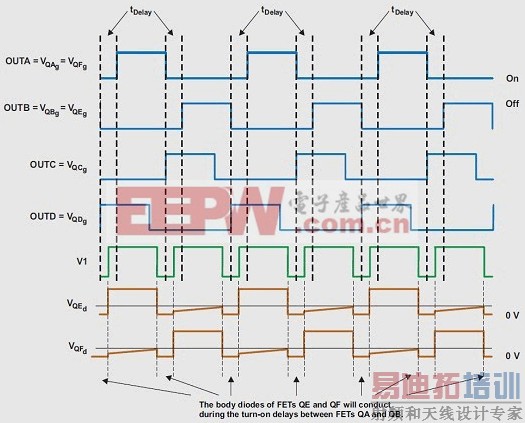

QE 和 QF 的主体二极管传导损耗 (PDiode) 过多会使设计达不到"白金"标准。更多详情,请参见图 1 和图 2。如图所示,OUTA 驱动 FET QA 和 QF,而 OUTB 驱动 FET QB 和 QE。V1 为 LOUT 和 COUT 滤波器网络输入的电压,而 VQEd 和 VQFd 为相应同步整流器 QE 和 QF 的电压。

图 2 所示转换器的时序图

解决方案

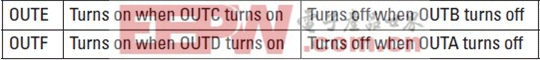

若想减少 QE 和 QF 主体二极管导电,最好是在 QA 和 QB 延迟期间 (tDelay) 让这些同步整流器开启。要做到这一点,必须通过其自有输出来驱动 FET QE 和 QF,其中"导通"时间而非同步的"断开"时间会重叠。图 3 显示了具有 6 个单独驱动信号(OUTA 到 OUTF)的相移、全桥接转换器的功能示意图。通过根据 QA 到 QD 的边缘,导通和断开 OUTE 及 OUTF,可以产生 QE (OUTE) 和 QF (OUTF) 的信号。表 1 和图 4 显示了完成这项工作所需的时序。图 4 所示理论波形表明,这种技术去除了主体二极管导电,其会在 tDelay 期间两个栅极驱动均为断开时,与图 2 所示栅极驱动信号一起出现。

表 1 OUTE 和 OUTF 导通/断开过渡转换

图 3 使用表 1 时序的相移、全桥接转换器

图 4 减少 QE 和 QF 体二极管导电的时序图

试验结果

为了查看这种技术在减少主体二极管导电方面的效果如何,我们对一个 390-V 到 12-V 相移、全桥接转换器进行了改进,旨在通过图 2 和 4 所示信号驱动 FET。

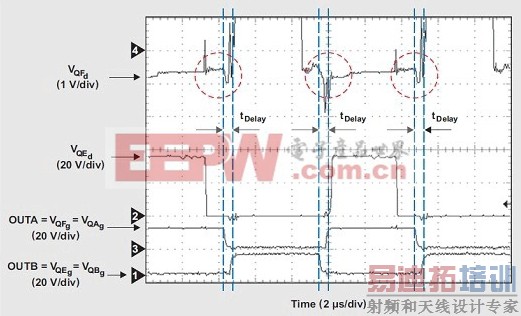

图 5 显示了同步FET(QE 和 QF)栅极的波形图,它们通过 OUTA 和 OUTB PWM 输出驱动。图中,在 OUTA 和 OUTB 之间的延迟时间 (tDelay) 期间可以观测到主体二极管导电。

图 5 QE 和 QF 主体二极管导电波形图

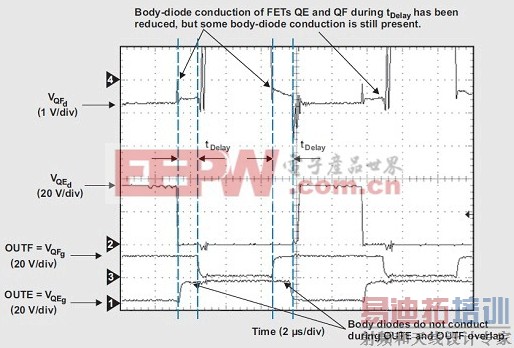

下一页的图 6 显示了同步FET(QE 和 QF)栅极的波形图,它们通过图 3 所示 OUTE 和 OUTF 信号驱动。这些信号都产生自 TI 新的 UCC28950 相移、全桥接控制器。图 6 表明 FET QE 和 QF 导通的同时主体二极管没有导电。尽管仍然可以看到一些主体二极管导电,但没有图 5 那么多。

图 6 显示了 QE 和 QF 低主体二极管导电的波形图

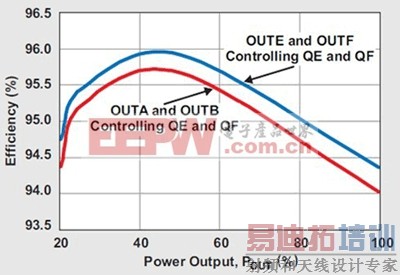

我们对两种驱动方案(OUTA 和 OUTB 与 OUTE 和 OUTF)从 20% 到满负载条件下 600-W DC/DC 转换器的效率进行了测量。在下一页的图 7 中,显示了这两种驱动方案的转换器效率数据。我们可以看到,相比使用 OUTA 和 OUTB,在 50% 到 100% 负载时使用 OUTE 和 OUTF 的效率高出约 0.4%。0.4% 效率增加看起来似乎并不多,但在设计人员努力想要达到"白金"标准时效果就不一样了。

图 7 不同 QE 和 QF 驱动方案下 600-W DC/DC 转换器的效率

结论

即使我们可以通过一个并非为同步整流(OUTA 和 OUTB 驱动方案)而设计的相移、全桥接控制器来对一个具有同步整流器的相移、全桥接转换器进行控制,实现 ZVS 所要求的 OUTA 和 OUTB 之间接通延迟也会使两个同步 FET 在同一时间 (tDelay) 关闭。这种延迟会导致在 FET 快速续流期间出现过多的体二极管导电。本文表明更加有效的方法是:在快速续流期间叠加同步整流器的"接通"时间,以便让体二极管不导电。利用这种方法,虽然体二极管导电并没有完全消失,但其被极大减少,从而提高了整体系统效率,让"白金"效率标准更容易达到。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...