- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

以较高的开关频率在负载点 (POL) 应用中工作

摘要: Power Clip 33 封装十分新颖,旨在增加同步整流 (SR) 降压应用中的功率密度,同时使用与传统分立式 Power 56 封装相比明显较小的 PCB 面积。 本文详细分析飞兆 Power Clip 3.3x3.3 Dual 是如何实现这一性能的。

概述

本文:

a. 总结了通过 Power Clip 封装实现的电源系统尺寸和电流密度的改进

b. 详细介绍了实现性能提升的 Power Clip 的特性

c. 提供了一对设计示例,展示通过该小占位面积和高频设计实现的总体元件占位面积减少

d. 展示了将 Power Clip 与传统设计在效率、功率损耗、波形、温度和热阻方面进行比较的测量数据。

简介

对电源工程师来说,功率密度 (A/mm2) 是器件选型中的一个重要指标。Power Clip Dual MOSFET 的设计是经过针对性的优化,可为同步降压调节器应用提供异常高的功率密度。

全新的 Power Clip 3.3x3.3 是对优化品质因数 (FOM)的硅技术和增强的散热设计的高效结合。

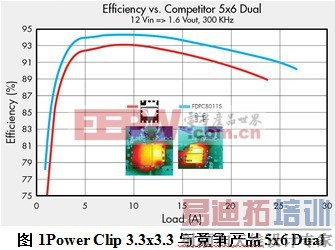

图1和图2展示这一新产品相较于两个竞争产品的性能。 新 Power Clip 较这两者性能都好。

图1显示,与较大尺寸的 5x6 竞争产品相比,Power Clip 的效率更高。 图1中的散热图片是在测试结束时拍摄的。 较小的 Power Clip 能够以同等的 TJ处理额外的 3 A 负载。

图2显示,与同等尺寸的 3.3x3.3 竞争产品相比,Power Clip 具有更好的效率和温度。 图2中的散热图片是在测试结束时拍摄的。 Power Clip 以低6 °C 的 TJ 温度处理了额外 8 A 的负载。

注意,这一图2评测使用与图1不同的控制器完成,因此 Power Clip 结果略有不同。

图3展示了过去 6 年中测试的一系列飞兆评测板的功率密度的演化。 Power Clip 产品实现的密度是上一代产品的近两倍。

这得益于 PowerTrench®工艺和封装技术的改进。图4展示了 Power Clip 33 MOSFET Asymmetrical Dual MOSFET 设计在负载点 (POL) 或同步整流 (SR) 降压转换器应用中的演化。 Power Clip 33 MOSFET 将一对分立式 MOSFET 的最佳的特性结合到 3.3x3.3 mm 的封装上。

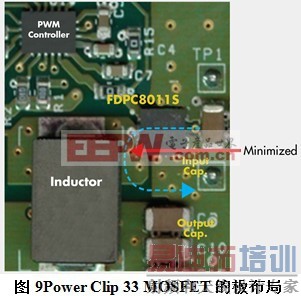

这一小尺寸、高效率的高频封装使得总体电源设计具有非常小的占位面积。 MOSFET、输入电容、电感和输出电容都嵌入到一个非常小的区域。 小尺寸电源系统最小化了开关节点区域,降低了从 SW 节点辐射出电磁干扰 (EMI) 噪音的风险。

封装底部的裸露 GND 和 V+ 焊盘支持从 MOSFET 晶圆到铜箔到环境的高效热耗散路径。

在设计具有最少寄生参数和最佳开关性能的封装时,输入电容与封装 V+ 到 GND 引脚之间形成的小环路大小至关重要。 Power Clip 封装上优化的 V+ 和 GND 引脚布局支持输入电容非常紧密的布局,以最大限度地减少环路面积,并减少寄生电感和开关损耗。

如图10所示,在 Power Clip 设计中,高频开关环路显著减小。 在开关转换期间,比如从 LS-off到 HS-on或从 HS-off到 LS-on,电流必须快速从一个 MOSFET 转换到另一个。 这一转换操作发生在由两个功率 MOSFET 和输入电容组成的环路之间。 该环路中的瞬态开关比输出电感中电流的纹波频率快几个数量级。 因此,这是决定开关损耗的环路。 对于一对分立式 MOSFET ,开关电流在返回到输入电容之前必须流经整个 HS 和 LS Mosfet。 对于 Power Clip 封装,电流出入于一个紧密环路中封装的同一面,仅由两个引脚的间隔隔开。 在分立元件的布局中,高频环路大小受到 MOSFET 的封装尺寸的限制。 对于 Power Clip,环路大小受到输入电容的大小的限制。

为高频同步整流低压转化器优化设计的Power Clip 33 MOSFET

本节展示一个典型的电源系统的详细分步设计,并展示因高操作频率和高效率相结合而减小的板面积。

对于芯片组电源,选作目标工作条件的一个常见设计是 12 Vin,1.6 Vout和 25 Aout。 对于操作频率,选择了两个点: 300 kHz 和 600 kHz。 输入电容、输出电容和输出电感的元件尺寸都因较高的操作频率而减小。

较高的操作频率可改善瞬态响应,同时保持纹波不变,并减小电感和电容的元件大小。

表1展示操作频率为 300 kHz 和 600 kHz 时的设计示例。 与 300 kHz 的分立式 MOSFET 设计相比,在 600 kHz 时使用 Power Clip 33 MOSFET 可让设计人员节省 42% 的总 BOM 面积。

数据测量效率、功率损耗、温度上升

在一个同步降压转换系统中,MOSFET 的额定电流基于若干因数的折衷:

a. MOSFET 的最大 TJ

b. 输出功率

c. 效率

d. RΘJA 热阻

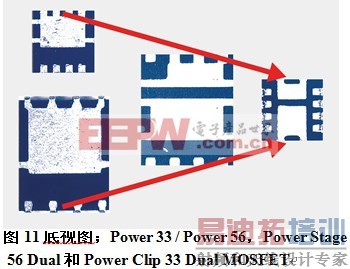

通过封装结构的显著改进以及高级硅技术,Power Clip 33 MOSFET 封装可在一个 3.3 x 3.3 mm 的占位面积中提供 20 A 解决方案。 为了评测 Power Clip 33 Dual MOSFET 的性能,我们测试了FDPC8011S和两个备用的大尺寸设计,即一对分立式Mosfet HS Power 33 (FDMC8588) / LS Power 56 (FDMS8560S) 和 FDMS3624 Power 56 Dual MOSFET。图11展示了封装尺寸的发展。

[p]如表2所示,使用最新一代的 FOM 硅,FDPC8011S 能够近似匹配大尺寸备用设计的 RDS(ON)值。

效率:

图12和图13展示三个选项之间的效率和功率损耗比较: Power Clip 33 Dual、Power Stage 56 Dual 和分立式 Power 33 / Power 56。测试点是一个典型的 POL 操作点;12 Vin 和 1.6 Vout。 在 300 kHz 和 600 kHz 的频率下对性能进行了比较。

这些 MOSFET 组合经过测试,因为所有组合拥有类似的电气特性。 这就能够将小占位面积和低寄生参数的 Power Clip 33 设计与传统尺寸封装进行比较。 FDPC8011S 同时在 300 kHz 和 600 kHz 的频率下在几乎整个负载范围内展示出更高的效率和更低的损耗。

注意,分立式组合和 Power Clip 之间的性能交叉点在更高的操作频率下显著移出。 这反映了 Power Clip 33 更低的封装和开关环路寄生参数。

开关性能

表3展示了每个封装的 PSPICE 模型参数。 四个电感: HS 漏极、HS 源极、LS 漏极和 LS 源极,对于提升效率至关重要,因为它们都在 AC 开关路径中,且都能限制最大 di/dt 开关速度。 Power Clip 33 的一个独特功能是,LS MOSFET 源极朝下。 因此,LS 源极电感比之前的封装低一个数量级。

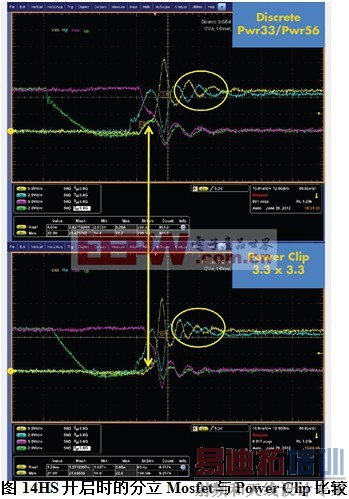

图 14 中所示的开关波形比较展示了分立Mosfet和 Power Clip 33 封装之间的开关速度差异。 波形比较中的若干因数凸显了寄生参数的差异。 在 HS 开启时,Vsw波形(黄色)中的初始步骤是由于 LS 源极电感创建了 Ls*dID/dt 电压阶跃。 请注意,分立Mosfet的的显著阶跃与 Power Clip 33 的几乎无阶跃。阶跃的差别是 Power Clip 33 的 LS 源极电感更低的一个直接迹象。这验证了表3中的预测。

除了开关速度考虑,低 LS 源极电感也最大限度地减少了 Vsw负脉冲信号,这发生在 HS 关闭时。 在图15中,注意 Power Clip 33 封装的Vsw负脉冲信号减少了 50%。 过大的 Vsw负脉冲信号会对驱动器造成压力,或者导致不稳定的驱动器行为和潜在的电路故障。 这在高负载电流瞬变期间尤其让人忧心。 HS 开关损耗往往由关损耗主导,这受到 HS 源极电感的强烈影响。

如表3所示,Power Clip HS 源极电感比备用设计少 1/3。 HS 源极电感似乎难于从开关波形直接确定。 源极电感的一个指示是 HS 开启时在 HS 栅极 (G) 波形中发生的电压瞬变。 这一瞬变归因于在 HS V_GS 测量的 LS*dID/dt。在图 14 中,对于 Power Clip 封装 Vsw上升地较快,表明 dID/dt 更快。 两个设计都在 HS V_GS 中显示出 4.8 V 的下降。如果在 dID/dt 更快时具有同等的下降,则表示 HS 源极电感更低。

如图10所示,由于其增强的封装设计、更小的尺寸和增强的引脚配置,Power Clip 33 预期因环路面积减小而拥有更低的总高频 (HF) 开关环路电感。

总高频环路电感可以通过 HS 和 LS MOSFET 波形共振实验测量计算得出,使用 MOSFET Coss从 LC 共振中为 L 求解。 对于图 14 的测量,分立Mosfet的总 AC 环路电感是 1.3 nH,而 Power Clip 的是 0.70 nH,降低了几乎 50%。 Vsw上升时间更快和振铃频率更高都是因为 Power Clip 33 的总 AC 环路电感更低。

寄生的高频开关环路电感在整个 HS MOSFET 中对根据 Vds测量的振铃有显著影响。 请注意在图15中,Power Clip 封装的过冲减少了 33%。

图 14 和图15中的所有数据均使用差分探头进行测量。 强烈建议使用高带宽 (BW) 差分探头准确地测量 HS FET 波形。

热性能

Power Clip 33 的热性能表现在一系列板设计上。 FDPC8011S 拥有从结到外壳/电路板的非常有效的热传递。 板热阻是限定封装温度上升以及相应的电流能力的主导因数。 HS 漏极朝下和 LS 源极朝下的 Power Clip 在典型的板设计中提供到两个大铜箔的良好热连接,V+ 和 GND。 为了实现最佳性能,使用 vias 增强到板 Vcc和 PGND 板架的热互连。 有关最佳设计实践的一个更详细的讨论,请参见FDPC8011S 数据手册的“应用信息”部分。

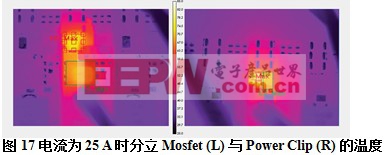

图16和图17显示分立式Mosfet和 Power Clip 封装的相关温度性能。 这一特性描述在一个可与服务器类产品设计相媲美的厚铜电路板上完成。 额定电流的一个常见性能指标是高于环境温度 40 °C 的 Tj上升。 在 65 °C 环境温度下,将产生 105 °C 的 Tj。如图16所示,对于这一评测板,更小占位面积的 FDPC8011S 在分立Mosfet电流能力的 10% 内。 鉴于分立Mosfet的较大占位面积,这是一项卓越的性能。

设计的额定温度基于 HS 和 LS MOSFET 温度的最大值。 对于该设计,图17显示,HS MOSFET 温度上升对于分立设计和 Power Clip 设计来说都是限制性参数。

三个备用设计的热阻数据表值如表4所示。 为标准的 1 平方英寸测试板上描绘的部件指定 RΘJA 的额定值。 一个典型的电源 PCB 拥有比测试板更低的热阻。表5显示在厚铜和薄铜评测板上测量的 RΘJA值。 分立Mosfet和 Power Clip 的最大额定电流在薄型铜板上较低,因为具有更高的热阻。 表5所示的热阻值同时描绘了结到环境和晶圆之间的耦合。 参考资料Error! Reference source not found.详细介绍如何执行这些测量,以及如何使用产生的热矩阵预测给定功率损耗的 HS 和 LS TJ。

结论

结合先进硅和 Power Clip 封装技术,FDPC8011S Power Clip 33 MOSFET 大大减少了封装寄生参数并超越了之前的分立式 Power 33 / Power 56 或 Power Stage 56 Dual 组合的 A/mm2性能。 在同步整流降压应用中,Power Clip 33 MOSFET 能够以比分立Mosfet更高的频率和效率在 20 A 负载下运行。

功率损耗降低,使得操作频率和效率更高。 因此,与传统的分立式 MOSFET 解决方案相比,Power Clip 33 MOSFET 可以节省 42% 的总面积。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...