- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

DDR_I布线

录入:edatop.com 点击:

原理图说明:

上图DDR_I电路中需要注意到信号线有CLK+/-,DQS0/1等.

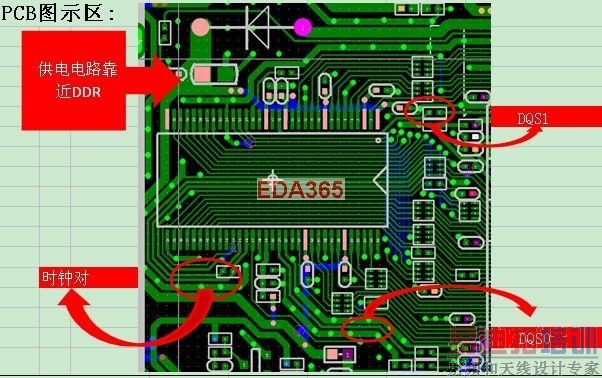

pcb图说明:

1: 13位地址线与16位数据线的宽度走6MIL就可以,每根线的间距为9MIL.

2:时钟走线宽度12MIL,两边包地处理,尽可能多打过孔.时钟线一定不要有过孔.

3QS0/1线的线宽12MIL,两边包地处理,尽可能多打过孔一定不要打过孔.

4DR芯片的高频电容要靠近相应的供电脚放置,连线宽度>=12MIL.其供电线宽度>=30MIL.单元供电LDO靠近DDR芯片放置.

5:REF电路需要靠近芯片的引脚放置,线宽>=12MIL.

6:整个DDR单元电路与外界需要用地线隔离.

上图DDR_I电路中需要注意到信号线有CLK+/-,DQS0/1等.

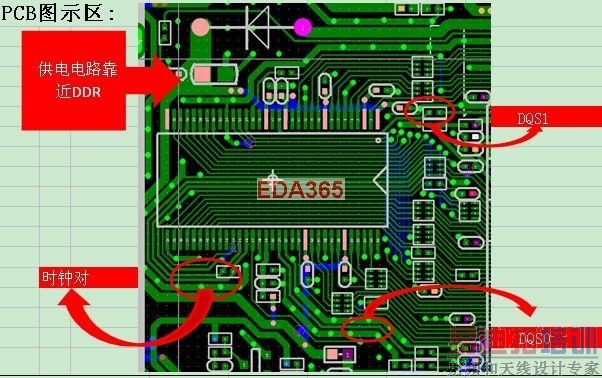

pcb图说明:

1: 13位地址线与16位数据线的宽度走6MIL就可以,每根线的间距为9MIL.

2:时钟走线宽度12MIL,两边包地处理,尽可能多打过孔.时钟线一定不要有过孔.

3QS0/1线的线宽12MIL,两边包地处理,尽可能多打过孔一定不要打过孔.

4DR芯片的高频电容要靠近相应的供电脚放置,连线宽度>=12MIL.其供电线宽度>=30MIL.单元供电LDO靠近DDR芯片放置.

5:REF电路需要靠近芯片的引脚放置,线宽>=12MIL.

6:整个DDR单元电路与外界需要用地线隔离.

甘渣:别来无样呀!

陈总,你这错别字。

还是可以的

和DDR_2的有什么实质性的区别呢?只是没看到你做等长而已。请教了

等长看芯片规格书了,这颗不需要等长,原则上等长是最好的。

呵呵,谢啦

干嘛不弄个PDF文档,把教程整理成一份就好了,方便我们学习啊

学习啊,都是画高速的高手呀.

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:PADS原理图导PCB

下一篇:powerpcb中层次原理图如何设置页间连接符

射频和天线工程师培训课程详情>>