- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

晶振串联电阻应该靠近哪边?

录入:edatop.com 点击:

一,串联端接之所以靠近源端,是因为IC的输出电阻总是很小,小于传输线的特性阻抗。(所以,通常传输线特性阻抗为50欧姆的pcb板中,串联端接电阻总是小于50欧姆。串联之后,源端才和传输线匹配)。

二,同理并联端接之所以靠近终端,是因为IC的输入电阻总是很大,大于传输线特性阻抗。(所以,通常传输线特性阻抗为50欧姆的PCB板中,并联端接电阻总是大于50欧姆。并联之后,终端才和传输线匹配)。)

请问一下:::::在晶振电路中,IC和晶振哪个是源端?哪个是终端?

二,同理并联端接之所以靠近终端,是因为IC的输入电阻总是很大,大于传输线特性阻抗。(所以,通常传输线特性阻抗为50欧姆的PCB板中,并联端接电阻总是大于50欧姆。并联之后,终端才和传输线匹配)。)

请问一下:::::在晶振电路中,IC和晶振哪个是源端?哪个是终端?

居然没一个人知道?

很明显是靠近晶振端。

十分感谢你的回复。可否说一下此图的出处?如果不是机密的话,可否与大家共享?谢谢!

楼上的大哥,很抱歉,原图不能给你哟,因为我们正在生产这个东西,这个图是出自老美的。我只能告诉你的是这个电阻靠近晶振放置绝对没错,我这有大把的板都是这样做的。

好的,谢谢。可靠就行!

学习了

再请教一下。串联的电阻是不是都很小,小于50,(传输线特性阻抗)?谢谢!

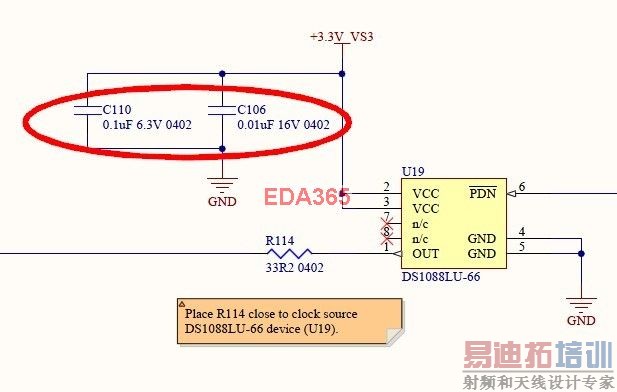

有源晶振串联47到50欧姆的电阻是做阻抗匹配。

就是出于信号完整性的考虑,如反射,阻抗匹配,阻值一般为22R-33R不等,如果时钟不是晶振产生的,是从芯片如FPGA或者ASIC引脚出来的,这个电阻显得尤其重要。

就是小于50咯

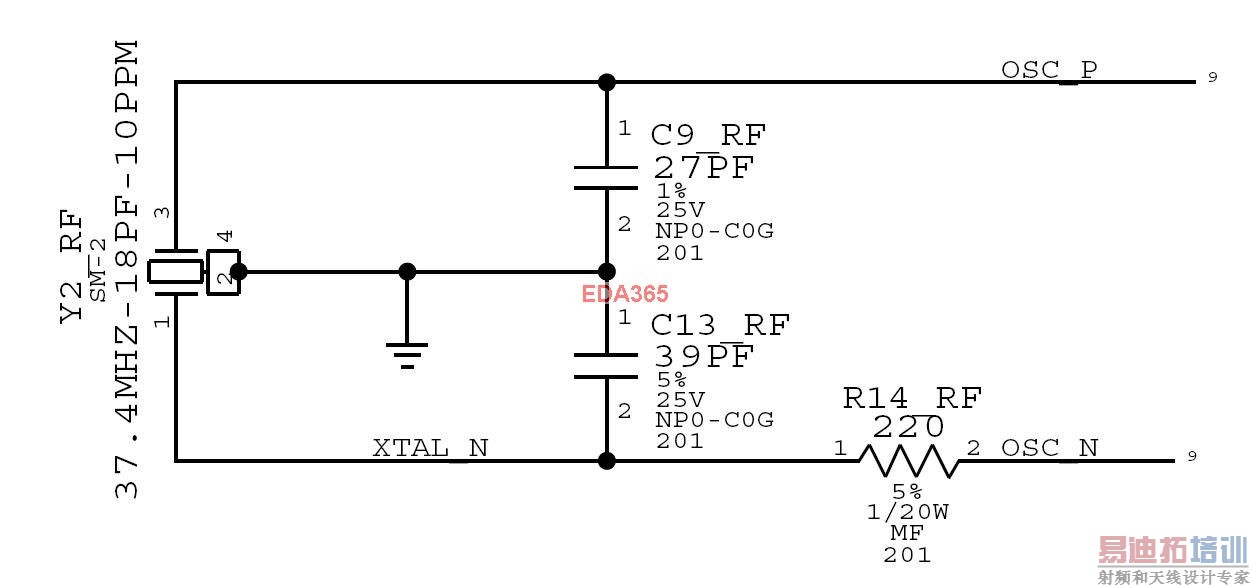

谢谢!。这张原理图又是为哪般呀。大于50了。难道是晶振和晶体串联电阻理念不一样?

这张。

晶振的第三脚为clkout,明显这里是输出信号,驱动端.

源端端接电阻应该靠近驱动端放置.

发表于 2011-9-1 12:40

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:pads软件

下一篇:铺铜之后没有布线的地线网络不能和铜皮接一起呢(解决了)

射频和天线工程师培训课程详情>>