- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

MOSFET结构及工作原理

金属-氧化层-半导体-场效晶体管,简称金氧半场效晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor, MOSFET)是一种可以广泛使用在模拟电路与数字电路的场效晶体管(field-effect transistor)。MOSFET依照其“通道”的极性不同,可分为n-type与p-type的MOSFET,通常又称为NMOSFET与PMOSFET,其他简称尚包括NMOS FET、PMOS FET、nMOSFET、pMOSFET等。

结构

图1是典型平面N沟道增强型MOSFET的剖面图。它用一块P型硅半导体材料作衬底(图la),在其面上扩散了两个N型区(图lb),再在上面覆盖一层二氧化硅(SiO2)绝缘层(图1c),最后在N区上方用腐蚀的方法做成两个孔,用金属化的方法分别在绝缘层上及两个孔内做成三个电极:G(栅极)、S(源极)及D(漏极),如图1d所示。

平面N沟道增强型MOSFET从图1中可以看出栅极G与漏极D及源极S是绝缘的,D与S之间有两个PN结。一般情况下,衬底与源极在内部连接在一起。

图3是N沟道增强型MOSFET的基本结构图。为了改善某些参数的特性,如提高工作电流、提高工作电压、降低导通电阻、提高开关特性等有不同的结构及工艺,构成所谓VMOS、DMOS、TMOS等结构。图2是一种N沟道增强型功率MOSFET的结构图。虽然有不同的结构,但其工作原理是相同的,这里就不一一介绍了。

工作原理

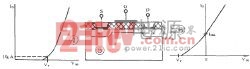

要使增强型N沟道MOSFET工作,要在G、S之间加正电压VGS及在D、S之间加正电压VDS,则产生正向工作电流ID。改变VGS的电压可控制工作电流ID。如图3所示(上面↑)。

若先不接VGS(即VGS=0),在D与S极之间加一正电压VDS,漏极D与衬底之间的PN结处于反向,因此漏源之间不能导电。如果在栅极G与源极S之间加一电压VGS。此时可以将栅极与衬底看作电容器的两个极板,而氧化物绝缘层作为电容器的介质。当加上VGS时,在绝缘层和栅极界面上感应出正电荷,而在绝缘层和P型衬底界面上感应出负电荷(如图3)。这层感应的负电荷和P型衬底中的多数载流子(空穴)的极性相反,所以称为“反型层”,这反型层有可能将漏与源的两N型区连接起来形成导电沟道。当VGS电压太低时,感应出来的负电荷较少,它将被P型衬底中的空穴中和,因此在这种情况时,漏源之间仍然无电流ID。当VGS增加到一定值时,其感应的负电荷把两个分离的N区沟通形成N沟道,这个临界电压称为开启电压(或称阈值电压、门限电压),用符号VT表示(一般规定在ID=10uA时的VGS作为VT)。当VGS继续增大,负电荷增加,导电沟道扩大,电阻降低,ID也随之增加,并且呈较好线性关系,如图4所示。此曲线称为转换特性。因此在一定范围内可以认为,改变VGS来控制漏源之间的电阻,达到控制ID的作用。

苏州工职院机电07C3-CZW-手打由于这种结构在VGS=0时,ID=0,称这种MOSFET为增强型。另一类MOSFET,在VGS=0时也有一定的ID(称为IDSS),这种MOSFET称为耗尽型。它的结构如图5所示,它的转移特性如图6所示。VP为夹断电压(ID=0)。

耗尽型与增强型主要区别是在制造SiO2绝缘层中有大量的正离子,使在P型衬底的界面上感应出较多的负电荷,即在两个N型区中间的P型硅内形成一N型硅薄层而形成一导电沟道,所以在VGS=0时,有VDS作用时也有一定的ID(IDSS);当VGS有电压时(可以是正电压或负电压),改变感应的负电荷数量,从而改变ID的大小。VP为ID=0时的-VGS,称为夹断电压。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:用TrenchFET

IV功率MOSFET系列设计更绿色、更小的电源

下一篇:新的电路保护方法将“智能激活”用于高倍率放电锂离子电池应用