- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

生成一个宽度与模拟电压方根成反比的脉冲

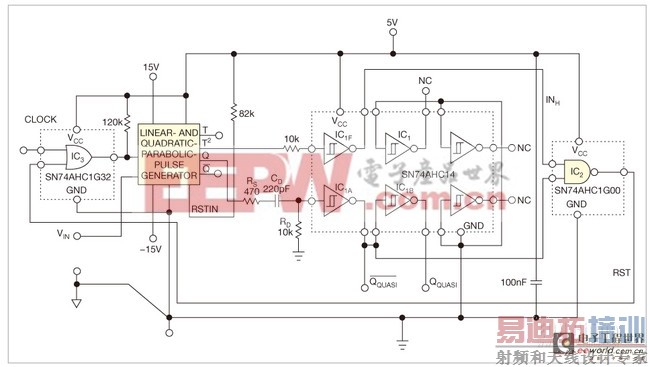

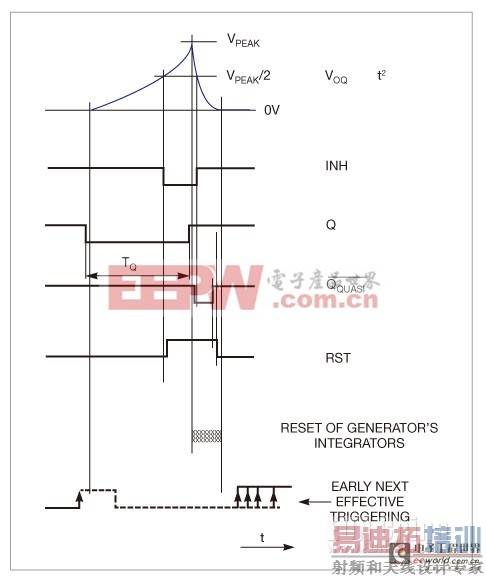

图1,时钟输入端由低至高的转换触发了单稳态。在互补的Q与Q输出处产生的脉冲宽度是0V~3V模拟输入电压的数学意义非线性函数。

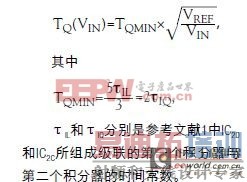

本电路输出Q上的输出脉冲宽度为:

虽然经此修改就能实现单稳功能,但图1中的IC 1、IC2和IC3逻辑电路还增加了其它功能。增加的逻辑可确保发生器忽略那些在单稳态繁忙状态内到来的触发器脉冲。

这样, 发生器的积分器电容可以放电到接近0V,误差不大于0.4%,即使是在超过1/[TQ(VIN)]值的相对高的触发器频率。因此,某个输入电压的输出脉冲宽度是恒定的,哪怕触发周期非常接近或小于输出脉冲宽度。

IC1和IC2组成的子电路产生一个RST(复位)信号,其尾沿决定了一个单稳运行周期的结束。在Q输出从低到高转换以及RST信号从高到低转换期间,本电路中的RST信号禁止单稳态的重新触发。为此,触发器信号的时钟与RST信号在IC3中相OR(图2)。

图2,所生成RST逻辑信号的高电平防止在时钟输入端的任何低-高转换去触发单稳态,除非发生器的积分器以一种已确定的方式复位。

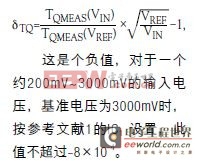

于是,在RST脉冲尾沿后, 下一个有效触发被使能。大约在二次抛物线电压VOQ达到其峰值电压VPEA K的一半时,RST脉冲的前沿出现。在VOQ跌至VPEAK / 2 以下时,RST脉冲的尾沿被延迟。IC1A输入端RS/CD/RD网络的辅助时间常数(RD+RS)CD定义了这个延迟。实验评测表明,输出脉冲宽度的相对误差为:

然后误差幅度上升,在输入电压为99.925mv时达到最大δTQ=-2.337×10-3。通过进一步降低输入电压,负误差的幅度下降, 在输入电压为9 . 9 1 5 m V 时为δ T Q= -1.113×10-3。在输入电压为3.08mV时,相对误差为正值,δTQ≈2.9×10-3。进一步降低输入电压,会使正误差快速上升,在输入电压为1.065mV时达到3%。但注意,输入电压跨度几乎是3000:1。触发频率为2Hz或200Hz。

在触发器频率为2kHz、200kHz和2MHz时,得到的脉冲宽度几乎相同。由于触发器频率变化而造成的脉冲宽度变化可与δTQ值相当甚至更低。对一个满量程输入,在输入电压等于基准电压时,测得的脉冲宽度为445.44μs。

用VOQ输出, 还可以将此电路用作一个精密的二次抛物线时基发生器;输入电压控制着发生器的速度。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:您真的了解设备供电的质量吗?

下一篇:晶振及其封装