- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

BU-61580芯片与PPC处理器的接口设计与分析

摘要:文章简要介绍了MIL-STD-1553总线的接口芯片BU-61580的功能及其特点,重点从硬件方面分析了RT模式下的几种不同的接口方式,具体分析了BU-61580与PPC系列代表处。理器PPC755如何进行硬件设计,如何能比较好的缩短共享内存的仲裁时间问题。

关键词:共享内存;仲裁;存储器接口

BU-61580是美国DDC公司生产的MIL-STD-1553B总线控制芯片,其集1553B总线协议的BC/RT/MT模式与一身,具有双收发器模块、协议处理器部件、存储器管理部件以及与不同微处理器的逻辑接口,内部还集成了一个4k字节的共享RAM。在进行总线通讯时,主机只需要初始化其内部共享RAM中的相关数据结构和需要发送的数据信息,对其内部的寄存器进行适当的编程,就可以自动地完成1553B总线的消息传输任务。对1553B总线的全协议支持以及灵活的使用方式,使得BU-61580在航空工程领域占领了很大的市场份额。PPC处理器是Motorola和IBM共同研发的RISC结构体系,具有高性能和低功耗的特点,主要应用在嵌入式系统中。PPC处理器分为MPC6XX、MPC7XX、MPC7XXX几个系列。

文章以PPC处理器PPC755为例,介绍与BU-61580协议芯片在RT方式下的硬件设计。

1 BU-61580协议芯片简介

1.1 BU-61580功能与特点

BU-61580协议芯片除了具有远程终端(RT)功能外,还可以用作总线控制器(BC)、总线监控器(MT),其内部功能极强,接口灵活、便于控制,有各种封装形式和供电电压供用户选择,是1553A/B等总线标准应用中较常用的接口芯片。其主要特点有:

a)支持多种总线通讯协议;

b)灵活的处理器/存储器接口;

c)先进的BC特性:重试、可编程时间间隔、帧自动重复;

d)先进的RT特性:非法化指令和忙位可编程,RT可工作在单一消息模式、可选择双缓冲器模式或环形缓冲器模式;

e)先进的MT特性:字监控选择,可选择为同时具有RT和MT功能;

f)单电源供电,体积小,功耗低

1.2 BU-61580与处理器的接口方式选择

BU-61580与处理器或外部存贮器接口非常灵活,可与8位、16位多种处理器接口,需要很少的控制逻辑电路。BU-61580与处理器共有3种接口结构形式:8/16位缓冲方式、16位透明方式、16位直接存贮器存取方式。

8/16位缓冲方式下BU-61580和处理器共享内部4K byte内存,BU-61580内部提供地址线和数据线的物理隔离措施,处理器访问内部4K byte内存时不需要外部增加隔离措施。8位缓冲方式主要应用范围是针对8位处理器,如8051、80186等微处理器。缓冲方式硬件电路简单,要充分利用BU-61580的READY(等待信号),但在其和处理器共享内存访问时的冲突仲裁的时间大约需3.7us,很大程度上限制了处理器的速度。

16位透明方式下BU-61580和处理器也可以共享内存,不同的是该方式下内存大小可外扩到64K byte,处理器访问64K byte内存时需要在外部增加隔离措施。硬件电路较16缓冲方式复杂,但传输的数据量较大,但仍然存在和处理器共享内存访问时的冲突仲裁的时间大约需3.7 us,很大程度上限制了处理器的速度。16位透明带双口 RAM方式,处理器和BU-61580通过双口RAM的两侧的A口和B口进行内存共享,处理器可全速访问双口RAM,访问的速度受双口RAM的限制。这种方式要求要求处理器访问双口的时间必须小于100ns,这样减少了BU-61580访问内存的冲突仲裁的时间,BU-61580在冲突下仲裁时间大约250ns。16位直接存贮器存取方式下由处理器而不是BU-61580仲裁使用地址和数据线。当BU-61580终端需要访问RAM的时候,它需要通过将/DTREQ(Data Transfer Request)信号变低向CPU请求数据和地址总线。当CPU完成当前指令周期,它通过将/DTGRT (Data Transfer Grant)信号变低来放弃使用中的总线。当ACE采样到/DTGRT变低,它将/DTACK(Data Transfer Acknowledge)信号变低表明ACE已经开始控制总线了。16位直接存贮器存取方式主要弊端是1553终端向RAM传输字或者一组字都必须占用处理器的带宽,处理器使用率低,其优点是可快速传输大量数据(外部RAM需要大于64K byte)。

2 PPC755处理器方案设计

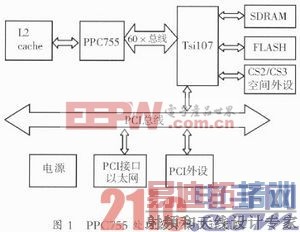

第三代高性能PowerPC处理器PPC755具有并行执行数条指令、简单指令的快速执行、流水线操作等优点,内部最高频率为300MHz,最快单周期可同时执行6条指令,峰值速度约500MIPS/300MHz。图1为PPC755设计方案,Tundra半导体公司Tsi107主桥片提供与PowerPC处理器、PCI外围设备及本地内存之间的系统互连接口。外设接口可配置在CS2/CS3空间,也可以在PCI空间。外设配置在CS2/CS3空间,其访问速度必须以所有外设中最慢外设的参数设置,快速的外设可以加等待时间满足CS2/CS3的存储器参数设置;外设配置在PCI空间,可以有效的将快速外设和慢速外设通过应答信号在PCI空间访问,对于非PCI接口外设,需要将PCI总线接口进行转换。

3 BU-61580与PPC755处理器典型接口\设计

根据PPC处理器设计方案可知,外设配置在CS2/CS3空间使用简单方便,但足不够灵活,并且访问外设的受到最慢外设的限制。这种设计方案不需要BU-61580的应答READY信号,采用BU-61580的8位/16缓冲方式下的零等待方式比较合适。[p]

外设配置在PCI空间可以解决配置在CS2/CS3空间中的问题,但是需要将PCI转换成ISA总线接口。这种设计方案采用BU-61580的16缓冲方式下的非零等待方式,16透明方式及DMA方式比较合适。在实际应用中具体选用BU-61580的16缓冲方式下的非零等待方式,16透明方式及DMA方式要根据具体系统架构来决定选择那种方式,以下对这几种访问方式作进一步的详细介绍。

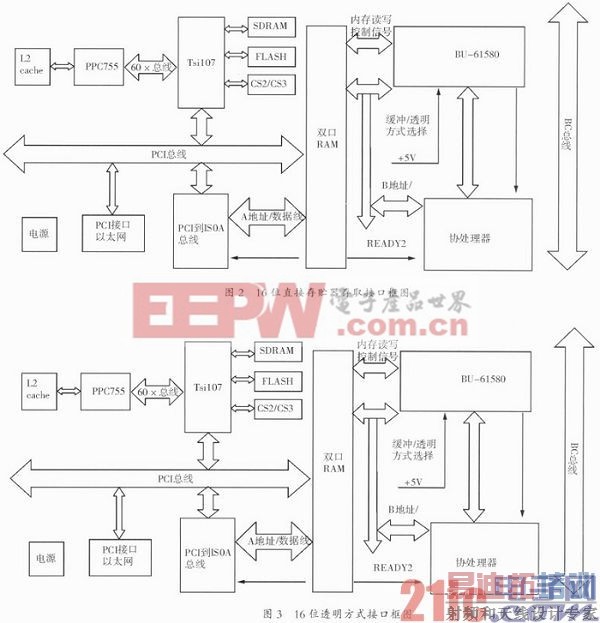

图2为BU-61580和PPC处理器DMA方式的典型接口电路。当传输的数据量大于64 Kbyte时缓冲方式和透明方式都不能满足要求,由于BC总线控制器和PPC755访问BU-61580不同步,必然会有对内存访问的总线冲突与仲裁问题,如果用PPC755处理器与BU-61580直接用DMA方式进行连接,PPC55的运行效率会受到严重的影响。图2中协处理器解决此问题,协处理器在中断产生后进行给双口RAM写数或者读数,避免了BU-61580芯片内部共享内存访问的竞争,PPC755访问BU-61580协议芯片的数据转换到与协处理器访问双口RAM的数据。这种方法对软件初始化BU-61580芯片RT内存管理比较灵活。

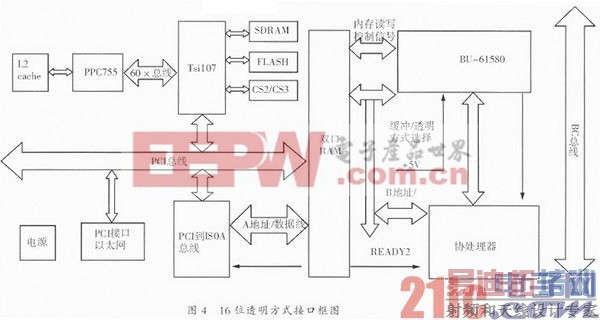

图3和图4为BU-61580和PPC755处理器透明方式和缓冲方式的典型接口电路,两种方式都需要将BU-61580的输出握手信号连接到PPC755处理器的READY信号。透明方式比缓冲方式的优点就是外部缓冲RAM可扩展到64K byte,缺点就是硬件上需要增加物理隔离,同时对外部缓冲RAM的访问需要BU-61580的内存读写控制信号参与。在传输数据量比较少,BU-61580内部的4Kbyte RAM足够用时,可选用16位缓冲器接口方式。

由于BC总线控制器和PPC755访问BU-61580不同步,必然会有总线冲突与仲裁问题,当发生访问共享内存冲突时,硬件上READY信号就会加入自动等待。这两种接口设计方法可以将INT中断信号连接到PPC755处理器的中断控制器上,在中断服务程序中处理数据,但中断对PPC755处理器开销比较大,一般不推荐直接使用。通常采用定时查询的方式,可以利用BU-61580RT提供的全局双缓存存储器管理机制,通过1#配置寄存器的第13位(CURREENT AREA B/~A)来选择激活部分。这样,在任意时刻,有一“激活”的堆栈指针、堆栈区域、查询表以及若干数据块用于1553消息处理,另外一套数据结构处于“非激活”状态。“激活”与“非激活”RAM区域都可被主机程序访问。

4 结束语

本文介绍了BU-61580芯片RT方式下与PPC755的几种存储器接口方式。根据处理器的架构和系统的实际应用对几种存储器接口方式进行了分析说明,文中提出的几种接口方式已经在实际工程产品中得到应用,具有一定的推广和借鉴意义。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:通过驱动器IC及输入检测机制来降低能耗方案

下一篇:晶闸管烧坏的真实原因解析