- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

在半桥谐振转换器中提升次级端同步整流器功率效率的控制方法分析

温室效应和日渐枯竭的地球资源使得功率电路设计中的节能要求变得越来越重要。设计人员正在寻求效率更高、功耗更低的解决方案,以期减少不必要的能量损失。利用谐振电感和谐振电容的LLC 谐振转换器,使用零电压开关(ZVS)或零电流开关(ZCS)可获得更加高效的解决方案。虽然LLC谐振转换器具有更高的效率,采用不连续模式(DCM)或临界导通模式(BCM)工作的次级端MOSFET的电流可能引起功率损耗。本文将讨论如何使用次级端同步整流器电路来降低功率损耗,探讨使用次级端电流使MOSFET同步导通和关断的控制方法,以及使用LLC初级端栅极信号来控制MOSFET的电压和导通时间的方法。

I. 前言:半桥LLC转换器

为了获得更高的功效,与200W到800W双管正激转换器相比,LLC谐振转换器的初级端MOSFET能够轻易达到零电压开关(ZVS),以期节省能量,并且获得更高的效率。此外,LLC谐振转换器使用独特的部件,能够省略次级端的储能电感,优于双管正激转换器的方案,并减小在印刷电路板上的占位面积。由于LLC谐振转换器的特性,将会以临界导通模式(BCM)或不连续模式(DCM)处理次级端电流,电流峰值将会大于双管正激转换器的电流峰值。下面将介绍几种使用不同的检测信号来控制MOSFET导通和关断的方法。

II. 同步整流器控制方法的分析

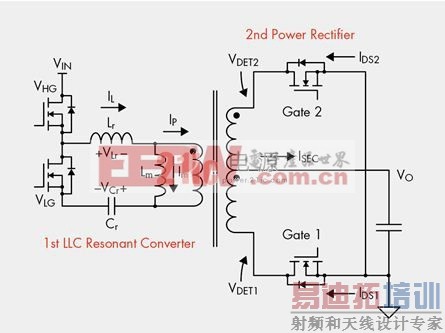

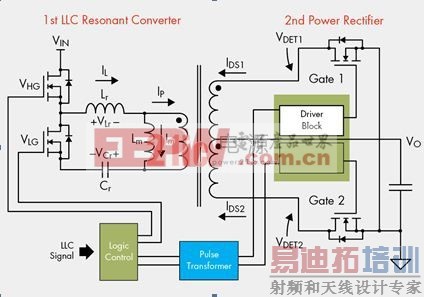

在LLC谐振转换器控制次级端整流器时,尤其是在关断的过程中,MOSFET导通和关断的控制定时是非常重要的。我们可以使用检测LLC谐振转换器初级端或次级端的电流或电压信号的方式,来确定MOSFET导通的区域。图1为LLC转换器的同步整流电路图。我们使用所示的电压和电流符号,介绍四种在次级端同步整流器关断过程中控制MOSFET的方法。

图1. LLC转换器的同步整流器电路图

1. 检测次级端电流(IDS1和IDS2)

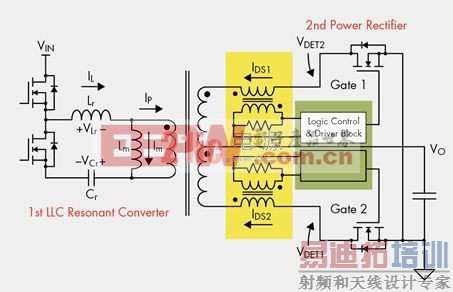

通过检测MOSFET的电流,可利用次级端同步整流器来控制MOSFET导通和关断的时间,如图2和3所示。由于需要检测IDS1和IDS2,需要增加一个电流互感器(Current Transformer, CT),从MOSFET信号中获取控制信息。与初级端电流相比,次级端电流要大些,所以电流互感器的匝数比很大。最后,设计人员可以使用电阻将分离的电流信号变换成电压信号,并将其发送至逻辑电路来控制MOSFET器件。

图2所示为使用两个电流互感器来检测电流信号,图3所示为使用一个电流互感器来检测电流信号的情况,在这个设计中,电路布局受到更多的限制,但是省去了一个电流互感器并且节省了线路板面积。

图2. 使用双电流互感器检测同步整流器电流

图3. 使用单一电流互感器检测同步整流器电流

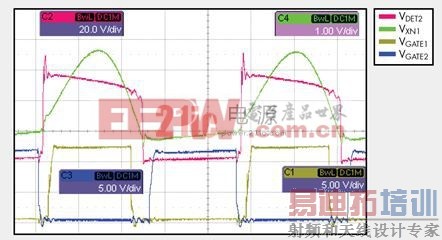

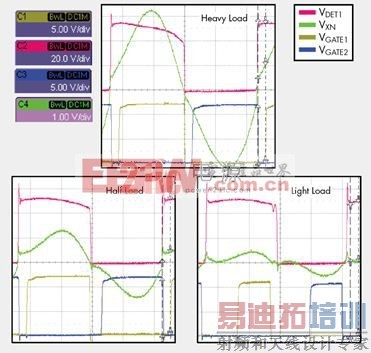

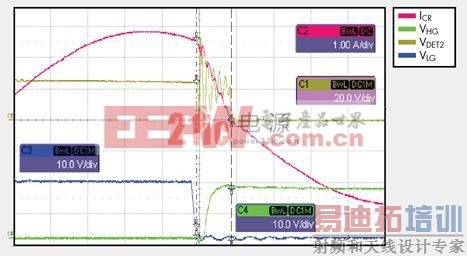

图4所示为每个相位的情况,该相位使用由电流互感器的检测电流转换而来的电压,以便控制MOSFET波形和GATE信号。设定的电平用作控制MOSFET导通和关断的基点。图5所示为一个电流互感器检测到电流后的两个相位,转换成电压以确定MOSFET导通和关断的波形。我们观察到电流互感器检测到的波形是交流信号VXN,并且具有一个不同的输出负载波形。在轻负载下,次级端电流集中在开关周期的终端,所以,控制MOSFET的GATE打开信号的时间会更短。如果输出电流继续降低,电流互感器检测到的电流将会减小,我们可以使用检测到的电平来确定在轻负载或无负载情况下关断同步整流器的时间。[p]

图4. 双电流互感器控制同步整流器的波形

图5. 单一电流互感器控制同步整流器的波形

虽然使用电流互感器检测电流信号能够控制MOSFET导通和关断的时间,但还是存在不足。通过监测流过电流互感器次级端的电流来检测信号,会少许增大电流互感器的电流损耗,略微降低SR的效率。如果是这样,在发生最轻微的过负载时必须关断同步整流器的功能,设计人员必需在两个电路相位反转和交替时仔细监测电流。

2. 检测次级端同步整流器电压VDET

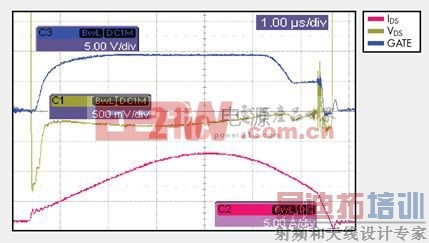

使用电流互感器检测次级端电流,可以方便地控制MOSFET,但为了避免电流互感器上的损耗,可以使用另一种检测方法。为此,在检测MOSFET导通时,利用RDSON上的电压来揭示MOSFET电流的直接比率。这样在MOSFET导通时检测了电压,并且提供了一种控制关断时间的方法。MOSFET导通定时使用了跨越MOSFET的体二极管。当次级端电流相位转换时,电流通过MOSFET,使其关断。使用这些条件来控制MOSFET的导通定时,MOSFET上的电压将会降低二极管的正向电压VF。如图6所示,当IDS开始通过MOSFET的体二极管时,MOSFET上的电压VDET为负,触发发出GATE信号来导通MOSFET。在GATE导通时,可以观察到VDET下降,电压为RDSON*IDS。

图6. 同步整流器的VDS波形

该检测方法可与使用电流互感器检测电流的方法相媲美,防止电流互感器之间和电流互感器上的能量损失,并精确地控制电流互感器的使用。这种方法最适合LLC次级端同步整流器。重要的是保证检测VDET 信号到控制电路之间的间隔不能太长,可能由于线路内电感的寄生效应造成信号的失真,此外,需要控制的信号会受到干扰。选择最低的MOSFET RDSON和最小的过载输出是控制MOSFET关断定时的简便方法。

3. 检测次级端同步整流器的导通周期

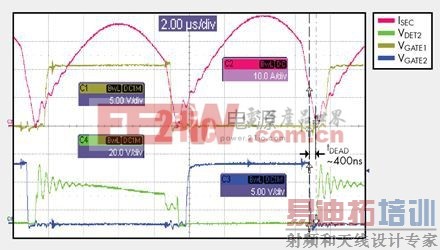

在MOSFET导通时,可以使用与检测V DS相同的方法来检测VDET电压。通过检测VDS导通时间,并且在MOSFET导通后VDET处于接近0V的低电压下,可以测量同步整流器的导通时间(tDETL),在这段时间内,DETL低于低电平(大约1~2V)。该信息用来确定同步整流器栅极针对下一个开关周期的关断时间。为什么能够使用这个功能,原因是LLC拓扑的高侧和低侧开关占空比是对称的,在稳定状态下,开关频率不会有大的变化。控制导通的定时使用了MOSFET的体二极管,MOSFET先导通,然后断开。

图7所示为这种控制方式。在过程开始时获取信息作为控制MOSFET关断的方法,这种方法使GATE较早关断,以防止由于某些原因而造成MOSFET晚关断。在MOSFET导通且受到噪声和连线的一些干扰时,这种方式比直接检测VDET上微小负电压的方式更加稳定。由于电流低至0A,tDEAD的周期(从GATE关断的定时到IDS的定时)将变长,减低同步整流器的活动性可以改善能效。

图7. 同步整流器的VDS波形[p]

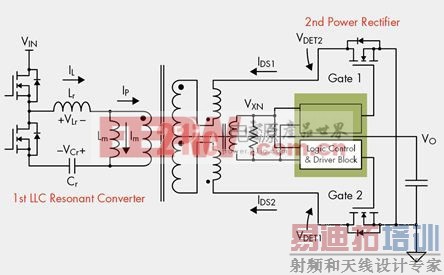

4. 使用LLC谐振转换器初级端栅极信号的同步控制

使用LLC谐振转换器初级端栅极信号的同步控制是最直接的控制方法。使用由初级高侧和低侧信号计算而来的GATE信号,并将结果提供给次级端,控制相应的次级端MOSFET的导通和关断。如图8所示,处理高侧和低侧的额外信号后,使用逻辑电路发送信号来控制次级端的MOSFET。注意,VHG和VLG的信号不能直接从计算导出,最有效的方法是使用LLC的信号来生成VHG和VLG信号,控制初级端的MOSFET。因为在大多数情况下,相应的次级端MOSFET需要早于初级端MOSFET关断,原始的LLC控制信号不能直接驱动MOSFET,必须发送一个新信号。

图8. 使用初级端LLC信号控制同步整流器电路

使用这种检测方法时必须满足两点要求:

A. 当在II区域中使用LLC时,由于可能出现谐振电流IL低于磁性电流IM,这会使IP为零并且造成初级端和次级端的去耦合。去耦合的主要条件是次级端二极管关断。所以,如果要改变同步整流器电路,需要在这一时间间隔内关断MOSFET。我们无法通过监测初级端LLC控制的信号来了解该现象何时出现,所以必须添加功能,早些关断SR,以阻止电流反向。

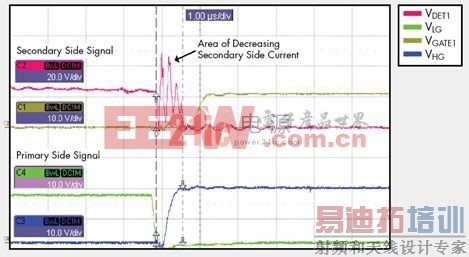

B. 当LLC系统工作于I区域时,从图9我们能够找出初级端GATE信号与次级端电流的关系。当低侧MOSFET关断时,次级端的相应电流还没有降到零,所以,虽然次级端没有出现相位立即改变的情况,但会发生相位置换的情况。工作于I区域的现象和相位置换时间的长度将会伴随过载的交换。因此,当使用初级端信号来控制同步整流器时,设计人员应增加功能,以推迟同步整流(SR)的导通和关断。这样会确保这种情况不会发生并且能够防止同步整流器受到初级端谐振电流的损坏。图10所示为正常工作的同步整流器波形。

图9. 次级端和初级端LLC信号的绕组电压波形

图10. 同步整流器波形和初级端LLC信号

III.结论

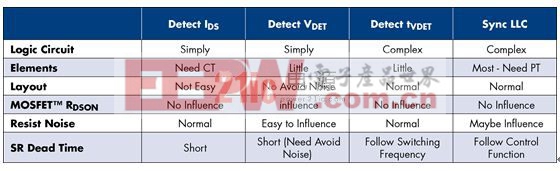

最后,表1给出了四种检测方法。从逻辑上讲,当MOSFET导通时,就控制而言,检测电流会比检测VDET容易。最复杂的方法是与LLC信号同步,这要求增加功能,以改善I区域和II区域的情况。检测电流需要使用电流互感器(CT),而使用初级端LLC的信号则需要电压互感器(PT)。因此,各种因素更加难以控制。在布局设计过程中,设计人员在确定电流互感器的电流检测方法以及MOSFET非常精确的RDSON电压时必需非常仔细。因为检测到的RDSON电压大约为1mV至10mV,所以更易受到干扰。采用通过PT发送同步信号的初级端LLC信号方式,要求设计人员考虑噪声问题。

如果同步整流器死区时间受到布局和已降低噪声的影响,检测RDSON电压的方法可以使得变化最小。由于交换频率的差异,检测VDET所需的时间将改变同步整流器的死区时间。从安全方面考虑,该功能时间是最长的。与LLC信号同步的方法将根据I区域相位移动的改善程度来确定同步整流器的死区时间。高效设计的最终考虑因素表明同步整流器的死区时间越短,其工作效率越高。因为增加电流互感器来检测电流会增加损耗,其效率将会低于检测VDET时间的方法。因此,在设计过程中,我们可以选择合适的检测和控制功效的方法。

表1. 次级端绕组电压波形和初级端LLC信号

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:电路设计模块化与设计重利用

下一篇:高能效LED道路照明驱动器设计