- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

序列信号发生器的设计方法及应用实例

摘要:阐述了使用移位寄存器和计数器设计序列信号发生器的各种方法,对每种设计方法进行了详细分析并给出了设计实例。运用构成的序列信号发生器设计了一个实用的彩灯控制电路,可实现彩灯有规律的亮灭。运用proteus软件对电路进行了仿真,并分析了输出结果。

关键词:序列信号发生器;移位寄存器;计数器;彩灯控制电路

0 引言

序列信号是一组特定的串行数字信号,在通信、雷达、诊断、检测等数字技术中有着广泛的应用。能够循环地产生序列信号的电路称为序列信号发生器。序列信号有多少位,就称序列信号长度为多少。例如:序列00011,序列长度为5。

在许多情况下,要求按照给定的序列信号来设计序列信号发生器。序列信号发生器一般有两种结构形式:一种是反馈移位型,另一种是计数型。相应的设计方法一般有两种:一种是由寄存器和反馈电路组成,另一种是由计数器组成。序列信号发生器在数字电路中有着较广泛的应用。在电子电路中,使用序列信号发生器可以构成彩灯控制电路,使彩灯有规律地亮灭。

1 用移位寄存器和反馈组合电路构成序列信号发生器

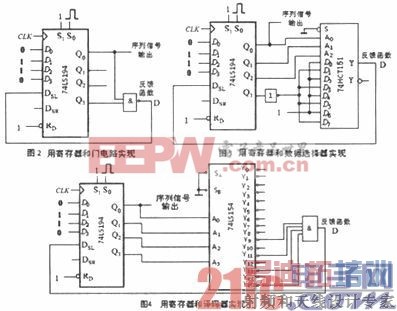

根据要产生的序列得到串行输入表达式,再根据此表达式得到串行输入的电路,这是一个组合电路,可以用逻辑门电路实现,也可以用MSI芯片实现。因此设计方案又分为两种:一种是用移位寄存器和必要的门电路实现;另一种是用移位寄存器和MSI芯片(如数据选择器、译码器)实现。

设计步骤如下:

第一步:根据序列信号的长度L确定移位寄存器的位数N,要求N满足条件2N-1≤L≤2N。

第二步:确定移位寄存器的L个独立状态。根据数据左移,画出状态转换图,检查图中的L个状态是否两两不同,如果是,则N可用;如果存在两个状态相同,则移位寄存器位数需要加1,得N+1。重新画状态转换图,再次检查状态图中的L个状态是否两两不同,如果是,则N+1可用;否则,移位寄存器位数再加1得N+2。重复上述过程,直到状态图中的L个状态两两不同为止,这时状态图中的L个状态就是移位寄存器的L个独立状态,这时的移位寄存器的位数才是最后的值。

第三步:根据状态转换图及每一个状态所需要的移位输入信号,列出反馈函数表,画出反馈函数的卡诺图,求出反馈函数的表达式。对于未用状态,做无关项处理。如果有无关项,还要求检查电路的自启动能力。

第四步:根据反馈函数的表达式,使用门电路,或者译码器,或者数据选择器实现反馈函数的组合电路。

例如,产生一个5位的序列信号01101。

设计过程如下:第一步,L=5,得N=3。第二步,取N=3,根据数据左移,可得到5个状态:011、110、101、010、101,在这5个状态中,存在两个重复状态,移位寄存器的位数需要加1,N=4,按照上述方法重新得到5个状态:0110、1101、1010、0101、1011,这5个状态各不相同,为独立状态,因此选择N=4,用移位寄存器74LS194即可。第三步,列出反馈函数表,如表1。Q0的输出即为序列信号0101。根据反馈函数表,得反馈函数D的卡诺图。化简时若将0000所对应的小方块中的d画在圈外,也就是化简时把它取作0,这意味着0000状态时左移输入信号D为0,因此当时钟信号到来时它的状态依然为0000,这样构成了无效循环,电路是不能自启动的。为使0000不再构成无效循环,应将0000对应小方框中的d画入圈中。卡诺图的化简方法应如图1,得。接下来,还应该检查电路的自启动能力。当电路中出现无效状态时,根据左移输入信号,判断若干个时钟脉冲作用后电路能否进入有效循环,经判断,电路可以自启动。

, D0=D2=D4=D6=1,在Y端顺次输出序列信号01101;如果用译码器74LS154实现,电路如图4。Q0Q1Q2Q3依次接译码器的A0A1A2A3,则![]() 。

。

[p]

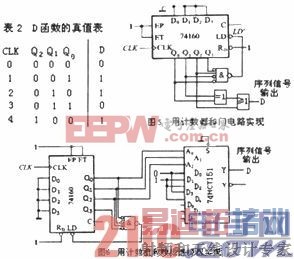

2 用计数器和组合电路构成序列信号发生器

如果序列长度为L,则首先将计数器接成L进制的计数器,然后根据计数器的状态和要产生的序列信号得到产生序列信号的函数,此函数可以用门电路实现,也可以用数据选择器实现。因此设计方法又分为两种:一种是用计数器和必要的门电路实现;另一种是用计数器和数据选择器实现,序列信号发生器的构成方法很多,在这些方法中,这是一种比较简单和直观的构成方法。

仍然以产生01101序列信号为例。

由于序列长度为5,首先将计数器接成5进制的计数器。这里用十进制芯片74160通过置入数据0的方法实现。计数器的5个状态为000~101。利用这5个计数状态和要产生的序列信号01101,列出输出函数D的真值表。根据真值表,得到输出信号的函数。该函数可以用门电路实现,也可以用数据选择器实现。如果用门电路实现,则需要画出函数的卡诺图(未使用状态作无关项处理),然后化简。化简后的结果为:![]() ,使用最少数目的门电路实现,函数可转化为

,使用最少数目的门电路实现,函数可转化为![]() ,电路图如图5所示。如果用数据选择器实现,选用芯片74HC1 51,可把五进制计数器的Q0Q1Q2接给数据选择器的地址端A0A1A2,把数据输入端D0~D4接为01101,以数据选择器的输出作为序列信号的输出端,则在时钟脉冲的作用下,电路依次产生所需序列01101。电路图如图6所示。

,电路图如图5所示。如果用数据选择器实现,选用芯片74HC1 51,可把五进制计数器的Q0Q1Q2接给数据选择器的地址端A0A1A2,把数据输入端D0~D4接为01101,以数据选择器的输出作为序列信号的输出端,则在时钟脉冲的作用下,电路依次产生所需序列01101。电路图如图6所示。

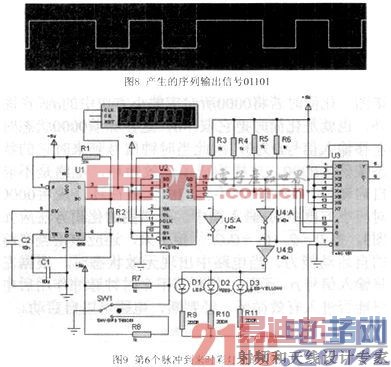

3 应用电路

使用这种电路可以驱动一路多个彩灯按照一定的规律亮灭,构成灯光控制器。在图3所示电路的基础上,设计出仿真电路,和理论电路不完全相同。Proteus软件中没有74HCT151芯片的模型,在下图中以74HC151代之。存在用TTL电路驱动CMOS电路的问题,TTL电路输出高电平下限值低于74HC系列输入高电平的下限值,解决办法是在TTL电路的输出端与电源之间接入上拉电阻以提高TTL电路输出的高电平。该电阻阻值不能过小,太小时,TTL门电路输出为低电平时流过三极管的电流过大,容易把器件烧坏;该电阻阻值也不能过大,过大会导致TTL门电路输出为高电平时上拉电阻上压降过大,引起输出高电平值的降低。综合考虑以上两种情况,取上拉电阻为1kΩ。设计的灯光控制器由555定时器构成的时钟脉冲信号产生电路、开关控制电路、移位寄存器、数据选择器以及灯光电路五个部分组成,可以驱动1路3个彩灯。图中Q0为序列信号输出端,驱动彩灯电路。为了使得Q0在驱动彩灯电路时输出高电平不致降低,采用U4:A和U5:A两个反相器串联,以减小该负载电路的驱动电流。开始仿真时,首先把开关掷向上方,S0=1,寄存器置入初始数据0110,然后把开关掷向下方,S0=0,寄存器中的数据按照指定规律移位。3个彩灯同时点亮,同时熄灭。亮灭的规律为:灭亮亮灭亮。彩灯亮灭的速度可由时钟信号CLK的频率控制。图中555定时器构成多谐振荡器产生频率为1Hz的时钟信号,因此彩灯亮和灭所持续的时间均为1s。时钟信号的仿真图如图7,周期为1s,占空比为63.83%。产生的序列输出信号仿真结果如图8所示。当第6个时钟信号到来时,Q0Q1Q2Q3=1101,此时序列信号输出端Q0输出高电平,彩灯全部点亮,电路的仿真结果如图9所示,图中还接入了频率计,显示时钟频率为1Hz。

4 结束语

序列信号发生器的构成方法很多,本文对其进行了详细介绍,结合具体例子给出了设计的全过程。并运用构成的序列信号发生器设计了灯光控制电路,分析和解决了电路设计过程中所遇到的各种问题,用Poteusr软件进行了仿真并分析了输出结果,使所介绍理论设计变成了实际应用。设计的灯光控制电路由集成芯片和门电路组成,电路成本低,具有很强的实用性,有一定的应用价值。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:NFC无线功能

下一篇:开发手机的全流程(

下)