- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于ECL逻辑器件的高频相移信号发生电路

随着电子技术的发展,高频相移信号在精密工程、电子、生物医学、通信科学研究的应用越来越广泛。现有的普通高频信号发生器常表现为信号不稳定或精度不高,而高性能高频信号发生器的价格昂贵,对于一般用户并非最佳选择[1]。

传统的相移信号发生电路采用锁相环与计数器构成地址发生器,在不同数据存储器下取数据实现,通过改变数据的存储位置实现信号的相移。这种方法输出灵活,但是由于锁相环输出频率的限制,仅适合于1 MHz以下的低频信号应用领域,且构成锁相环重要部分的计数器容易失去控制,同时相对复杂的电路结构也使整个电路的可靠性难以保证。近年来发展的基于直接数字频率合成DDS技术的高频信号发生器能实现频率在40 MHz以上的相移信号输出,相移分辨率可达到0.01°,但该类产品均未给出相移不稳定性指标[2]。另外,该类高频信号发生器均为国外产品垄断,价格昂贵,且硬件电路复杂,体积较大,不易携带[3]。因此,自主开发便携式、高稳定、低信噪比、低成本的高频相移信号发生器具有重要的技术创新价值。

针对上述高频相移电路存在的问题,本文提出了一种基于可编程ECL逻辑器件的高频相移电路。利用ECL信号上升沿和下降沿时间短(100 ps)、工作频率大(>GHz)、相位噪声小的优点以及ECL可编程逻辑器件输入/输出信号频率可编程的特性,实现的高频相移电路具有频域宽、输出信号频率编程可调、输出信号稳定、步进相移值可调且电路面积小、成本低等优点。

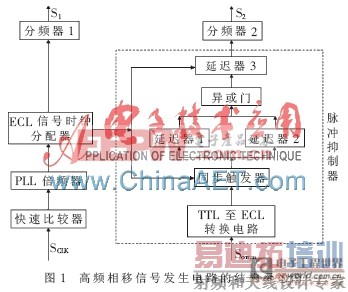

1 高频相移电路结构框图

高频相移电路包括快速比较器、PLL倍频器、ECL信号时钟分配器、脉冲抑制器和分频器,其结构示意图如图1所示。快速比较器将外部时钟信号转化为方波信号;PLL可编程倍频器将该方波信号倍频;ECL信号时钟分配器将该倍频信号分配至两路,一路经由数字分频器1直接分频,另一路倍频信号由脉冲抑制器抑制一个脉冲(相应的相移为2π)后再由数字分频器2分频。分频器1和分频器2的分频倍数均为2-p(p为整数),从而分频器1的输出信号相对分频器2的输出信号有2π/2p的相移。

相移原理图如图2所示。对于频率为fHF的高频数字逻辑ECL信号,用ECL逻辑器件抑制一个脉冲,则相应有2π的相移产生;将该信号二分频后,相移量为π。因ECL信号频率可分频为2-p倍,则在频率为2-p×fHF的信号处有值为2π/2p的相移信号产生。

图1中的脉冲抑制器由TTL至ECL信号转换电路、同步触发器、延迟器1、延迟器2、异或门电路、延迟器3组成。其工作原理如图3所示,脉冲抑制触发TTL信号经转化电路转换成ECL信号,该ECL信号经由同步触发器与PLL倍频信号SHF同步。与倍频信号SHF同步的ECL信号同时发至延迟器1和延迟器2,延迟器1输出延时量为t1的延迟信号St1,延迟器2输出延时量为t2的延迟信号St2,信号St1和信号St2经由“异或门”异或,“异或门”的输出为脉冲抑制信号,该脉冲抑制信号的脉冲宽度等于倍频信号SHF的周期,即t2-t1=THF。每次外部触发信号的边沿均触发一次脉宽为THF的抑制信号,该抑制信号通过延迟器3来抑制倍频信号SHF,从而实现2π的相移,如图3所示。

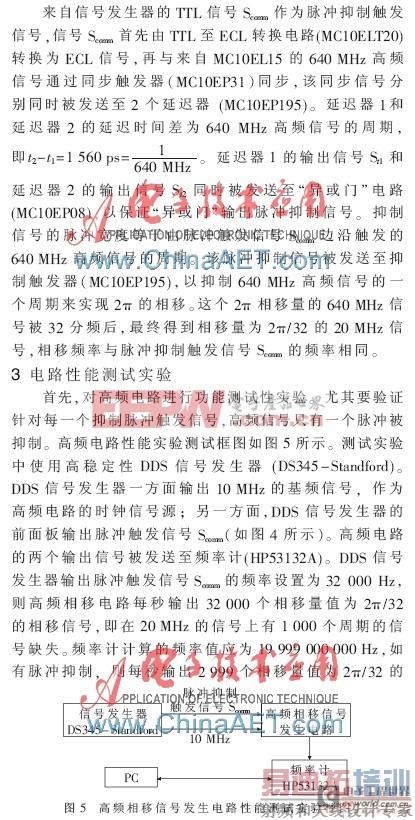

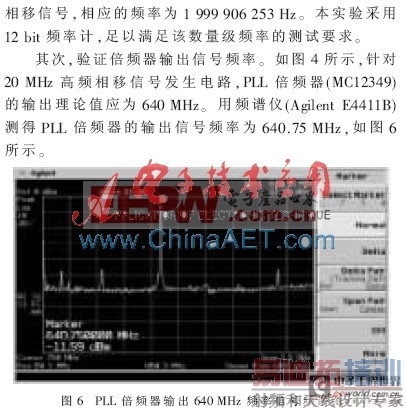

由信号发生器(DS345-Stanford)输出频率为10 MHz的正弦波信号Sclk,信号Sclk经由快速比较器(AD8598)整波成为方波信号,该方波信号经由PLL倍频器(MC12349 Motorola)倍频,倍频器(MC12349)的输出频率的范围为50 MHz~800 MHz,输入频率范围为10 MHz~20 MHz,输出频率FOUT与输入频率FXTAL的关系为FOUT=FXTAL×M/N,M和N的值可通过改变连接开关的值来改变。图4中,倍频器(MC12349)的输出频率为640 MHz,M和N值分别设置为64和1。ECL时钟信号分配器(MC10EL15 On-Semiconductor)将倍频器(MC12349)的输出频率640 MHz分配至三路,一路信号S3分配至低噪声分频器1(SP8402-Plessey),分频器分频倍数设置为32,则分频器1输出频率为20 MHz的方波;另两路信号S4 和S5分别被分配至脉冲抑制触发器(MC10EP195)和同步触发器(MC10EP31)。

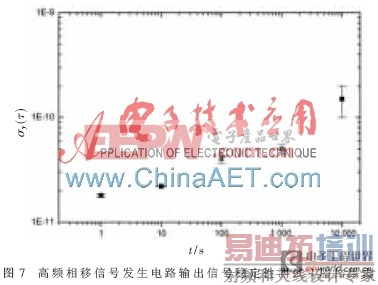

最后,验证高频相移电路输出信号的频率稳定性。频率稳定性测试条件为:信号的采集时间约为12 h,每次测试的积分时间为1 s。图7为高频相移电路中一个输出信号的实验结果图,另一个输出信号的稳定性也以同样方式进行验证。对实验数据进行相对艾伦方差计算得出,对于1 s~10 000 s的积分时间,艾伦标准方差值δy(ι)10-9。因此,该高频相移信号发生器输出信号的频率不稳定性可以忽略不计。

本设计实现了一种基于可编程ECL逻辑器件的高频相移信号发生电路,并验证了输出相移量为2π/32的20 MHz信号的频率稳定性。实验结果表明,对于1 s~10 000 s的积分时间,艾伦标准方差值

滓y(

子)10-9。该电路设计原理简单、可复制性强、电路体积小、相移信号噪声小、相移信号稳定、成本低。

参考文献

[1] 吴建辉.印制电路板的电磁兼容设计[M].北京:国防工业出版社,2005.

[2] CHASSAGNE L,TOPCU S.Highly accurate positioning control method for piezoelectric actuators based on phase-shifting optoelectronics[J].Measurement Science and Technology,2005,16(9):1771-1777.

[3] 陈伟.高速电路信号完整性分析与设计[M].北京:电子工业出版社,2009.

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:LED照明调光装置设计与实现

下一篇:单体蓄电池温度在线监测