- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

连接性错误一直无法解决

录入:edatop.com 点击:

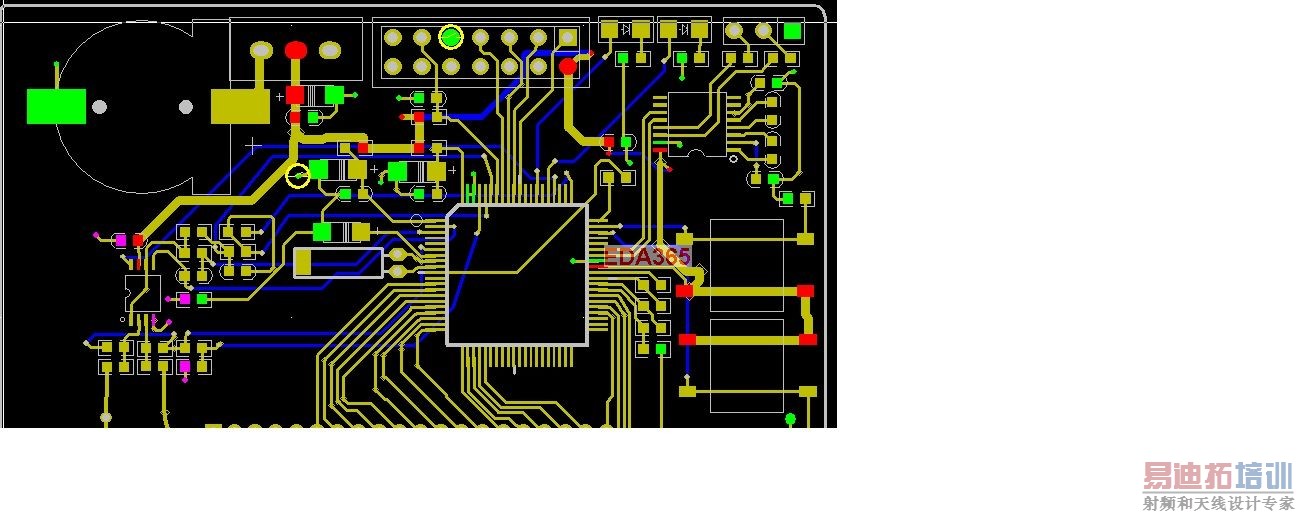

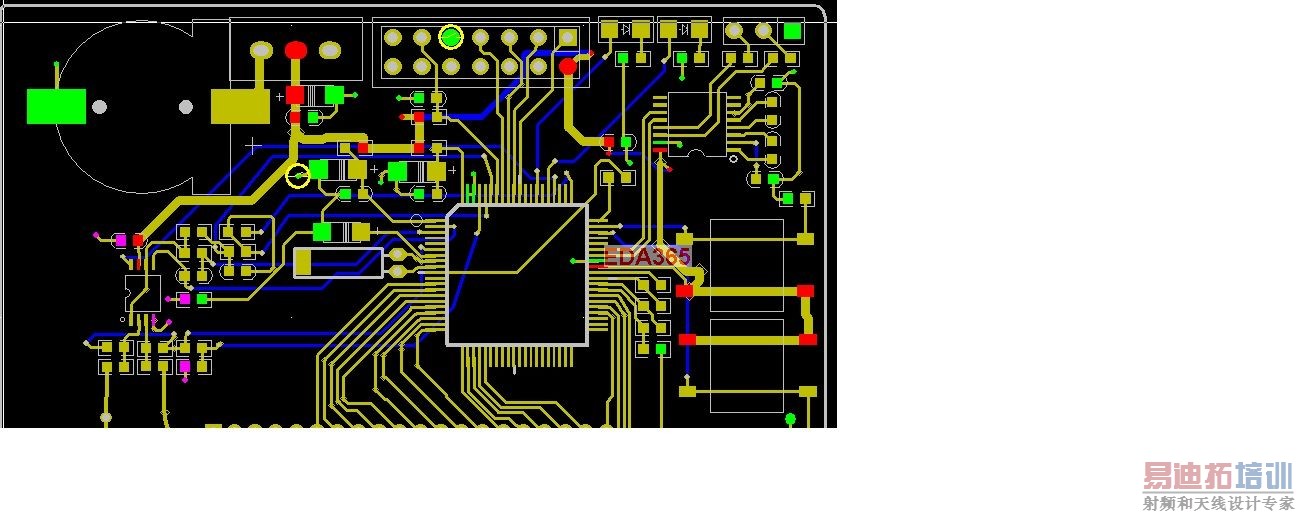

请问下,我连接性检查的时候发现这两个错误,但是无论我怎么改动再重新覆铜错误都不消失!或者错误变成了别的过孔了!

Isolated subnets for: GND

*** subnet # 1

HATCH OUTLINE(1894.35,1448.23 L2) C9.1 U2.79 C11.2 L1.1 C6.2 U2.78 VIA(1623.7,1490.75 L1) C7.2 VIA(1307.24,1460.75 L1) C5.2 VIA(1022.28,1482.68 L1)

*** subnet # 2

HATCH OUTLINE(1924.43,1507.83 L2) HATCH OUTLINE(2815.71,572.88 L2) B1.2 R22.2 C15.2 C17.2 R29.2 C16.2 VIA(1367.05,1749.37 L1) C1.1 R23.2 R19.2 C12.2 U2.53 U3.15 C18.2 R14.2 VIA(2159,1528 L1) VIA(2330.12,1587.48 L1) VIA(2709.61,650.87 L1) VIA(1965.31,1192.2 L1) VIA(2337.76,1819.49 L1) J2.1 VIA(2721,1841 L1) VIA(195,1866 L1) VIA(1219,1760 L1) JTAG1.9

Isolated subnets for: GND

*** subnet # 1

HATCH OUTLINE(1894.35,1448.23 L2) C9.1 U2.79 C11.2 L1.1 C6.2 U2.78 VIA(1623.7,1490.75 L1) C7.2 VIA(1307.24,1460.75 L1) C5.2 VIA(1022.28,1482.68 L1)

*** subnet # 2

HATCH OUTLINE(1924.43,1507.83 L2) HATCH OUTLINE(2815.71,572.88 L2) B1.2 R22.2 C15.2 C17.2 R29.2 C16.2 VIA(1367.05,1749.37 L1) C1.1 R23.2 R19.2 C12.2 U2.53 U3.15 C18.2 R14.2 VIA(2159,1528 L1) VIA(2330.12,1587.48 L1) VIA(2709.61,650.87 L1) VIA(1965.31,1192.2 L1) VIA(2337.76,1819.49 L1) J2.1 VIA(2721,1841 L1) VIA(195,1866 L1) VIA(1219,1760 L1) JTAG1.9

将原灌铜框删掉,重新绘制

我删除了几次重画还是有那样的错误!

那就将文件放上来吧.

my_pcb.rar

我修改过了一下的版本

终于知道什么原因了那些过孔在灌铜时被BOTTOM的走线分割开了。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

射频和天线工程师培训课程详情>>