- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

切换式电源的静电放电能力防制技术

【前言】

切换式电源产品在做验证时,经常会遭遇到ESD的相关问题,有时处理起来需花费非常多的时间,笔者从事切换式电源电路设计多年,希望能藉由之前ESD对策的经验与ESD的相关理论基础做个整理,让目前正从事或未来想从事切换式电源设计的人员对静电防制技术能有初步的认识。

本文章内容包括静电的介绍,切换式电源的ESD测试法规与测试方法,切换式电源的ESD防制观念,ESD防制方法与ESD问题解决方式等。

静电介绍

多数的物体皆会储存电荷,而所谓的静电,即物体表面的电荷分布不平衡,当正电荷分布较多时带正电,当负电荷分布较多时则带负电;当一个带电的物体靠近或接触到另一个带不同电位的物体时,彼此会有电位差,就会产生电子转移的现象,此现象称为静电放电,当彼此电位差太大时,会因此产生高电流而导致组件受损。

只要是容易累积大量电荷的物体,皆有可能成为静电放电的来源,大至大型机台,小至电子零件,涉及的来源十分广泛,而多数的电子零件都是带电荷的组件,人体也是优良的带电荷来源(如下表所示),因此电子产品很容易因人体的静电将其损坏。

切换式电源电路的ESD法规与测试方法

因人体是良好的带电体,很容易因人体的静电放电将电子产品损坏,因此安规就定义了一些ESD的测试规范与要求,而切换式电源电路的ESD测试规范是依据IEC61000-4-2,人体放电模型可由电容及电阻所组成,人体的等效电容容值约150pF,因此IEC便依此概念,利用一个高压电源对人体的等效电容充电,而串联的高电阻(50M~100M)是为了防止充电电流过高的电磁干扰,待充电电容储存到高压电源的电压后,由静电枪的放电开关(如图一的切换开关)来控制放电,在放电时电荷会经由一串联电阻(330ohm)放电到待测物(DUT, device under test),其等效测试线路如下:

图一

IEC61000-4-2所规范仪器校正时的测试标准如图二所示,用一铁箱(法拉第空箱)将示波器置于箱中,并用幅射吸收材置于铁壳内以防止干扰,静电枪由外部透过一个2ohm阻抗进入到示波器,即可量测放波形,其测试图与波形图需符合下面表一所示,放电波形必需达到0.7~1ns的上升时间到第一个放电电流的最高值,在30ns后仍能保持最高值电流的一半以上,在60ns后仍能保持最高值电流的1/4以上,才能符合IEC61000-4-2的规范。

[p]

图二

表一 IEC61000-4-2 测试标准电压/电流值

IEC61000-4-2 规范的放电方式分成两种,依安规申请的不同而有不用要求,规范有接触放电 (Contact Discharge)与空气放电(Air Discharge)如表二所示:

表二

ESD测试方式为:

1. 各测试点正负各25次以上

2. 放电间隔至少1秒

3. 充电电压的误差范围要在5%以内

而ESD测试结果可依不同状况做不同等级申请,如表三所示:

表三

切换式电源的ESD防制观念

在开始介绍防制之前,我们先了解一下静电放电的基面概念。

由电子学的观念,两个导体之间皆有一电容值,利用电容储能的概念可以解释电荷累积的情形,像两金属板的电容可由公式 , A为两金属板之间接触的面积,d为

, A为两金属板之间接触的面积,d为

金属板之间的距离,∈是两金属板之间的材质(介电系数)。

而电容值与储存的电荷(Q)及跨于电容间的压差(V),可由Q=C×V来表示。

电容中所储存的能量则可由 来表示。

来表示。

由上述公式可对于储存电荷,电压及能量大小有些许的认识。当静电发生时,电荷可能会快速的消失,也可能透过上述电容储能的概念被储存起来,当物体的静电累积到一定的量时,藉由后端所接的电路做放电。

[p]

在静电放电时所产生的高电压,电流,可能会对DUT(切换式电源)造成的影响包括:

1) 讯号失真:在IC或电子电路里,可能透过PCB板或组件,将静电放电释放的瞬时能量耦合到内部电路,造成讯号干扰,误触而造成讯号失真,像是保护线路误动作。

2) 组件损坏:针对半导体组件,像MFET,Diode等切换开关,可能会因静电放电所产生的高电压或电流击穿组件,或是连续的瞬时突波电流在P-N接面造成热效应损坏组件(heat breakdown),也有可能因距离太近,让电场耦合经由非预期的路径而造成组件损坏。

ESD防制方法

在做电路初期规划设计时,若能先将ESD相关对策放入,则能事半功倍,而在ESD一开始的防制部份,最重要的是建立疏导路径。

切换式电源供应器大多以绝缘材质的外壳密封,或是有铁壳做包覆,因此对外裸露的部份只有接地铁壳与输出导线,提供了静电放电测试时的测试点。一般三线输入时,需要从输出端开始预留一条疏导路径回到输入端的地,若是两线输入(输入没有地线),则需从输出端预留疏导路径回到输入侧的火线或中性线。

跨接于一二次侧的组件,包括光耦合器,Y 电容与变压器,当二次的电荷增加时,此三个组件会等效将二次侧的电荷回到一次侧,通常流过Y电容的电荷会较多,因其容量小(《4700pF),高频时的阻抗低,因此一般疏导路径会以Y电容两端定为一二次侧快速放电路径。

在所规划的疏导路径上要尽可能避开半导体组件,以防因电荷的累积造成零件的损坏。

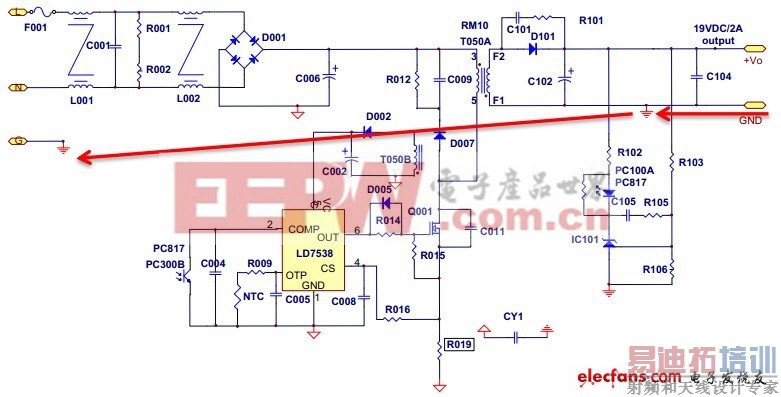

以通嘉科技PWM IC LD7538设计的返驰式切换式电源为例,图三红色图标为其疏导路径,且为三线式输入电源,若一次侧的地与二次侧的地直接相连,则电荷由二次侧输入时可快速藉由一次的地疏导。

图三

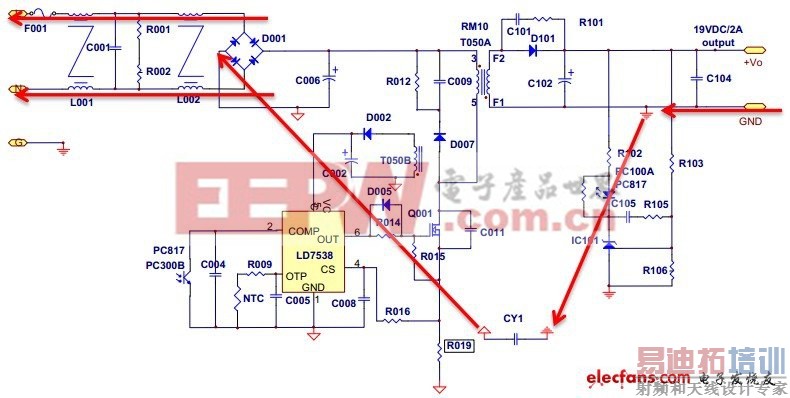

图四为二线式输入电源,若一次侧没有地的回路,则电荷需由输入的火线或中线做疏导,因此将二次侧的地直接接至Y电容二次侧的地,再将Y电容的地尽量的靠近桥式整流端的地,再回到火线或中线。

[p]

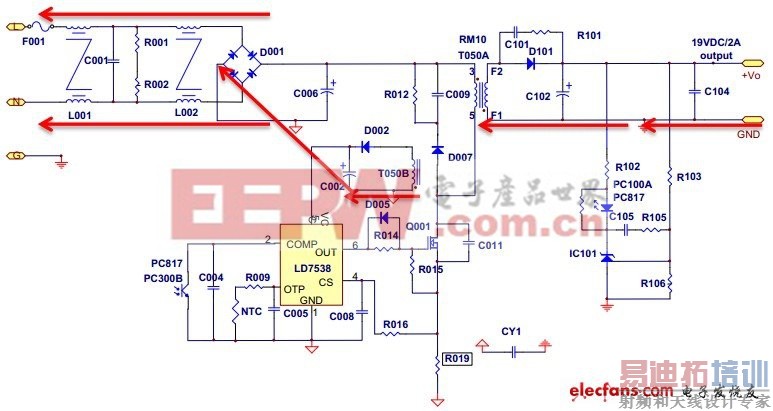

除了Y电容外,电荷也会由输出的地经由变压器二次侧耦合至一次侧,因此变压器初级侧的Vcc走线也需注意,如图五所示,将变压器的地直接接至Vcc电容的地后,直接接至桥式整流的地,再回到火线或中线,可让电荷经由初级侧的火线与中线快速将能量释放。

[p]

除了Y电容外,电荷也会由输出的地经由变压器二次侧耦合至一次侧,因此变压器初级侧的Vcc走线也需注意,如图五所示,将变压器的地直接接至Vcc电容的地后,直接接至桥式整流的地,再回到火线或中线,可让电荷经由初级侧的火线与中线快速将能量释放。

图五

除了一次侧变压器的地之外,变压器Vcc的正端也会耦合电荷,其会经过Vcc Diode再进入IC Vcc的正端(图六),若IC的Vcc太敏感或不够强壮即会造成IC误动作或损坏,一般加强的方法有:

1. 在靠近IC的Vcc pin对地增加一MLCC电容,吸收Vcc的突波电压。

2. 在Vcc进IC的路径上串联一Bead,抑制其突波电流。

3. 在Vcc进IC的路径上串联一电阻,抑制其突波电压与电流。

图六

在疏导路径上,我们会在Y电容两端会加一尖端放电的铜箔(如图七黑色框框所示),当初次级的电荷电压累积到某个电压值时,可透过此铜箔做放电,一般经验值是1mm等于1KV,例如放电铜箔尖端的距离为5mm,即表示当电压高过5KV时,会藉由此尖端将电荷由次级侧回到初级侧,因此次级侧对初级侧的电压即可压制在5KV以下,如此即可增加次级的静电耐受性,一般Y电容两端的放电铜箔距离即为安规的最小空间距离。

另外,切换式电源供应器为了符合EMI要求,会在输入端放入共模电感,此电感的高频阻抗会阻碍电荷的放电,因此也会在共模电感的同相两端加一尖端放电的铜箔(如图七红色框框所示)来帮助电荷的移动。因为为同电位,所以两尖端的距离愈小愈好,只需考虑产在线不会连锡的距离即可。

[p]

图七

图八是反驰式电源供应器的电路板布线图,红色部分为GND疏导路径,由最右边输出的地点经由一跳线接至Y电容次级侧的地,再由Y电容初级侧的地直接回桥式的地,再回到火线与地线。棕色部份为初级侧变压器的地,直接接回大电容而不经过IC周边讯号的地,制造一条让电荷快速流过的路径。

图八

图九棕色标示为变压器Vcc正端,经由一二极管后串联一电阻再进到IC,此电阻即为压制突波电压/电流所用,而进到IC前再并联一电容做吸收突波电压所用。

图九红色标示为尖端放电点,分别在第一级EMI电感,第二级EMI电感与Y电容上,Y电容二侧采用圆形PAD放电方式。

图九[p]

ESD问题解决方式

先确认因ESD而产生之故障现象,一般来说,ESD造成的故障现象包括:

1. 机台有跳火的现象(不在规划的放电PAD上)

2. 机台进入保护模式(auto or latch)

3. 整个机台损坏。

A. 若机台有跳火的现象,一般为绝缘不足或距离不够所致,对策方式为:

a.1可先用Hi-pot做一二次侧的绝缘测试,将Hi-pot的电压慢慢的往上调整,当一二次侧的绝缘或距离不足时,即为产生跳火而致使漏电流超过10mA,Hi-pot机跳离。尤其是变压器内部或散热片与周边零件的距离,用此法可快速检测机台一二次侧之间的距离问题。

a.2将输入端的火线/中线/地线全部接在一起下地,然后再去测ESD(机台没开机),此方式是检测当有外部电荷进入时,是否电荷是依循规划路径在走,只在放电PAD上有跳火。用此方式可以在不伤机台的情况下(因没有开机)先确认组件之间的距离是否足够,若不够即会跳火。

a.3在ESD测试时,可关灯确认跳火现象是在哪一个部份,一般跳火可用方式为:

a.3.1增加热缩套管,加强绝缘。

a.3.2修改layout,增加组件之间距离。

a.3.3在跳火处涂上白胶,增加其绝缘强度。

B. 若机台进入保护模式,对策方式为

b.1先判断与此现象相关的电路部分,看哪一部份电路动作会导致此保护现象,然后先将此保护模式关掉。例如测试ESD造成电源latch,就先将IC 会进到latch 的功能先Disable,看是否为IC周边线路误动作导致IC进到latch。

b.2若不是保护线路问题,即可能为IC被干扰,对IC来说,操作电流或操作电压愈小的pin脚愈容易被干扰(pin脚呈现高阻抗),确认IC哪个脚位的操作电流很小,设法增加一小电容去滤波或在pin脚前端串联一电阻做干扰讯号的衰减,在切换式电源IC里,CS pin因操作电压较低,故较容易受干扰,因此CS pin的layout 要极为注意;另外,TL431的地也很重要,在规划TL431的地时,最好连接于疏导电路的后端(让大多的电荷先走过疏导电路再进入TL431的地),或于输出端并联一颗MLCC电容再接至此(让此电容做突波的衰减)。

b.3 IC 的所有脚位不可空接, 空接的脚位很容易受外来干扰而被误动作,需以电容或电阻连接至Vcc或接地来拉高或降低其电位。

b.4 IC的Vcc脚也可能因太大的突波而干扰IC内部运作,可串接电阻,并电容来减少突波。

b.5若仍无法找到保护问题,则需用隔离探棒同时量测gate与IC各pin之间的波形,确认是何pin误触IC进到保护模式。

C. 若机台整台损坏,对策为:

c.1机台会损坏表示电荷疏导不足,让电荷进入组件或IC造成损坏,先确认机台的疏导路径是否如之前所提,半导体组件不要经过疏导路径,而疏导路径的铜箔要尽量加粗来使电荷快速放电。

c.2可增加Y电容的容值,降低高频时Y电容的阻抗,增加流过此路径的电荷。

c.3 若IC有高压pin,可在此脚并联一电容来吸收突波电压。

c.4 有些IC的输入/输出端很容易被打穿,在设计上要极小心;输入即为Vcc端,前面有介绍可外加电容,电感或电阻来压制,要注意IC的Vcc绝不能超过其最大额定值,因IC的输出端有一个totem pole,而输出端与Vcc存

在一个上臂的MFET,若Vcc超过此MFET的Vds即可能打穿IC的Vcc至Vgate,让输出一直为高电位。输出即为驱动端,有时会因MFET较大的Cgd而让电荷经由驱动端灌入,可于驱动端串联一电感来抑制其突波电流,或增加一电容对地来吸收突波。

c.5注意组件的选择与layout,对ESD的高频线路来说,寄生电感的影响非常大,在layout 时要将power trace(大电流在走动的线路)布的愈粗,愈短愈好,以减少其寄生电感;而在组件的选择上,侦测电阻也尽量要选用无感电阻。回路上的电感愈大,其感应的逆向电压也愈大,此产生的逆向电压有可能导致IC损坏。

c.6若仍找不出损坏的原因,可用一外加TVS(速度较快),并接于可能发生过电压的地方做限压,或并联一二极管作负压的放电。

结语:

ESD的防制其实重点在于放电路径的规划与相关原理的了解,只要在一开始做电路设计时有先考虑ESD快速放电路径,问题就可以解决一半。而相关原理则包括了解静电测试时的标准测试线路(一个150pF的电容与330 的串联电阻),

电荷公式Q=C×V与能量公式 ,

,

当电容充满电压并对待测物放电时,待测物上有哪些路径会让电荷走过?哪些组件可以帮助电荷放电,哪些组件会妨碍电荷放电,易受干扰的组件要如何接到讯号源而不受ESD干扰等,利用串联电阻抑制突波电流与电压,串联电感抑制突波电流,并联电容抑制突波电压等方式,可改善大部份ESD造成的干扰问题。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:拆解:变频传动细节观

下一篇:电位器在电路中的主要作用