- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高性能结合尺寸、重量与功耗的革命性突破

介绍

当今复杂的雷达与航空电子系统要求高处理性能,但同时又面临着小尺寸、轻重量与低功耗 (SWaP) 限制。驱动这些系统的功能都属于信号处理密集型,因此高效实施在高性能低功耗小型处理器上执行的数字信号处理 (DSP) 算法,能够为它们带来极大的优势。此外,这些系统还具有不断提高的设计与数据使用需求。为了满足 SWaP 的效率与自适用性需求,可编程 DSP 与片上系统 (SoC) 现已成为处理平台理想选择。它们能以极低的功耗为雷达与航空电子设备,以及雷达与航空电子常配套的软件定义无线电 (SDR)、影像以及视频应用提供无与伦比的信号处理功能。

要满足对 SWaP 高效率 SoC 不断增长的需求并非易事。这要求既要低成本地提供高性能,又要达到低功耗目的,以实现工作与环保目标。德州仪器 (TI) 基于 KeyStone 的多内核器件是实现 SWaP 效率的关键。它们可为 TI 领先 TMS320C66x DSP 内核进行多内核实施,以小型封装提供每瓦最低功耗。KeyStone 器件以不同的性能提供,在整个系列产品中实现了软件兼容。这可满足多样化需求,在设计时为未来发展预留空间,实现高效开发。

KeyStone 平台中的 TI TMS320C6657 与 TMS320C6655 器件是雷达与航空电子系统的理想选择。这些器件分别为引脚兼容型单内核与双内核 KeyStone DSP。

定点与浮点处理

使用多个数字信号处理器 (DSP) 内核是通过日益复杂的信号处理技术推动波形密集型应用发展的重要技术,可充分满足航空电子设备、雷达、声纳、信号智能 (SIGINT)、影像与视频处理以及软件定义无线电的需求。多内核功能将各种不断丰富的 AccelerationPac 与面向多内核 DSP 的开发工具进行完美结合,能够以紧凑的封装在极低的单位功耗性能下实现高性能。

航空电子、雷达以及相关应用需要多内核 DSP 来满足这些任务关键型应用不断提高的要求,包括更高的处理吞吐量、更精细的分辨率、更高的精度以及高级 I/O 的集成。许多这些功能都依靠浮点数学运算来获得所需的精度。TI KeyStone 架构能够逐指令地在单个器件内提供浮点或定点执行功能,可为设计人员带来高度的设计灵活性。浮点运算执行的时钟速率高达 1.25 GHz,这一速率通常只有定点器件才能达到。设计人员再也不必为获得浮点精度而牺牲性能,或采用分离式定点处理器和浮点处理器进行设计。

主要特性

l 基于 TI KeyStone 多内核架构,可实现出众的可扩展性与移植性 | l 完整的多内核共享存储器控制器 (MSMC) |

l 采用单个或两个 TMS320C66x DSP 内核 | l C66x 内核共享的 1MB 低时延 SRAM |

l 40 GFLOP/80 GMAC 的处理功能 | l TeraNet 片上网络互连可实现完整的多内核优势 |

l 在每个内核上进行定浮点运算 | l 多内核导航器为多内核 SoC 软件设计带来单内核设计的便捷性 |

l 定点速度下的浮点性能 | l 高性能 40 纳米工艺技术可提高成本效益 |

l 在 850MHz 至 1.25GHz 下的低功耗 | l 工业温度范围:-40°C 至 100°C 以及 -55°C 至 100°C |

l 业界领先的功耗/性能比 | l 完整的维特比与Turbo AccelerationPac 可提高通信应用 |

AccelerationPac

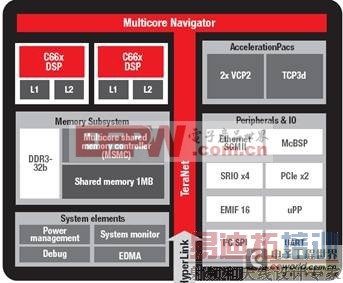

除优异的 DSP 性能外,C6657/55 还具有维特比及Turbo AccelerationPac,在充分利用每个内核 1MB L2 存储器与 1MB 共享存储器的同时,还可在低功耗硬件中处理通信与波形算法。这些 AccelerationPac 可独立于可编程内核运行,将 DSP 资源释放出来用于其它处理,从而可降低时延,优化软件开发。KeyStone 架构的多内核导航器提供一个基于硬件的抽象层,可将软件开发人员从底层硬件设计的具体繁琐工作中解放出来。多内核导航器的队列与描述符可用于自动将软件任务指向适当的资源,使可扩展性与资源池化成为处理器的整体功能。使用多内核导航器的软件可运行在任何 KeyStone 器件上,无需变更便可提供从一个 DSP 内核到多个 DSP 内核的可扩展性。这些因素综合在一起,可提供以 SWaP 为导向的应用所需的低功耗高性能。C6657/55 采用 40 纳米工艺技术,可在 1.25GHz 的频率下提供高达 80GMAC 和/或 40GFLOP 的性能。图 1 是 C6657 的功能图。

图1:TMS320C6657/55 方框图

高性能 I/O

一般情况下,这些系统不但需要与来自多个厂商的设备进行互操作,而且还要与其它原有系统进行互操作。C6657/55 提供高性能外设集,支持现代系统所需的高数据传输速率,并具有支持原有设计的高灵活性。这些外设包括:

双通道 PCI Express 端口,支持每通道高达 5GBaud 的 GEN2;

4 通道 Serial RapidIO

(SRIO),符合 RapidIO 2.1 规范,支持每通道高达 5Gbps 的运行;

支持与其它 KeyStone 架构器件高达 50GBaud 互连的 HyperLink 可实现资源扩展;

千兆位以太网 (GbE) 端口,具有一个支持高达 1000Mbps 的 SGMII 端口;

32 位 DDR3,具有支持达 1,333MHz 速率的 ECC 接口;

16 位外部存储器接口 (EMIF),用于连接闪存存储器(NAND 与 NOR)以及异步 SRAM;

8 位或 16 位双通道通用并行端口,每个通道都支持 SDR 与 DDR 传输;

2 个多通道缓存串行端口 (McBSP)。

C6657/55 可充分利用 KeyStone 架构中丰富的外设与 AccelerationPac,以紧凑的外形与低功耗实现全面的多内核优势。

SRIO、PCIe 以及 HyperLink 能够在多个 SoC 和/或 FPGA 之间实现高速互联。HyperLink 是 KeyStone 架构内部总线的接口延伸,能够在点对点高速互连中提供 50Gbps 的速度。HyperLink 提供低开销协议,支持与其它 KeyStone 器件或 FPGA 的高速通信与连接。它可提供一款能够满足当前雷达、SDR 以及航空电子系统可扩展性需求的解决方案。然而,SRIO 与 PCIe 则能够以较低的比特率实现基于各种标准的互连。

C6657 中的 32 位 DDR 外部存储器接口(支持 ECC)可提供支持 8GB 可寻址存储器空间的 1,333MHz 总线。TI DDR3 实施方案可降低相关外部存储器访问的时延,为高速运行这些应用相关的大量数据提供必要的支持。

尺寸与功耗

SWaP 是对上述任务关键型应用的主要要求。TI 长期以来始终致力于提供业界最低功耗的 DSP 与 SoC。C6657 不但支持双 C66x DSP 功能,频率在 1GHz 时功耗不超过 3.5 瓦,同时还能提供性能与外设的理想组合,满足市场需求。紧凑的 21x21 毫米封装可满足任务关键型应用对小巧外形的要求。C6657/55/54 器件还提供最新“超薄”封装(仅 2.9 毫米厚),可优化任务关键型应用对整体系统级封装的要求。此外,这些器件还支持 -55 至 100C 的更宽泛工作温度,这就是通常所谓的航空电子应用要求。

此外,C6657 还可支持软件定义无线电中最复杂的波形。VCP 与 VCP3d 加速器、内部共享存储器(达 3MB)与接口带宽可提供必要的高性能,能够支持和生成众多 SDR 应用中使用的最为复杂的波形。

雷达设计要求

现代雷达设计将信号处理功能整合在雷达系统的前端(激励器/接收器),这其中可能包括波形生成、滤波、矩阵逆转运算以及信号关联。此外,雷达系统还需要进行数学函数运算,包括递归最小平方与平方根运算。许多设计人员都在基于 C 语言的处理器中实施了这些功能(采用定点十进制和/或浮点运算)。这些类型的设计可充分利用 TI C6657 中提供的小型双定/浮点内核满足系统需求。

例如,在自适应阵列设计与标准空间收发器阵列处理 (STAP) 中,矩阵逆转是一个重要因素。矩阵逆转可根据雷达系统中使用的阵列规模,充分利用 C6657 DSP 提供的并行处理功能缩短时延,降低系统功耗。随着系统中阵列规模的变大,所需浮点乘法也随之提高。雷达系统设计人员最可行的设计方法是使用 DSP 和内部存储器模块实施这一功能。C6657 提供高达 40 GFLOP 的性能以及 3MB 的内部存储器,是该应用的理想选择。

结论

TI C6657/55 DSP 将外设与处理功能进行完美整合,可为系统设计带来众多优势,包括定点速率浮点性能、更高的系统灵活性以及更低的系统成本与功耗。器件上整合的外设可提供网络连接 (EMAC)、支持 ECC 的高速存储器接口、标准总线接口 (PCIe) 以及高速低时延点对点接口 (HyperLink)。该高级外设集可增强系统性能与可扩展性,再加上高集成度,可进一步降低系统成本。在需要运行雷达、SDR 以及航空电子应用要求的复杂计算密集型算法时,C6657/55 整合定浮点的数字性能可提供得天独厚的优势。

总而言之,TI C6657/55 DSP 不但可为任务关键型应用提供优异的 SWaP 性能,同时还可为整体系统缩减芯片数量与板级空间。

德州仪器公司 2012 年版权所有 |

| SPRY196 |

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...