- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

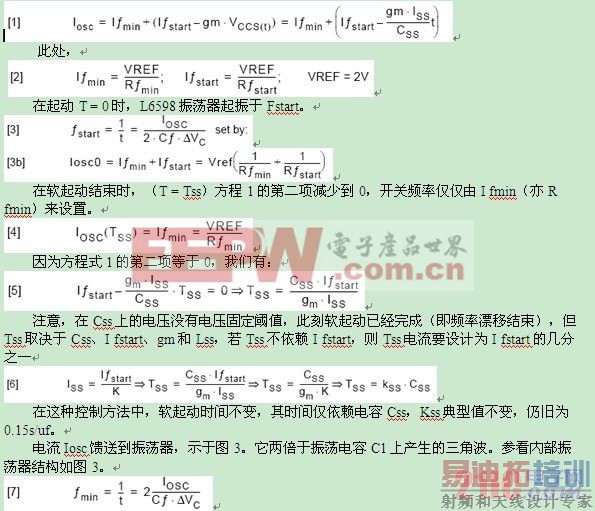

L6598脱线控制器用于谐振式变换器

因为更高的效率是可以达到的(高于传统的PWM),减少了高频电磁干扰,(谐振槽路利用了电路的寄生参数)

电源转换器市场对谐振拓扑的兴趣近来在增加。

事实上,这种拓扑允许更高的功率/重量比和低的元件功率损耗。

许多电源应用领域如适配器,电视,显示器,通讯机和汽车收音机都可以使用这种技术的转换器。

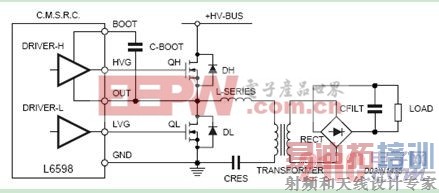

L6598设计成半桥式电路结构。

本文说明如何使用这种器件。最后将讨论所涉及的一些设计规则和应用要点。

器件特色描述

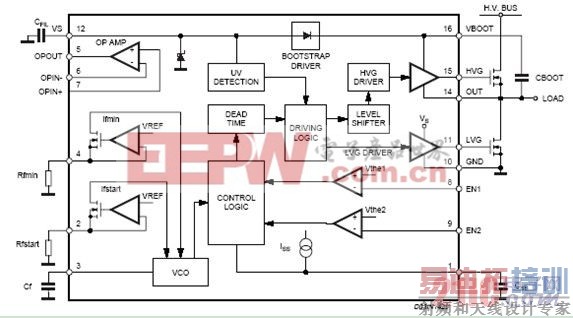

器件的内部电路图如图1,它是一个集成电路,用于实现脱线电源的控制技术。用于驱动功率MOS或IGBT。在半桥拓扑中,它提供的全部特点(如压控振荡器,软起动,运算放大器,及使能端。)需用最少的电路元件恰当的执行和控制谐振和SMPS。

图1 L6598控制IC 内部等效电路

该器件执行可通过元件与高压相接,它也能工作在从它供电的低压之下。封装为DIP16和SO-16。

最重要的特性:

高电压(直到600V)输入和降低dv/dt(150V/ns)于整个温度范围内。

250mA(源出)/450mA(漏入)的驱动电流能力。

欠压锁定。

精确的电压控制振荡器和软起动频率转移功能。

集成式升压驱动用于电容升压。

器件端子功能

pin1 软起动定时电容接线端,器件提供软起动特色,电容Css软起动时间根据关系式Tss= Kss* Css(tpy*Kss= 0.15s /uf)。在稳定状态,pin1电压是5V,在Tss间隙时间内,电流Iss(为If起动的函数)给电容充电,另外,Tss设置在Kss*Css,它只取决于Css值。见 pin2说明和数据表中定时的描述。

pin2 最高振荡频率设置端。将一个电阻接于这个引脚和地之间,以设置起始频率值,并固定于Fmin处。(Fstart>Fmin)在这个pin上的电压固定为VREF = 2V。所以,Rfstart调整Ifstart = VREF / Rfstart。Rfstart值建议不小于18-20kohm。

pin3 振荡器频率设置端。电容Cf与Rfstart和Rfmin一起设置Fstart和Fmin。正常工作时,该脚呈三角波。详见数据表的定时和振荡器部分。

pin4 最低振荡频率设置端。将电阻连接在该端接地。以设置Fmin值。该端电压固定为VREF=2V。所以,Rfmin设置的Ifmin电流等于VREF/ Rfmin,为精确设置频率,Rfmin值建议不小于20 kohm。

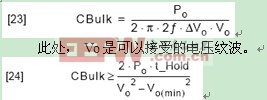

pin5 运算放大器的输出端。1M增益带宽乘积,这种运放是一种可以满足任何需要的无特征放大器。为完成一个反馈控制环路,该引脚凭借特有的电路可以接到Remind端子。

pin6 运算放大器的反相输入端。

pin7 运算放大器的同相输入端。

pin8 EN1,这个端子强迫器件处于锁闭状态。(与欠压状态相同)

高电平有效,典型的阈值电平是0.6V,这里有两种方法可 重新开始正常运行。

第一是降低电源电压到锁定阈值之下,然后再升高电压到正 确的供应值。

第二是激活EN2输入,EN1是为了大故障设计的,(例如短路或开路)

pin9 EN2,输入在1.2V开始激活,当激活时,强制一个软起动的程序。EN2电平普遍在EN1之上,它可以取消EN1的锁定。

pin10 GND,接地端子。

pin11 LVG,低边驱动输出。这个端子连到半桥电路低边功率MOSFET的栅极。将一个电阻接在这个端子和功率MOS 的栅极之间。用以减少驱动峰值电流。

pin12 Vcc电源电压端。这个端子连接一个电源滤波电容。内部箝制在

15.6V电源电压限制。

Pin13 空脚。这个端子内,外都不接,它为增加高压和低压电路的距离插入,增加的距离对绝缘性非常有益。

Pin14 高边驱动浮地参考端,该端必须紧密的接到高边功率MOS的源极。[p]

Pin15 HVG,高边驱动输出,这个端子必须连接到半桥的高边功率MOS的栅,串入一个电阻接在该端子和功率MOS之间,可用于减小驱动峰值电流。

Pin16 提升电压端,升压电容必须连接在这个端子和VS之间,专 利集成电路技术取代了外部高压二极管,这个特点系用高压 DMOS完成与低边同步MOSFET的驱动,详见数据表中升压技术的细节描述。

器件工作描述:

当提供给IC的电压达到UVLO阈值时,器件将开始工作。在提供的电压达到阈值之前,两支外部半桥的功率MOS将驱动器的低阻抗槽路切断。随着供电进入正常,电路开始运行,在第一个半周期中高边驱动器有效,所以升压电容将充满电荷。振荡器是一个电压控制振荡器,在Rfmin和Rfstar端选择合适的阻值,我们可以找出最低和最高工作频率的限制。器件提供软起动功能。在Css上接入一个延迟电容,这样就可以控制软起动时间。在一个周期内,开始时频率达到最大值,然后逐渐减小到工作值。振荡器通 过低边、高边栅驱动来控制功率回路,连接到外部功率MOS。频率的控制可在闭环控制条件下操作Rfmin做到。高、低边驱动有效的驱动电流能力,以保持通常450ma源出和250ma漏入,这允许许多不同功率能力的MOS驱动,以保持快速的开关转换。内部逻辑确保死区时间插在高、低边栅关闭和低高边栅开启之间,这个重要 的特点。使两功率元件很容易工作在零电压开关模式下,以减小晶体管开关损耗和电磁干扰(详见下面软开关部分)。建起的死区时间典型值为300ns,转换会在这个时间内全部完成。集成升压功能允许避开用外接的快速二极管来给升压电容充电(满足悬浮驱动的需要)。内部运算放大器在闭环控制以及保护功能上非常有用。

软起动和振荡器:

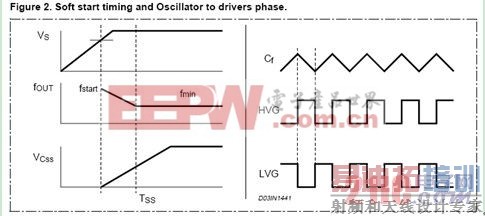

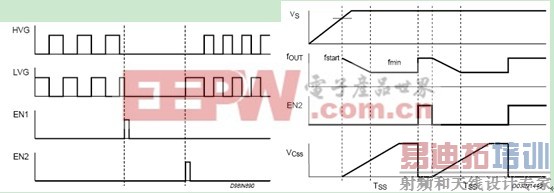

图2 软起动时间和振荡器波形

软起动功能由在一个周期的时间Tss内完成,Tss是开关频率从Fstart减为Fmin的时间,这个特点详细的说明如下(参见图2)。

在软起动时间内,电流Iss给电容Css充电,通常由一个电压斜波送到跨导放大器,见图2。这样,此电压信号转变为电流信号,并衰减为I fsyart。因此,该电流驱动振荡器并在软起动期间设置频率为:

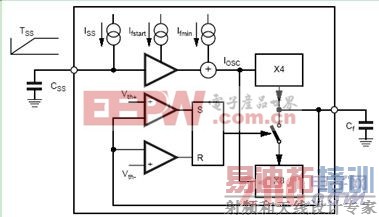

图3 振荡器电路

此处 Iosc=4*I R fmin。

Vc从峰值到振荡器低谷值约等于2.84V。

在正常工作下,计算振荡器近似频率值的关系式为:

![]()

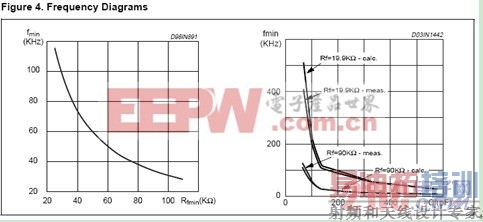

近似程度取决于频率值,但是它仍旧大于从30Khz到100Khz的范围。(图4)

图4 频率特性

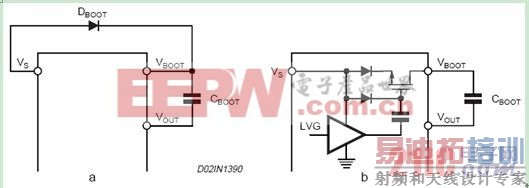

升压部分:

高电压部分由升压电路获得,这种方法一般需要高压快速恢复二极管,用来给自举电容充电,在器件中本集成结构取得专利,用以取代外部二极管。它由高电压DMOS实现。用串入一个二极管的方法与低边驱动(LVG)实现同步驱动。为了驱动同步DMOS,其VS电压必须高于电源电压。这个电压由内部充电泵获得。串接入DMOS的二极管避免其不希望有的开或关,二极管的插入防止了任何电流从V boot端子流入VS,防止内部电容泵没有完全放电 时,电源会快速关断。自升压式驱动插入了一个电压降落于电容 C boot的重新充电时间内,(当进行低边驱动时),随着频率增加,外接功率MOS尺寸也要增加。它是Rds on上压降和二极管阈值电压的总和。低频时,这种压降很小,可以忽略。无论如何提高频率时必须计及。事实上,这个压降会减小驱动信号的幅度,并且可以有效的增加外部功率MOS的R ds on(取消也如此)。考虑到在谐振电源中流过的电流,MOS减小了所增加的开关频率,通常增加的R dson不是什么问题,因为其功率损耗是可以忽略的。此处Qg是外部功率 MOS的栅充电电荷,下面的方程式对计算升压驱动的压降是有用 的。

图5 升压驱动电路

[p]

![]()

此处,Qg外部功率MOS的栅充电电荷,Rdson 是升压DMOS的导通电阻, T charge是升压驱动保持开通的时间(大约是开关频率的一半减去死区时间)

升压DMOS典型电阻值是150 毫欧姆,例如,使用一个具有整个30nc栅电荷的功率MOS,升压驱动的压降是2.5V,在开关频率200Khz,实际上,

![]()

在实践中,如果有效的压降在升压驱动上呈现出一个问题(特别在大功率MOS时)可以外接 一支二极管。防止C boot上的电压减少。

使能功能:

L6598具有两个不同的使能输入端,EN1和EN2(PING)适合多方面应用:

ENABLE 1(高电平有效)阈值典型为0.6V,当其被激活时,它可强迫器件处于闭锁状态,使得振荡器停振,并且HVG和LVG两输出都被切断,就如在欠压条件下。在这种状态下器件从电源取用很低的静态电流(250uA最大)。这里有两种方法重新起动器件,一种是减小电源电压到关闭阈值以下,然后再起动。第二种是激活ENABLE 2的输入端,锁住OV P功能,可以达到使用这个功能。EN2高电平有效典型阈值为1.2V,它重新起动的顺序以EN1已经预先激活,它将从锁存状态下重新激活。

图6 使能端子1的功能 图7 使能端子2的功能

EN2高电平有效,典型阈值为1.2V。它重新起动的顺序以及如果EN1已经予先激活,它将从锁存状态下激活。

谐振的应用:

在开关式的电源转换器中,谐振转换器可以根据波形与非谐振式区分出来。尤其是以转换器中的功率开关和寄生元件。实际上对照传 统的PWM方式,(典型为矩形/梯形)谐振转换器波形则包含了正弦振铃波形。谐振转换器技术可以应用在所有的转换拓扑(Buck,Boost)它可以将这几种的转换器分一下类。

——串联或并联负载式谐振电路

——固定的或可变的工作频率

——连续式或断续式的谐振方式

——全谐振、半谐振的谐振开关转换器

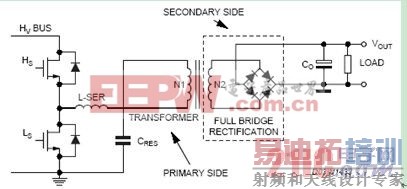

图8 半桥式电路的连接方法

这篇技术论文不可能讨论关于各种不同的拓扑,我们可以定义谐振变换器,它采用先进的网路谐振并且涉及零电压或零电流开关的可能性。零电压开关一般被认为在高频与高压应用时是最必要的,因为存在功率器件的寄生电容。

ZVS拓扑可以缓冲高电压应力,它涉及开关电压波形,但是,近来经济有效的方法是采用功率开关的半桥式连接,它提供 给两元件软开关特性,在开和关的上升下降沿处传输。整个谐振转换器很容易实现。

器件为基于半桥拓扑的应用而设计,以50%的占空比工作在变频状态,在这种形式的转换器中,输出参数的控制将由改变开关频率的方法来完成。

最流行的负载谐振转换器(SR串联谐振、PR并联谐振、LCL型串联谐振等等)都可以使用这种结构来完成。在目前的讨论中,我们通常是用一个变压器从主回路去给负载独立充电来实现。此外,由于器件的运行模式,连续式谐振变换器是我们感兴趣的拓扑,我们特制要参照LLC方式。[p]

图9:隔离的LLC变换器

谐振电路:

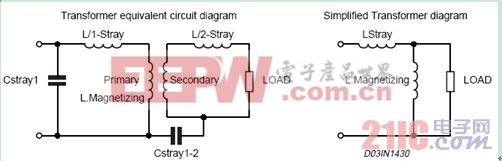

任何谐振电路包括电容和电感,由于我们实际要用变压器图10给出一个实际使用的变压器等效电路,它简化地展示出各个寄生参数。寄生电感可以在二次绕组短路连接时从初级侧测量出来。

图10 变压器等效电路

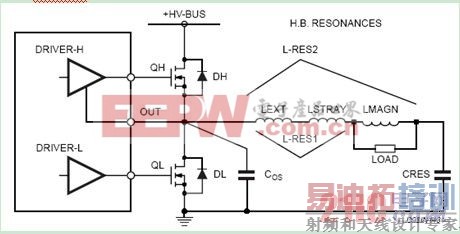

磁化电感是在变压器二次侧开始时从初级的测量值。寄生电容不予考虑。变压器的简化电路在目前的电路讨论中是可以接受的。我们现在可以定义一些基本的谐振电路和它们在应用中固有的效果。在图11中,我们可以注意到网络电路(从输出终点处可看到)由半桥图腾柱驱动,电路由漏感Lresi、变压器初级电感Lmag/Lload、和谐振电容Cres串连组成,我们把相串联的漏感Lres1和磁化电感Lmag叫做Lres2

Cos位于输出和地之间的等效电容视作驱动终点(相对功率开关结电容和电路的分布电容)。让我们开始引入基本的谐振概念, 涉及电路路径网Cos+Lres+Cres。此处,Lres可以在Lres1和Lres2之间变化,其仅取决于负载值。假设Cres远大于Cos值时我们刚好能够考虑串联的Cos+Lres。这个基本的谐振涉及软开关状态的运行。

图11 LCL 谐振式变换电路

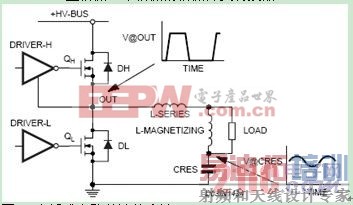

软开关:

依然参照图10。外部有源开关Qh在流过电感的电流达到0之前被关断(有效导通时间小于半个周期),电流被迫从输出结点处流出,最初将Cos上的电荷放掉,然后跨过电压阈值时的电压会通过二极管DL。在很短的时间(=300ns)之后,当QL的漏源电压接近 0时,固有的栅驱动器将被激活,并处在导通状态。同样的现象将在第二个半周期出现,关断导通的QL会产生输出槽路结点的交换,以使能量从Lres传到电容Cos的核,结果使上面二极管DH激活。

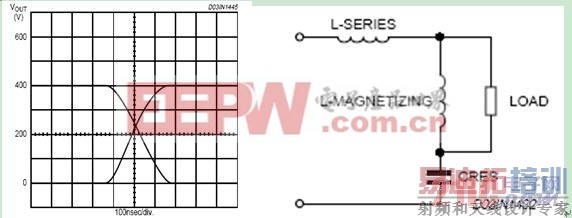

图12 软开关 图13 LLC谐振电路

传输的上升沿和下降沿可以被认为是上面定义的基本谐振部分,在图12中可以观察到输出结点处交换的正弦波形部分。用 这种方法工作可以是零电压开关,改善了系统的噪声干扰,因此,惊人的减小了开关损耗。为了工作在软开关状态,必须强制栅关断在电流流入负载之前,令其达到零电压或让它的极性反转,这可以很容易实现,需要很仔细,以便不使输出结点断开。

基本的谐振以及组成的软开关工作才是谐振变换器的实质,而没有包含在能量调整中。

为调整率改变频率。

由于软开关条件可以保证,让我们进行谐振电路的描述,本电路允许用 改变开关频率来控制输出。谐振路径是固有的电路。Lres+Lmag//Load+Cres(参见图13),它的谐振系用改变频率来调整输出到负载的能量。负载电阻(并联于磁化线圈电感)包括负载在二次侧折算到初级的负载。现在,我们必须考虑负载会有很大的变化(极限是短路和开路),另外,在实际的转换器中(图14),负载包括一个整流器部分和输出滤波器。因此,即使在单周期极限,负载也有很大的变化。Lmag可以看作在二极管导通期间与一个很低的阻抗并联,也可以看作在二极管关断期间与很高的阻抗并联(亦即在二极管阳极在降到低于输出结点 的瞬时电压)。

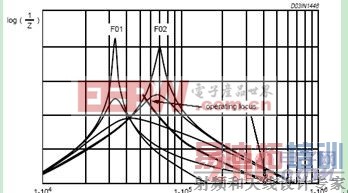

图14 简化的实际变换器

和以上论述相联,我们可以看到电路处在多谐状态的路径,也即是图15中描述的各个曲线,它可以监测到作为频率函数的导 纳变化趋势,此是为了对应不同的阻抗负载。这里有两种独立的 谐振峰值。第一个峰在频率低段时磁化电感是固有的(和Lext串连,如果只接一个)这是负载开路的情况。第二个谐振峰取决于串联电感Lsense(在负载非常重或整流器正在导通的情况下)。两种谐振均在能量传输到负载及其控制上起作用。我们可以开始讨论,假设磁化电感值Lmag太高,以至于它的电流对于我们感兴趣的频率范围内可以忽略不计。在这种假设下,很明显,最大电流将出现在F02谐振峰上。在低于F02谐振峰以下的频率时就不会谐振式工作。为了不失去零电压开关,也因为能量传输到负载的时间不能太长,从而为此增加或降低频率。在实际中,对于实际的变压器,其磁化电感不能被忽略(它的电感值不会太高)。无论如何,可以控制它的值以便让其工作在低于F02峰的开关频率下。[p]

图 15 多谐振

励磁电感 (在LCL拓扑中) 的控制,在能量管理上起到很重要的作用,它的值(以及它与Lsense的比率 ) 将影响多个应用功能。

假设负载断开,最大电流将出现在F01谐振的峰,它还涉及到路径L+C。磁性电感的值要显著地高于串联电感的值。一般来说,最低谐振F01峰主要取决于它的值。我们可以定义F01峰为最低谐振点,以便于记住开关频率必须不低于它的值。事实上,迫使半桥在较低F01下工作,串联电路存在一个电容性负载,这种条件在应用中是不能接受的,理由如下:

——在电容性负载中,零电压开关工作条件会丢失。有效功耗就会出现(或为硬开关)。

——在闭环电路中,传输功能会反转(当趋于谐振之下),会失去控制。

总结

它需要工作在曲线的“电感区域”以这种方法会使更高的频率加到谐振网络,所得到的功率会减少。值得注意的是,在深度电感模式下工作(远离谐振峰值)电流会从正弦波形变为三角形,而且需要很宽的频率变化去控制调整率。

相反的,尽可能接进谐振点工作时,对于给出的负载改变,频率变化将最小。

如果应用设计成尽可能靠近最低谐振点(F01)和第二谐振点(F02之间,已经证实初级电流在两个功率MOS之一的关闭时刻不应该太低,以便保证在所有条件下为实现软开关所需的能量。

L6598的功能和谐振对调整率的影响已经讨论过了。现在我们开始描述一些设计标准。

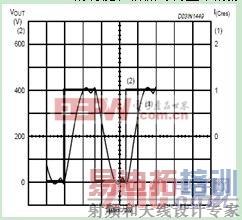

图16 Vout + I (Cres) 特性

设计准则和应用

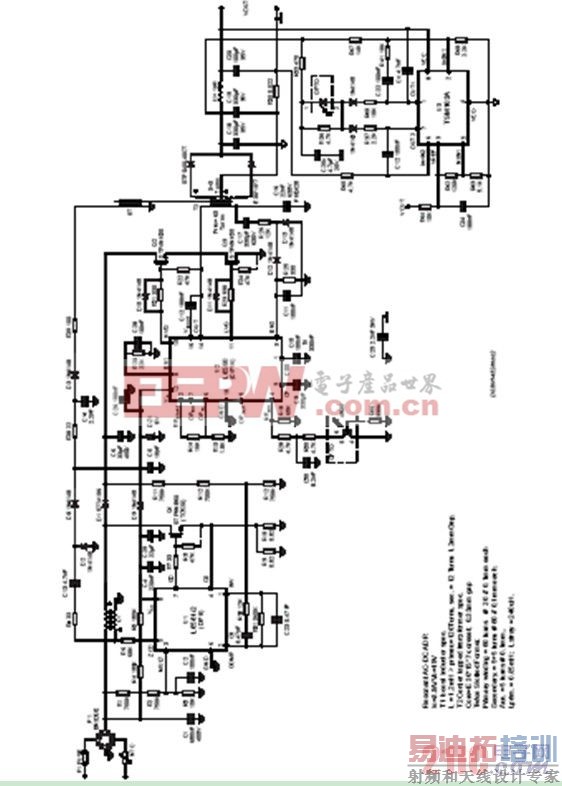

设计程序的描述参照样板来进行,它用来评估整个等效电路展示在图17中。

图17 L6598 组成的AC/DC 谐振变换器电路

对于PFC部分,仅作简单的描述。请参考专门的应用注意。

下面的讨论将仅限于对谐振式变换器。

设计过程

图 18 LLC谐振变换器

转换器方块电路可以分为几个大块,如图18所示。输出整流和滤波。变压器和谐振元件(Lres—Cnes)。半桥。驱 动器控制。目标规范是给出一个70W交流适配器的设计。下面是一些参数和要求。

——输出电压Vo=18V, 最大输出电流控制在Io=3.8A—4A

——宽范围交流输入电压85V—264V

——需要高功率因数,总线电压应该是360V—420V

基于这些值,我们可以开始设计输出级滤波器。

——二次侧的电流关系式(假设为近似正弦波形)。

![]()

输出滤波器和整流

需要使用高质量的电解电容设置极 限为1%,输出电压纹波是等 效串连电阻的函数(电容贡献可忽略)。

![]()

这是标准使用的两个电容(330uF ,WITH ESR = 75 msz 个,电容的内部功耗在最大功率输出时为140W,电压纹波约在240mv。

![]()

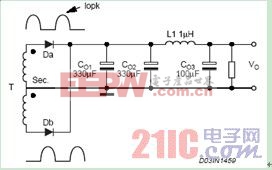

第二级L*C滤波器的布局接入可以有效的限制输出电压纹波,而不需要多个超过合理的高性能的电容。在本例的情况下,低价格电感就减少了高频率电压纹波,使之达到80mv(如图19)以下。因为输出电流/电压比率在这种应用中输出整流级可以呈现出更多的功耗。对于目前的应用,选择中心抽头线路连接,效率显著的改进,这样在每一侧输出整流器上只有一半功耗,使用这种解决方案,在二次绕组间需要两绕组很好的耦合。并且使电流波形能很好的对称。对我们的设计,选择STPS40L40CT是低压降功率萧特基二极管,为TO-220AB型封装(Vth = 0.28V,Rd = 0.0105ohm, BV = 40V)[p]

图19 输出整流和滤波

整流管上的功率耗散可以使用正弦模型来评估。@ Io = 4A

二极管上的峰值电流 I dp = 3.14*Io*Idp/2 = 6.3A Irms = 4.45A![]()

二极管的反向峰值电压>Vo*2 = 36V

变压器设计

LLC谐振结构需要一个谐振电感,(Lser)要将它串在变压器的初级还需要一个谐振电容(Cres) 这个电感起一个重要极点的作用,在能量传输或极重负载条件下,它的值控制着电流峰值。

由于初级通道将被用来提供作高频交流通道(会有很大的磁密浪涌 B),一个高质量谐振电感将需要用来限制磁心的功耗。在诸多实际设计中,变压器的杂散电感可以有效地取代任何外部谐 振电感(或减小它的数值)。我们采用这种解决办法,它可以省去部件并限制磁心功耗。漏感(Lstray)参数设计起来不太容易,通常它需要一些机械技巧, 以便得到一些有用的数值,不管怎样,还是变压器确定来得快。漏感值会足够恒定,变化范围也是有限的。

与此相关,第一步是选择磁心装置的尺寸,使用截面积(Ap)的规范。我们可以首先接近磁心两面积的乘积。所需的Ap可以用方程Ap1和Ap2找到。(我们用同一个公式做为标准半桥正向变换器)。

Ap = Aw*Ae 是窗口面积(Aw与型状相关)与磁芯截面积 (Ae)的乘积。

N.B对所选的谐振元件(电感及电容)及随频率的相应关系已设置好,其一可以很容易的参考附录A中讨论的变换器来完成。起始选择最小的工作频率,通常满载条件下为65KHz。

![]()

相对磁芯损耗限制,这里Kh = 4*10-5 Ke = 4*10-10 Fsw = 65KHz。对于现有设计AP1= 0.38 cm 4![]()

相对于磁饱和的限制。此处 K= 0.165 ,相对半桥变换器,Bmax.= 0.4T由变压器掌握的功率为P in。在现有设计中,将有AP2=0.17cm4。所需的AP将加大到现有数值的两倍。为满足电流的目标规范,我们选AP=AP1=0.38cm4。 选择磁芯形态为EE30(E30.15.7)在高频材料下,Ve=3.9cm3,Aw=0.8cm2 Ae=0.6cm2,Ap=Aw.Ae=0.48cm4。

变压器绕组:

为确定绕组,首先必须固定输入的直流总线电压值。由于在所讨论的设计中有PFC予调整级的需要,因此让起始固定电压总线范围在360V—420V。LCL谐振变换器的谐振可以用变压器的初级电感的予定值来实现。

第二个谐振电感容许工作在轻载条件下,并在给定负载范围内保持相同时间的高效率。在我们的经验中,用初级电感作为第二个电感的优点为其电感值与期望值之间的最佳比在3.5—7的范围内。

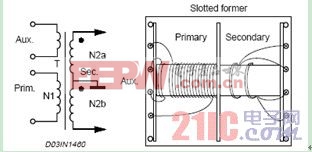

图20 变压器

初级电感值与期望电感值之比可以用骨架间隙来调整,而且可以在变压器磁心之间加入空气隙来调整(这就减少了磁化电感),为此我们选择两层骨架的形式,将初级,次级分开。见图20。绕组设计开始先计算所需的最小初级圈数。对此,有:

![]()

此处,Vin min = 360V B = 0.23T Ae = 0.6cm2

在AP情况,先求出AP1, B由式[17]计算。 [p]

[p]

此处,Pcv = Pt / 2Ve Pt = 1.3AP1*

作为替代,在此情况下,AP由AP2代替,Bmax由设计师固定0.4T。

选择初级圈数Np = 60。圈数比n = Np / Ns,由二次窗口及圈数定出。![]()

占空比 D = 0.5 选择n = 12,二次Ns = 5

*圈数比n可以足够高,高于[18]式,因为有Lmag效应。

**二次绕组相应为Ns = 5+5,这是由于中心抽头式整流。

为了限制趋肤效应,(带来固有功耗)Litz的导线解决方案被采用。

——20*0.1mm导线放于初级侧(0.157mm*2)

——60*0.1mm导线放于二次侧(0.47mm*2)

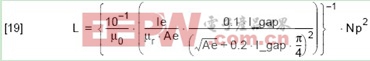

由于初次级侧绕组设定,我们需要固定变压器电感。公式[19]可以计算并很好地得出在磁心参数及气隙长度的条件下的初级电感量。它是磁心参数及初级圈数及气隙的函数。

此处,uo = 4*3.14*10-7 为空气的磁导率。ur为相对磁导率。

Le为磁路长度(cm) Ae为磁心有效截面积(cm),Lgap 为气隙长度(mm).

计算初级电感为mH。在本文情况下为L = 0.85mH

考虑漏感,在标准正向应用的变压器中不是很精确的。(主要因机械位置),近似值可以用下面公式得出:![]()

此处为270uH

这里,lw = 5.6cm bw = 0.5cm hw = 1.55cm

在此例的实际变压器中,漏感约240uH,(在变压器的二次短路时测初级得出)。如前所述,在磁心中插入一个气隙,可以控制初级电感及漏感的比值,选择气隙为0.33mm, 得到Lm/Ls = 3.5的比值。

谐振电容

对谐振电容的选择必须考虑其比率电流,对于低的电容值, 在实际上,电流能够被限制。在一个聚丙烯串联电容中,它通常可以找到一个合适的元件。另一方面,对给定的谐振值(见图21),见谐振曲线的纵剖面。(Q因子,其为(Lres/Cres)1/2的函数)这样,阻抗的改变随频率变。在我们的设计中,选为22nF / 630V PHE-100*C

图21 Q值的选择

功率MOSFET

功率MOSFET用于半桥需要耐压为500V选择STP4NB50。

相关参数可以用于计算

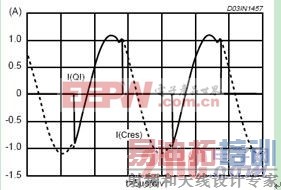

此处,I qpk为初极侧电流峰值。

由于Lm/Ls比值为变压器初极侧电流管理不可忽略的部分,它不会被传至负载。因此,用此式计算初极电流其结果将比测量值低得多。

测试结果见图22。

图22 I(Q)+I ces 特性

阻塞电容C-bulk

设计公式如下:

此处,T hold为所需的保持时间。Vo min为正常工作的最小电压。

选择阻塞电容的关键点是按如下顺序,承受电压,100Hz纹波下的电容值,保持时间,再看一下PFC文件。

选择C bulk = 33uF/450V 容许+/--9V电压纹波,没有固定任何保持时间。

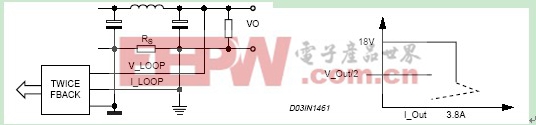

控制电路

输出电压及电流的控制与两个使用TSM103(双运放及基准)的环路有关。该元件还加上光耦。允许执行对输出电压和电流两者完整的控制。控制参数随频率的变化为流行的R f min,见器件工作页3。[p]

图23 输出V/I特性

自从输出控制不 能长时间保证重载情况,(如输出低于5V)在初级侧检测出的电流(C17,R26,D12,D13)并作为信号滤波器及馈送到L6598的 EN2端。超过阈值限制,软起动就会重新激活。

其它零杂

在设计中要考虑的少数临界点及相应调整。

——频率精度。实际频率由外部元件影响(Cosc的精度及其随温度的飘移)更多地,Cosc较低时,杂散影响必须考虑。(端子及PCB板电容)振荡精度会受下面因素影响,即基准中流出电流超过100uA时。

——PCB板布局会耦合噪声。检查噪声最好的判据是在Cf端(3pin)测量信号。为了确保正确的驱动周期占空比,此处应是一个同步触发波形。测试的另一点是14pin的电压,在自由运转期间,不要太近地电平。

(很少的几伏特)

功率因数部分

对谐振式应用,在我们的设计中,加入它还有如下理由:不管PFC是否必要。

前级的变换为传统的脱线式。由全波整流,电容滤波组成从AC线路得到未稳的DC总线。因此,连续的线路电压是长时间在电容上的低电压。这样整流器仅传导每个半周期的很小一部分。从主线的电流被拖出,然后一系列窄脉冲,其幅度为5~10倍的平均DC值。

从这里返回的损失,更高的峰值和均方根值电流从线路上拉出。AC线路电压的畸变,三相系统自然线路中的过流,在这所有之后,会是很差的电源系统的供给能量的能力。

这可以由测量整个谐波畸变项来得出。作为正常供电时,功率因数为实际功率和视在功率之比。从主干线上拖动的功率更直接。传统的输入级电容滤波只有很低的PF值(0.5~0.7)以及较高的THD(>100%)。国际正常标准需求要有高的功率因数来完成电源设计。

基于上述理由,功率因数校正为脱线电源管理中正在流行的部分。对高功率因数的预调整器,在输入整流桥和滤波电容之间插进去,会改善功率因数到0.99,供给电流能力也增加了,滤波电容峰值电流及谐波畸变都会减小。

再者,PFC有预调整的高压总线,它提供一个重要的优点。因为PWM工作在固定的直流总线上,这会使谐振式工作变得容易控制。

L6561是一个集成控制器,专用于PFC级,它采用临界型传导技术,并对低功率到中功率很适用。

PFC部分提供一个给出80W功率及400V稳定电压的设计。

AC主线电压可从85~264V。

对L6561细节描述可见AN966。

评价结果。

表格1

附录A

掌握谐振元件的方法是采用正常电压、电流。

最小工作频率设在65KHg,该频率可考虑一个好的折中的办法。既保持变压器的磁化设置的小尺寸。又防止高频问题。(如杂散参数开关损耗等)

让我们固定正常输出电压M=0.98 M=(VO*N)/(VIN(MAX)/2)

假设正常工作电流J = 0.2 J =(IO*RO)/(VIN(MAX)/2)

此处RO是特征阻抗 = (Lr/Cr) 0.5

谐振ZO可按下式计算 ZO =((VIN/2)2*J*M)/(VO*IO) ZO = 120

谐振电容是:Cr = 1/(ZO*W) Cr = 1/(110*2∏*65*103) = 20nF

谐振电感是:L r = ZO/W Lr = 110/(2∏*65*103) = 295mH

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...