- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的新型脉冲电源控制系统

录入:edatop.com 点击:

1 引言

在同步辐射加速器的电源设备中,旧的脉冲电源控制系统采用通用的逻辑元器件进行设计,电路复杂,调试过程冗长,系统稳定性不高,并且脉冲工作模式固定单一。所以对此进行了改造,采用了基于大规模可编程逻辑器件FPGA的设计方案,用VHDL语言来实现,大大缩短了开发周期,减少了电路体积,提高了系统稳定性,具有较强的实用性和升级性。同时系统的脉冲工作模式灵活,可单向正偏、单向负偏或双向偏转;控制电路能根据上位机送来的工作参数随时地产生一组放电触发脉冲系列,脉冲数可变,正负峰任意选择,脉冲间隔随意调节。

2 系统设计

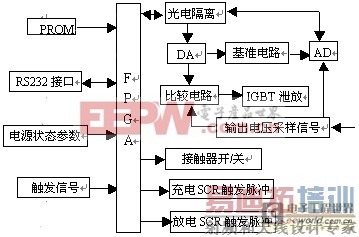

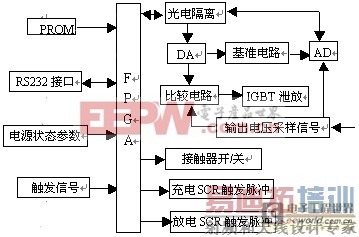

系统的主体结构如图1所示。上位主控计算机通过串口RS232实现实时监控,同时读取电源系统的故障信息。电源主控板以Xilinx公司Spartan #1520;系列FPGA器件XC2S200-5PQ208作为控制核心,具体实现电路包括PROM芯片XC18V02,12位A/D变换器Max178,14位D/A变换器Mx7534,电压参考模块MAX6350(5V)和MAX6325(2.5V),光耦TLP521-4和HCPL0631,运算放大器OP07和AD202,比较器LM339以及RS232接口Max232E等。

图1 主控板结构框图

[p] 主控板通过FPGA的可编程输入/输出功能块IOB,接收操作员的操作信号、电源的故障信号,将工作状态传送给上位机,将各种控制命令传送到电源。同时产生可控硅放电和充电触发脉冲;产生放电电压基准,控制IGBT开关管泄放;产生内触发信号,并对内外触发信号进行选择。

原系统的译码器、地址寄存器、数据寄存器、频率合成器、分频器、累加器、地址切换开关、数据切换开关等均集成在FPGA中,取代了用传统TTL器件搭成的复杂系统,简化了PCB设计。

3 FPGA内部功能框图及VHDL设计

在系统中,FPGA要具体实现的功能包括提供正负峰脉冲参考电压,读键盘和A/D的输出以及故障状态,控制系统输出脉冲正负峰的选择,控制输出脉冲数和电源接触器开/关,写A/D控制信号,进行内外触发选择,允许或禁止触发,设定时器初值,控制正常/故障灯亮等。

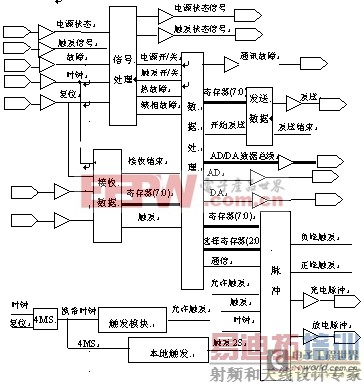

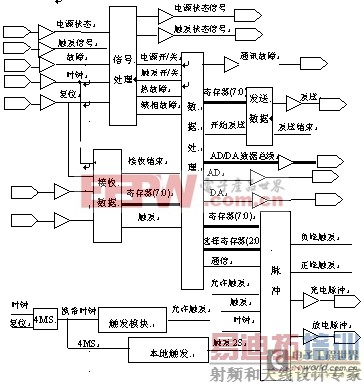

为此我们采用了模块化设计的思想,按FPGA要实现的功能,将其内部结构分成6个模块,每一个模块对应一个VHDL的设计文件(见图2)。VHDL语言是IEEE标准化的硬件描述语言,其覆盖面广,描述能力强,能支持硬件的设计验证综合和测试。这样设计的好处是有利于各功能模块的编写和调试,提高了软件的可维护性及可读性。

图2 FPGA内部结构图

下面给出各个模块的外功能简介:

(1) 信号处理模块SIGNAL-DISPOSAL.VHD

本模块主要接收脉冲开关铁电源的状态信号(电源开/关、控制开/关、触发开/关)、故障信号(热故障、缺相等),以及内部通讯信号(如内部信号输出、允许触发、状态/故障选择等),同时输出控制信号。

(2) 接收数据和发送数据模块RECEIVE-DATA-RXD.VHD 和SEND-DATA-RXD.VHD

这两个模块都有两个输入端口:时钟CLK和复位RESET,分别通过信号RXD和TXD实现与上位机之间的RS232通讯,波特率为9600bps,数据传送格式为11位,依此排序为:起始位(0),数据位(D0、D1、D2、D3、D4、D5、D6、D7),奇偶校验位,停止位(1)。同时与数据处理模块之间分别通过信号允许接收、接收结束、接收错误、接收寄存器 和允许发送、发送结束、发送寄存器联系。当发送结束为0时,发送寄存器送数,允许发送也置为1。

[p] (3) 触发模块TRIGALERT.VHD

这个模块输入端口设置为:复位RESET,触发TRIG(周期为2s,脉宽为10us),时钟(0.1us), 4MS(4ms)。在触发允许的情况下,输出信号为1,开始计数,如果没有触发就一直延续至1.8S,有触发就调用计数器10US,脉宽延续为10us,等1.8S结束后输出信号变为0,结束了一次触发过程。

(4) 脉冲模块WAVEGEN .VHD

本模块主要产生充电和放电脉冲。放电脉冲波形近似正弦波,振荡频率约454HZ(2.2ms); 充电脉冲与放电脉冲之间间隔延时4 ms。遥控状态下可调参数为正峰、负峰幅度,触发延时Td及间隔时间Tb,触发模式设置序列(即正峰、负峰的序列),一个周期内的波形个数最多为12个。Tb的调节范围为200ms-400ms,Td的调节范围为0-20ms,步长为0.1us 。该模块根据上位机送的模式序列及相关约定计算出各波形触发时间间隔即负峰到正峰T12、正峰到负峰T23、负峰到负峰T34等,在触发允许时,即送出相应的波形。

(5) 数据处理模块DATA-DISPOSAL.VHD

这个模块是系统的核心模块,主要承担处理数据的任务,其它模块都与此相互通讯。

4 系统功能实现

通过XILINX 的EDA工具软件FOUDATION的VHDL设计及仿真实现,这套系统能够满足设计要求,可以实现多种脉冲工作模式,并且系统运行稳定可靠。

参 考 文 献

[1] 徐志军等. CPLD/FPGA的开发与应用. 北京:电子工业出版社,2002.1.

[2] 侯泊亨等. VHDL硬件描述语言及数字逻辑电路设计. 西安:西安电子科技大学出版社,1999

[3] XILINX Foundation Series 2.1i 设计指南. 北京:清华大学电子工程系Xilinx培训中心,1999.9 .

在同步辐射加速器的电源设备中,旧的脉冲电源控制系统采用通用的逻辑元器件进行设计,电路复杂,调试过程冗长,系统稳定性不高,并且脉冲工作模式固定单一。所以对此进行了改造,采用了基于大规模可编程逻辑器件FPGA的设计方案,用VHDL语言来实现,大大缩短了开发周期,减少了电路体积,提高了系统稳定性,具有较强的实用性和升级性。同时系统的脉冲工作模式灵活,可单向正偏、单向负偏或双向偏转;控制电路能根据上位机送来的工作参数随时地产生一组放电触发脉冲系列,脉冲数可变,正负峰任意选择,脉冲间隔随意调节。

2 系统设计

系统的主体结构如图1所示。上位主控计算机通过串口RS232实现实时监控,同时读取电源系统的故障信息。电源主控板以Xilinx公司Spartan #1520;系列FPGA器件XC2S200-5PQ208作为控制核心,具体实现电路包括PROM芯片XC18V02,12位A/D变换器Max178,14位D/A变换器Mx7534,电压参考模块MAX6350(5V)和MAX6325(2.5V),光耦TLP521-4和HCPL0631,运算放大器OP07和AD202,比较器LM339以及RS232接口Max232E等。

[p] 主控板通过FPGA的可编程输入/输出功能块IOB,接收操作员的操作信号、电源的故障信号,将工作状态传送给上位机,将各种控制命令传送到电源。同时产生可控硅放电和充电触发脉冲;产生放电电压基准,控制IGBT开关管泄放;产生内触发信号,并对内外触发信号进行选择。

原系统的译码器、地址寄存器、数据寄存器、频率合成器、分频器、累加器、地址切换开关、数据切换开关等均集成在FPGA中,取代了用传统TTL器件搭成的复杂系统,简化了PCB设计。

3 FPGA内部功能框图及VHDL设计

在系统中,FPGA要具体实现的功能包括提供正负峰脉冲参考电压,读键盘和A/D的输出以及故障状态,控制系统输出脉冲正负峰的选择,控制输出脉冲数和电源接触器开/关,写A/D控制信号,进行内外触发选择,允许或禁止触发,设定时器初值,控制正常/故障灯亮等。

为此我们采用了模块化设计的思想,按FPGA要实现的功能,将其内部结构分成6个模块,每一个模块对应一个VHDL的设计文件(见图2)。VHDL语言是IEEE标准化的硬件描述语言,其覆盖面广,描述能力强,能支持硬件的设计验证综合和测试。这样设计的好处是有利于各功能模块的编写和调试,提高了软件的可维护性及可读性。

下面给出各个模块的外功能简介:

(1) 信号处理模块SIGNAL-DISPOSAL.VHD

本模块主要接收脉冲开关铁电源的状态信号(电源开/关、控制开/关、触发开/关)、故障信号(热故障、缺相等),以及内部通讯信号(如内部信号输出、允许触发、状态/故障选择等),同时输出控制信号。

(2) 接收数据和发送数据模块RECEIVE-DATA-RXD.VHD 和SEND-DATA-RXD.VHD

这两个模块都有两个输入端口:时钟CLK和复位RESET,分别通过信号RXD和TXD实现与上位机之间的RS232通讯,波特率为9600bps,数据传送格式为11位,依此排序为:起始位(0),数据位(D0、D1、D2、D3、D4、D5、D6、D7),奇偶校验位,停止位(1)。同时与数据处理模块之间分别通过信号允许接收、接收结束、接收错误、接收寄存器 和允许发送、发送结束、发送寄存器联系。当发送结束为0时,发送寄存器送数,允许发送也置为1。

[p] (3) 触发模块TRIGALERT.VHD

这个模块输入端口设置为:复位RESET,触发TRIG(周期为2s,脉宽为10us),时钟(0.1us), 4MS(4ms)。在触发允许的情况下,输出信号为1,开始计数,如果没有触发就一直延续至1.8S,有触发就调用计数器10US,脉宽延续为10us,等1.8S结束后输出信号变为0,结束了一次触发过程。

(4) 脉冲模块WAVEGEN .VHD

本模块主要产生充电和放电脉冲。放电脉冲波形近似正弦波,振荡频率约454HZ(2.2ms); 充电脉冲与放电脉冲之间间隔延时4 ms。遥控状态下可调参数为正峰、负峰幅度,触发延时Td及间隔时间Tb,触发模式设置序列(即正峰、负峰的序列),一个周期内的波形个数最多为12个。Tb的调节范围为200ms-400ms,Td的调节范围为0-20ms,步长为0.1us 。该模块根据上位机送的模式序列及相关约定计算出各波形触发时间间隔即负峰到正峰T12、正峰到负峰T23、负峰到负峰T34等,在触发允许时,即送出相应的波形。

(5) 数据处理模块DATA-DISPOSAL.VHD

这个模块是系统的核心模块,主要承担处理数据的任务,其它模块都与此相互通讯。

4 系统功能实现

通过XILINX 的EDA工具软件FOUDATION的VHDL设计及仿真实现,这套系统能够满足设计要求,可以实现多种脉冲工作模式,并且系统运行稳定可靠。

参 考 文 献

[1] 徐志军等. CPLD/FPGA的开发与应用. 北京:电子工业出版社,2002.1.

[2] 侯泊亨等. VHDL硬件描述语言及数字逻辑电路设计. 西安:西安电子科技大学出版社,1999

[3] XILINX Foundation Series 2.1i 设计指南. 北京:清华大学电子工程系Xilinx培训中心,1999.9 .

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:2kW高频高压电源

下一篇:一种数字式温度控制系统的设计

射频和天线工程师培训课程详情>>