- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

CypressCY8CPLC20动力线通信(PLC)解决方案

录入:edatop.com 点击:

动力线通信(PLC)芯片.M8处理器的速度达24MHz,有两个8x8乘法器和32位累加器,支持双向半双工通信,可配置的波特率高达2400bps,I2C频率50,100和400kHz,参考设计用于110 V/240 V AC以及110 V/240 V AC/DC动;力线,并和CENELEC EN 50065-1:2001 以及FCC Part 15兼容.本文介绍了CY8CPLC20主要特性,方框图以及CY3274 HV开发套件主要特性,电路图和材料清单.

The CY8CPLC20 is an integrated powerline communication (PLC) chip with the powerline modem PHY and network protocol stack running on the same device. Apart from the PLC core, the CY8CPLC20 also offers Cypress’s revolutionary PSoC technology that enables system designers to integrate multiple functions on the same chip.

Powerlines are available everywhere in the world and are a widely available communication medium for PLC technology.

The pervasiveness of powerlines also makes it difficult to predict the characteristics and operation of PLC products. Because of the variable quality of powerlines around the world, implementing robust communication has been an engineering challenge for years. The Cypress PLC solution enables secure and reliable communications. Cypress PLC features that enable robust communication over powerlines include:

■ Integrated Powerline PHY modem with optimized filters and amplifiers to work with lossy high voltage and low voltage powerlines.

■ Powerline optimized network protocol that supports bidirectional communication with acknowledgement-based signaling.

In case of data packet loss due to bursty noise on the powerline, the transmitter has the capability to retransmit data.

■ The powerline network protocol also supports an 8-bit CRC for error detection and data packet retransmission.

■ A Carrier sense multiple access (CSMA) scheme is built into the network protocol that minimizes collisions between packet transmissions on the powerline and supports multiple masters and reliable communication on a bigger network.

CY8CPLC20主要特性:

■ Powerline communication solution

Integrated powerline modem PHY

Frequency shift keying modulation

Configurable baud rates up to 2400 bps

Powerline optimized network protocol

Integrates data link, transport, and network layers

Supports bidirectional half duplex communication

8-bit CRC error detection to minimize data loss

I2C enabled powerline application layer

Supports I2C frequencies of 50, 100, and 400 kHz

Reference designs for 110 V/240 V AC and 12 V/24 V AC/DC Powerlines

Reference designs comply with CENELEC EN 50065-1:2001 and FCC Part 15

■ Powerful Harvard-architecture Processor

M8C processor speeds to 24 MHz

Two 8x8 multiply, 32-bit accumulate

■ Programmable system resources (PSoC Blocks)

12 Rail-to-Rail Analog PSoC Blocks provide:

Up to 14-bit ADCs

Up to 9-bit DACs

Programmable gain amplifiers

Programmable filters and comparators

16 Digital PSoC Blocks provide:

8 to 32-bit Timers, Counters, and PWMs

CRC and PRS Modules

Up to four full duplex UARTs

Multiple SPI masters or slaves

Connectable to all GPIO Pins

Complex peripherals by combining blocks

■ Flexible on-chip memory

32 KB flash program storage 50,000 erase or write cycles

2 KB SRAM data storage

EEPROM emulation in flash

■ Programmable pin configurations

25 mA sink, 10 mA source on all GPIOs

Pull-up, Pull-down, high Z, strong, or open drain drive

Modes on all GPIO

Up to 12 analog inputs on all GPIOs

Configurable interrupt on all GPIOs

■ Additional system resources

I2C slave, master, and multi-master to 400 kHz

Watchdog and sleep timers

User-configurable low-voltage detection

Integrated supervisory circuit

On-chip precision voltage reference

■ Complete development tools

Free development software (PSoC Designer )

Full-featured in-circuit emulator (ICE) and programmer

Full-speed emulation

Complex breakpoint structure

128 KB trace memory

Complex events

C Compilers, assembler, and linker

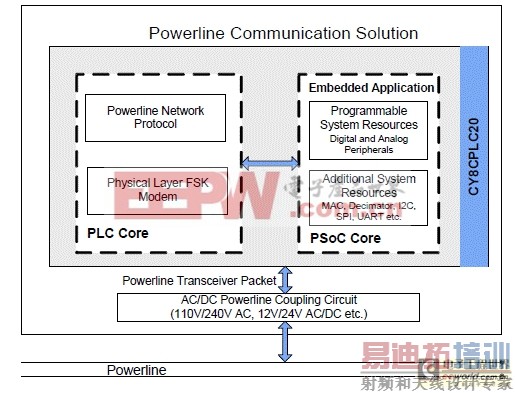

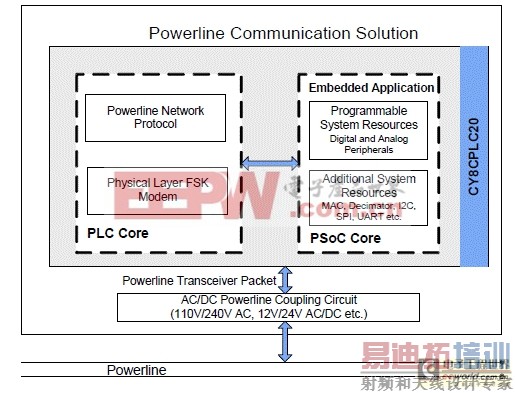

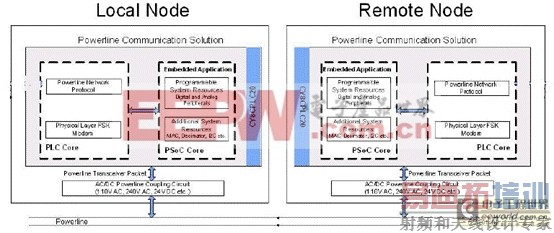

图1.CY8CPLC20方框图

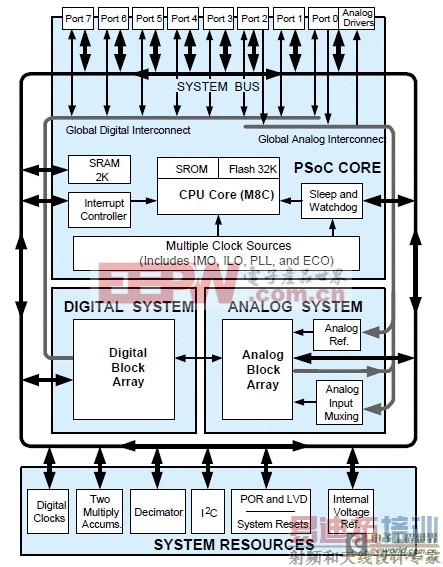

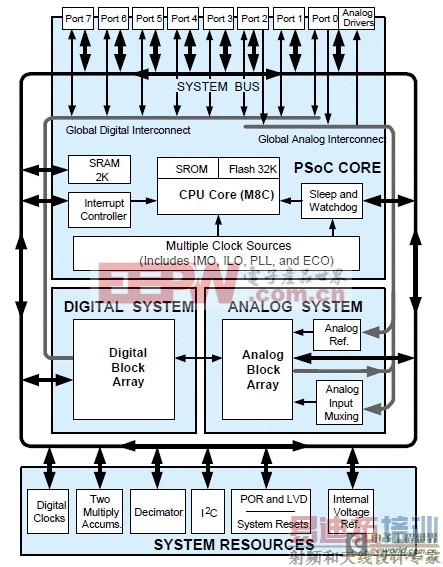

图2.CY8CPLC20 PSoC核框图

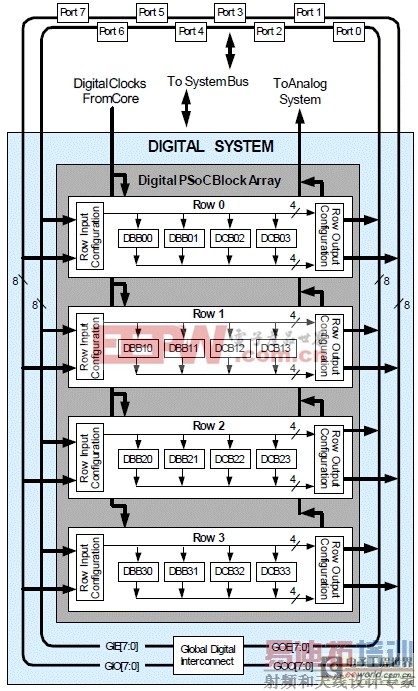

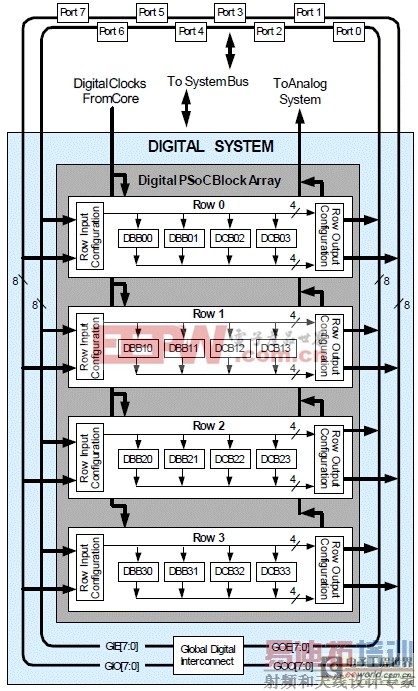

图3.CY8CPLC20数字系统框图

图4.CY8CPLC20模拟系统框图

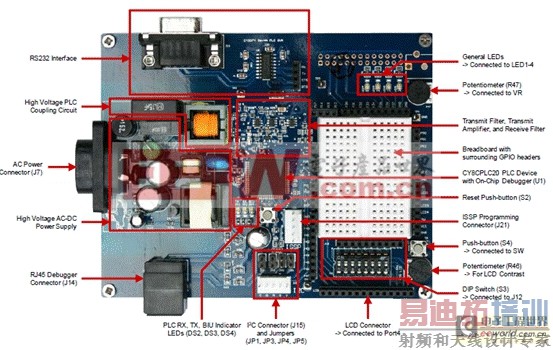

CY3274 HV开发套件

The CY3274 is for prototyping and development on the CY8CPLC20 with PSoC Designer. This kit supports in-circuit emulation. The software interface enables users to run, halt, and single-step the processor and view the content of specific memory locations. PSoC Designer also supports the advanced emulation features. The hardware comprises of the high voltage coupling circuit for 110VAC-240VAC powerline, which is compliant with the CENELEC/FCC standards. This board also has an onboard switch mode power supply.

CY3274 HV开发套件包括:

■ One High Voltage (110-230VAC) PLC Board. Cypress recommends that a user purchases two CY3274 kits to setup a two-node PLC subsystem for evaluation and development.

■ CY8CPLC20-OCD (100 TQFP)

■ Software CD

■ Supporting Literature

■ MiniProg1

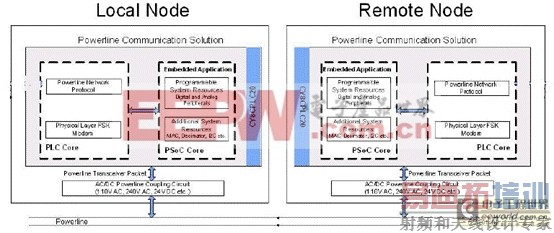

图5.PLC系统级方框图–两节点

The key features of the CY3274 development board are:

■ User friendly PLC Control Panel application available on kit CD

■ CY8CPLC20-OCD – 100-pin TQFP on-chip debug (OCD) device that allows quick design and debug of a PLC application.

The CY8CPLC20 100-pin TQFP is available for debug purpose only. For production quantities, CY8CPLC20 is available in 28-pin SSOP and 48-pin QFN packages.

■ Chip power supply derived from 110 V to 240 V AC

■ User configurable general purpose LEDs

■ General purpose 8-position DIP switch

■ On board surge protection and isolation circuit

■ RJ45 connector to use ICE debugger

■ RS232 COM port for communication

■ Header to attach the LCD card

■ I2C header for communicating to external device

■ ISSP header for programming the CY8CPLC20

图6.可编程PLC HV开发板外形图

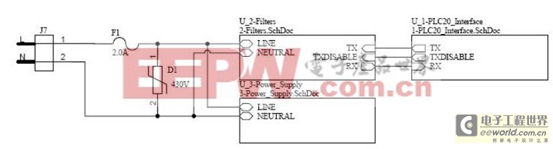

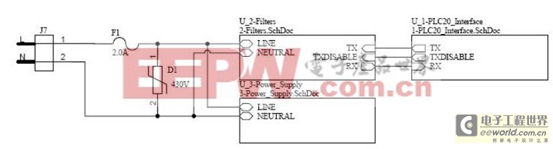

图7.开发板框图

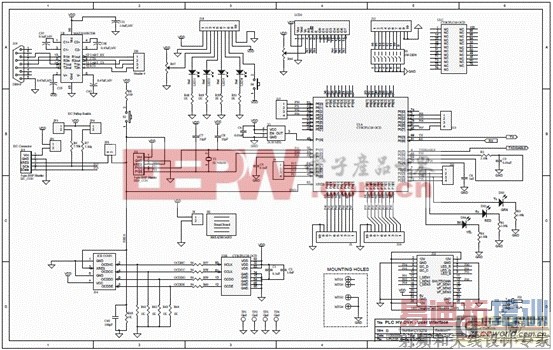

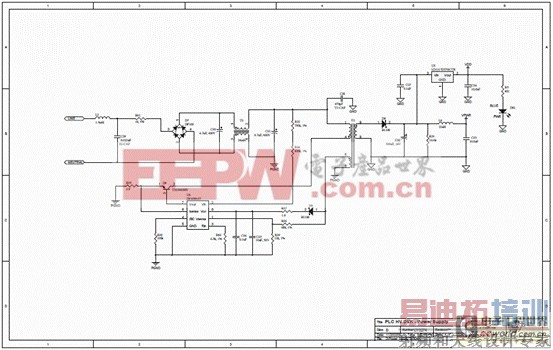

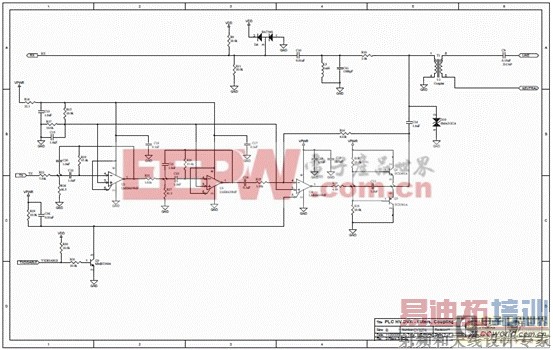

图7.可编程PLC HV开发板电路图:用户接口

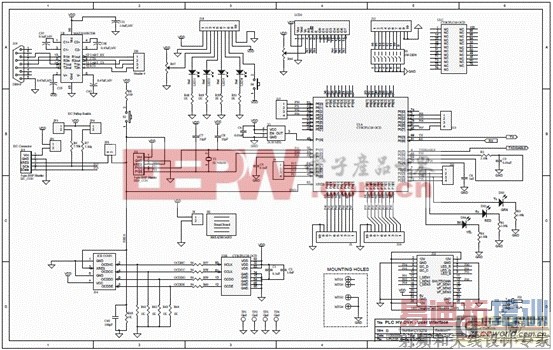

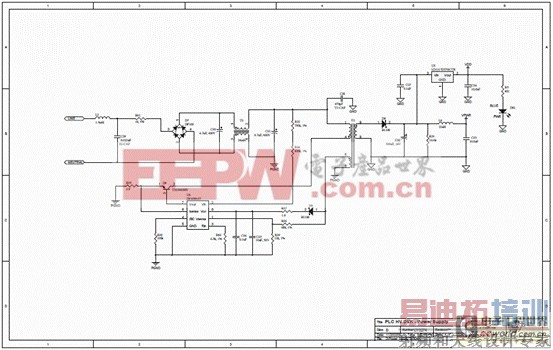

图8.可编程PLC HV开发板电路图:发送和接收滤波器与耦合

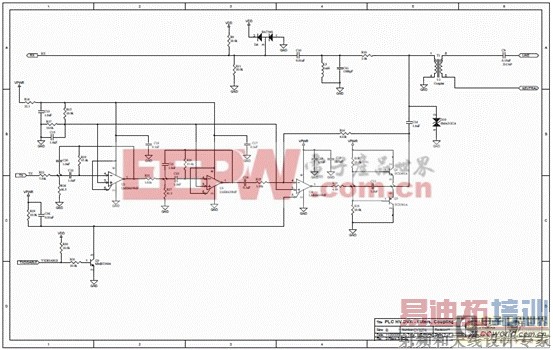

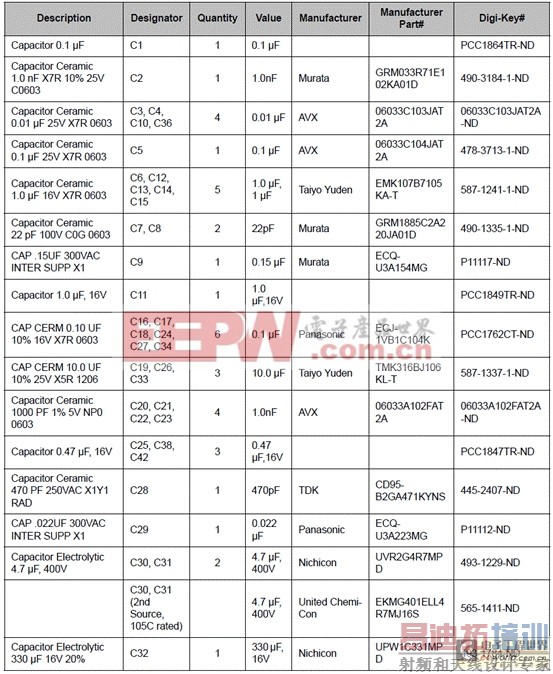

图9.可编程PLC HV开发板电路图:电源

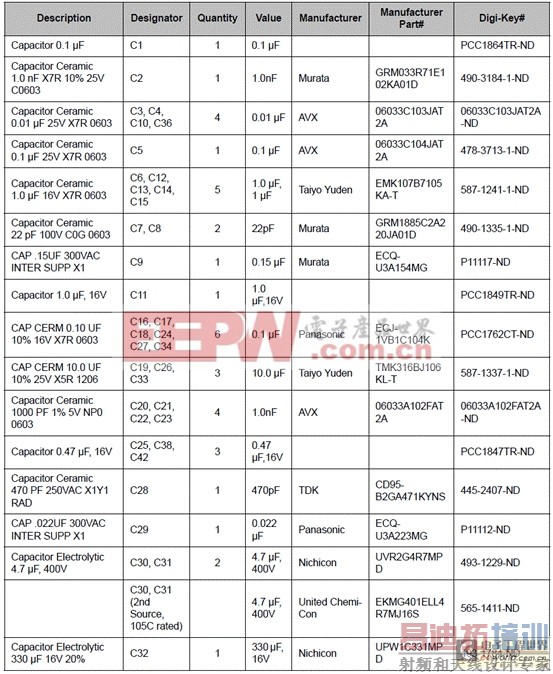

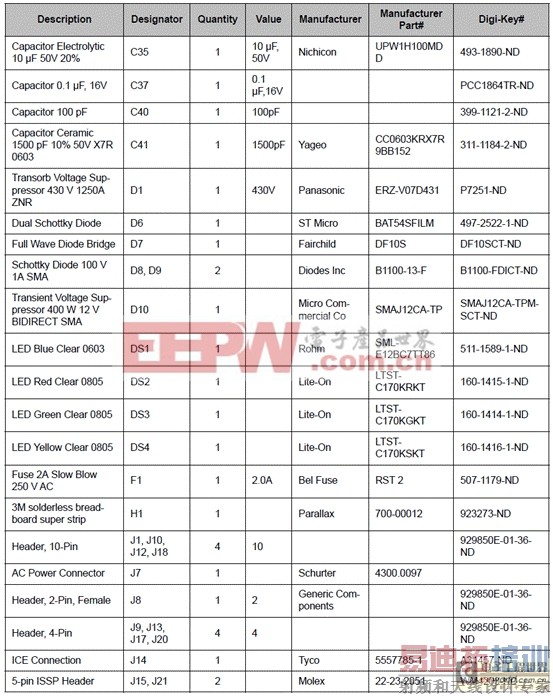

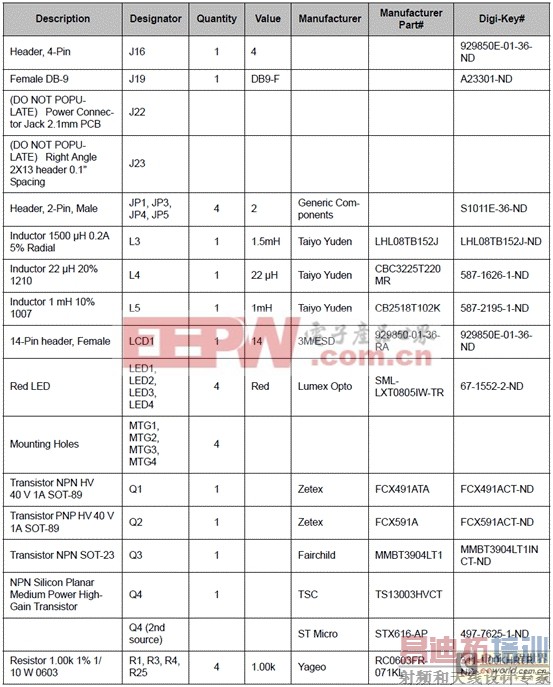

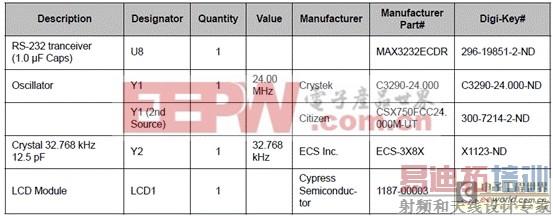

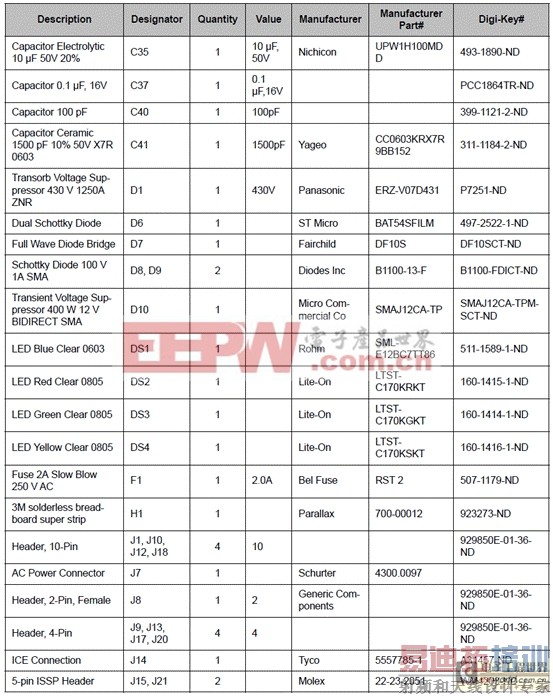

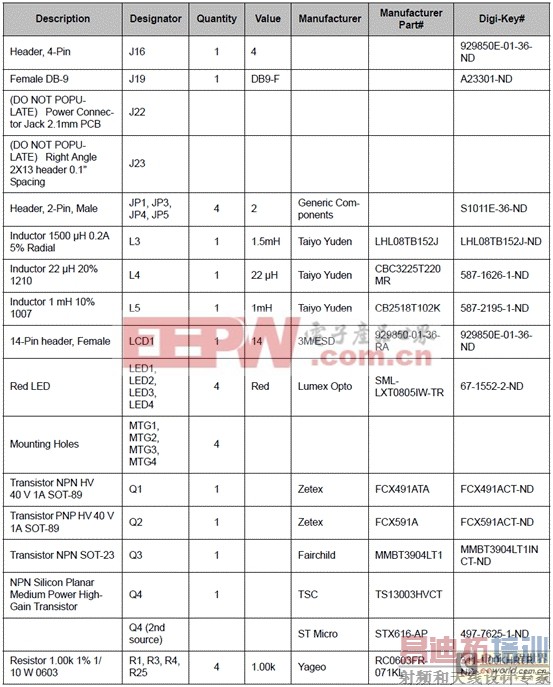

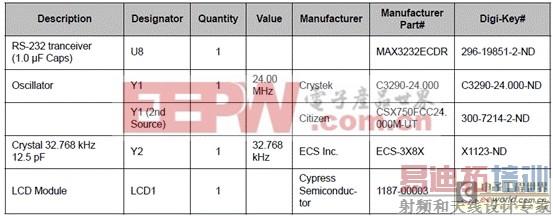

可编程PLC HV开发板材料清单:

详情请见:

http://www.cypress.com/ docID=30115

和

http://www.cypress.com/ docID=31735

The CY8CPLC20 is an integrated powerline communication (PLC) chip with the powerline modem PHY and network protocol stack running on the same device. Apart from the PLC core, the CY8CPLC20 also offers Cypress’s revolutionary PSoC technology that enables system designers to integrate multiple functions on the same chip.

Powerlines are available everywhere in the world and are a widely available communication medium for PLC technology.

The pervasiveness of powerlines also makes it difficult to predict the characteristics and operation of PLC products. Because of the variable quality of powerlines around the world, implementing robust communication has been an engineering challenge for years. The Cypress PLC solution enables secure and reliable communications. Cypress PLC features that enable robust communication over powerlines include:

■ Integrated Powerline PHY modem with optimized filters and amplifiers to work with lossy high voltage and low voltage powerlines.

■ Powerline optimized network protocol that supports bidirectional communication with acknowledgement-based signaling.

In case of data packet loss due to bursty noise on the powerline, the transmitter has the capability to retransmit data.

■ The powerline network protocol also supports an 8-bit CRC for error detection and data packet retransmission.

■ A Carrier sense multiple access (CSMA) scheme is built into the network protocol that minimizes collisions between packet transmissions on the powerline and supports multiple masters and reliable communication on a bigger network.

CY8CPLC20主要特性:

■ Powerline communication solution

Integrated powerline modem PHY

Frequency shift keying modulation

Configurable baud rates up to 2400 bps

Powerline optimized network protocol

Integrates data link, transport, and network layers

Supports bidirectional half duplex communication

8-bit CRC error detection to minimize data loss

I2C enabled powerline application layer

Supports I2C frequencies of 50, 100, and 400 kHz

Reference designs for 110 V/240 V AC and 12 V/24 V AC/DC Powerlines

Reference designs comply with CENELEC EN 50065-1:2001 and FCC Part 15

■ Powerful Harvard-architecture Processor

M8C processor speeds to 24 MHz

Two 8x8 multiply, 32-bit accumulate

■ Programmable system resources (PSoC Blocks)

12 Rail-to-Rail Analog PSoC Blocks provide:

Up to 14-bit ADCs

Up to 9-bit DACs

Programmable gain amplifiers

Programmable filters and comparators

16 Digital PSoC Blocks provide:

8 to 32-bit Timers, Counters, and PWMs

CRC and PRS Modules

Up to four full duplex UARTs

Multiple SPI masters or slaves

Connectable to all GPIO Pins

Complex peripherals by combining blocks

■ Flexible on-chip memory

32 KB flash program storage 50,000 erase or write cycles

2 KB SRAM data storage

EEPROM emulation in flash

■ Programmable pin configurations

25 mA sink, 10 mA source on all GPIOs

Pull-up, Pull-down, high Z, strong, or open drain drive

Modes on all GPIO

Up to 12 analog inputs on all GPIOs

Configurable interrupt on all GPIOs

■ Additional system resources

I2C slave, master, and multi-master to 400 kHz

Watchdog and sleep timers

User-configurable low-voltage detection

Integrated supervisory circuit

On-chip precision voltage reference

■ Complete development tools

Free development software (PSoC Designer )

Full-featured in-circuit emulator (ICE) and programmer

Full-speed emulation

Complex breakpoint structure

128 KB trace memory

Complex events

C Compilers, assembler, and linker

图1.CY8CPLC20方框图

图2.CY8CPLC20 PSoC核框图

图3.CY8CPLC20数字系统框图

图4.CY8CPLC20模拟系统框图

CY3274 HV开发套件

The CY3274 is for prototyping and development on the CY8CPLC20 with PSoC Designer. This kit supports in-circuit emulation. The software interface enables users to run, halt, and single-step the processor and view the content of specific memory locations. PSoC Designer also supports the advanced emulation features. The hardware comprises of the high voltage coupling circuit for 110VAC-240VAC powerline, which is compliant with the CENELEC/FCC standards. This board also has an onboard switch mode power supply.

CY3274 HV开发套件包括:

■ One High Voltage (110-230VAC) PLC Board. Cypress recommends that a user purchases two CY3274 kits to setup a two-node PLC subsystem for evaluation and development.

■ CY8CPLC20-OCD (100 TQFP)

■ Software CD

■ Supporting Literature

■ MiniProg1

图5.PLC系统级方框图–两节点

The key features of the CY3274 development board are:

■ User friendly PLC Control Panel application available on kit CD

■ CY8CPLC20-OCD – 100-pin TQFP on-chip debug (OCD) device that allows quick design and debug of a PLC application.

The CY8CPLC20 100-pin TQFP is available for debug purpose only. For production quantities, CY8CPLC20 is available in 28-pin SSOP and 48-pin QFN packages.

■ Chip power supply derived from 110 V to 240 V AC

■ User configurable general purpose LEDs

■ General purpose 8-position DIP switch

■ On board surge protection and isolation circuit

■ RJ45 connector to use ICE debugger

■ RS232 COM port for communication

■ Header to attach the LCD card

■ I2C header for communicating to external device

■ ISSP header for programming the CY8CPLC20

图6.可编程PLC HV开发板外形图

图7.开发板框图

图7.可编程PLC HV开发板电路图:用户接口

图8.可编程PLC HV开发板电路图:发送和接收滤波器与耦合

图9.可编程PLC HV开发板电路图:电源

可编程PLC HV开发板材料清单:

详情请见:

http://www.cypress.com/ docID=30115

和

http://www.cypress.com/ docID=31735

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:Microchip连接电网的太阳能微逆变器220V参考设计

下一篇:TIStellarisLM3S2000混合动力汽车电池充电器解决方案

射频和天线工程师培训课程详情>>