- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

最新全能数控电源IC-ADP1043A(六)

摘要:随着数字技术的发展和成熟,电源产品更多地向数字化方向发展。采用数字技术可减小电源高频谐波干扰和非线性失真,同时便于CPU数字化控制。文中重点介绍了ADP1043A的功能、原理及具体应用细节。ADP1043A的创新架构能支持多种拓扑结构,其图形化的操作界面、丰富的监控和管理功能,非常方便技术人员操作,也改变了以往对数字电源的认识。

关键词:ADP1043A;EEPROM;OrFET控制;同步整流(上接第9期)

5 通讯系统

5.1 I2C接口

ADP1043A的控制通过I2C接口被载出,ADP1043A接到I2C总线作为从属元件,由主控器件控制。

5.2 I2C地址

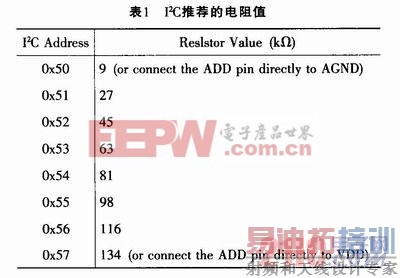

ADP1043A的I2C地址有外部从VDD端接到AGND的外部电阻来设置,表1列出了推荐的电阻值及相应的地址,8个不同的地址可用。

如果一个不正确的电阻值被用上,结果I2C地址会紧靠两地之间的临界处,一个标志就被设置出来。

在表1中推荐的值可以变化±2kΩ,ADP1043A扔回相同的地址。因此,推荐选择1%精度的电阻用于ADD端。

I2C地址0*58是广播地址,它允许多个部分同时写入,用广播地址提到表1中的I2C专用地址,所有ADP1043A器件的I2C总线都会写入,广播地址仅能用于写命令。

5.3 通用I2C时段

ADP1043A有一时段送出特色,以保护SDA线上的对应的故障条件,I2C接口监视SDA线。如果它停在低电平时间为0.65mst_low1.3ms,则I2C接口即复位,等待另一次起始条件。

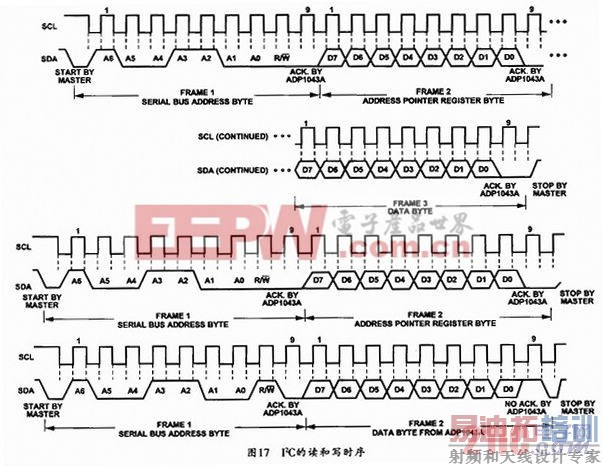

I2C规范定义出专门的条件,给不同类型的读和写的操作,一般I2C的读和写的操作展示在时序图中,如图17所示,并在此部分描述。

(1)主控初始数据传输用建立一个其实条件,定义了高电平到低电平传输为串联数据链SDA,此时串联时钟链SCL仍旧为高电平。这只是数据流在流动,所有从属外部连接到串联总线。响应启动条件并植入下面8位。由一个7位从属地址组成,加上一个![]() 位,它决定出书记传输的方向,即什么数据从从属器件中写入或读出。

位,它决定出书记传输的方向,即什么数据从从属器件中写入或读出。

(2)其并行的地址相应传输地址由加入数据键来响应,在低周期第九个时钟脉冲以前作为已知位,并保持其在时钟脉冲高周期为低,所有其他总线上的期间仍旧是空闲的。此时选择器件要等到数据从写到读出。如果![]() 位是0,则主控写到从属器件中。如果位

位是0,则主控写到从属器件中。如果位![]() 是1,则主控从从属器件中读出。

是1,则主控从从属器件中读出。

(3)数据传送整个串联总线为9个时钟脉冲的顺序,数据的八位跟随由从从属期间定下的位。数据链的传输在时钟信号低周期时必须出现。再高的周期仍旧稳定,因为低到高传输是在时钟为高并可以以停止此信号来解释。

(4)如果操作时写入,则在从属地址之后第一个数据位睡觉哦一个命令位,它告诉从属器件什么是期待的下一个,它可能是一个结构,诸如作为告知从属器件所期待的时钟写入,或它可以是一个寄存器地址,它告诉从属器件随后的数据写入在哪里。

(5)因为数据仅能一个方向流动,作为由![]() 位定义的在读出期间它不可能发送一个命令到从属器件。在读出期间以前,它必须首先执行一个写的操作,告知从属器件,读得时间多从短暂。从数据写入到起到与/或地址。

位定义的在读出期间它不可能发送一个命令到从属器件。在读出期间以前,它必须首先执行一个写的操作,告知从属器件,读得时间多从短暂。从数据写入到起到与/或地址。

(6)当所有数据为已经读出或写入时,停止条件建立起来,在写入模式主控器件将数据链。在第10个时钟脉冲到维持停止条件期间拉高。在读出模式,第九个时钟脉冲之前主控器件释放SDA线。但从属器件没有拉低,这是作为没有未承认位已知的。主控器件将数据链拉低,在第十个时钟脉冲前的低电平周期期间,将数据链拉低。然后在第十个时钟脉冲到维护停止条件期间在拉高。

如果几个读或写的操作必须逐渐地执行,则主控器件可以送出一个重新开始的条件,以代替停止条件,去开始新的操作。[p]

5.4 EEPROM

EEPROM分割成两个主方框:工厂方框和主方框.工厂方框包括128个8位字节,主方框包括8K个8位字节。

①从属方框

从属方框是一个128个字节,它用于存储原始的模拟器件公司工厂中校准和寄存器设置的,用户不能改变这些设置,工厂方框的目录可以在任何时候下载到寄存器中,它用写入0*01到寄存器0*7B中的方法完成。

②主方框

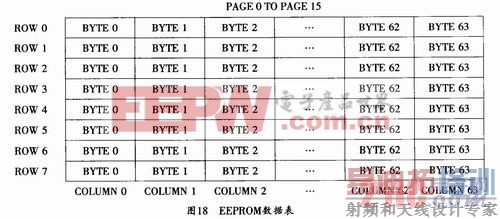

主方框可以存储数据,它可分为16页,每页包含了512字节,每页中的数据存入字节以便组成从8行和64列,如图18所示。

主框0页(用户设置)

ADP1043A用户寄存器设置是存在主框的0页中。VDD加到ADP1043A的每个时段。寄存器设置并自动下载从EEPROM的0页到寄存器。ADP1043A有唯一的命令去写入新的值到0页,它由写入寄存器O*00到0*7B。清理上部数据EEPROM到下面(在AD公司软件GUI中)执行此任务。

主方框:1页一15页

主方框的1页到15页可用于科技并储存其他数据寄存器0*7C和寄存器0*7D用于点入此页,字节的行和列即可存取了。

写入实例:

写数据0*AA到ADP1043A的12页3行30列,在I2C地址0*57处。

读出实例

从ADP1043A的10页7行62列,读出数据,在I2C地址0*50处。

③EEPROM通行令锁定

EEPROM通行令提供EEPROM由不希望的原因造成了偶然改变,还是故意改变通行令确保临界规范,如OVP和OCP不会改变。

EEPROM总是锁住的。当EEPROM下载它的内容到寄存器时,通行令也下载,如果用户写入相同的通行令到寄存器0*5E两次,则EEPROM就不含锁定并且可以适时修正。

当EEPROM没锁住时,它是可能由写入新的值到寄存器0*5E改变通行令的。EEPROM在此值修正后,包含了新的通行令,工厂方框不履行通行令为0*00。

修正EEPROM的通行令,用户必须写入寄存器0*7B,写0*00到此寄存器修正EEPROM,用户必须在写入命令后适应与ADP1043A通讯之前等待至少50ms。

注意:EEPROM将在VDD加上以后500ms中不再写入。

④EEPROMdffe通行令改变

为了改变EEPROM的通行令,要做下面这些步骤:

*写旧的通行令给寄存器0*5E

*写新的通行令给寄存器0*5E

*在第二时段再次写新的通行令给寄存器0*5E

*在第三时段再次写入的通行令给寄存器0*5E

*写0*00到寄存器0*7B

*等待50ms

*为锁住EEPROM,写任何一个不同于通行令的值给寄存器0*5E

⑤周期重复检测

ADP1043A执行一次检测,以确保EEPROM命令能在启动时正确下载到寄存器。它比较整个下载数和第一次下载写入EEPROM的数据。如果这里有不相符的,则CRC故障标志。在寄存器0*03中设置,这个标志用于确保从EEPROM下载正确的数据到起初时的寄存器。

5.5 软件GUI

自由软件GUI对编程和决定ADP1043A电路结构,GUI是设计直接用于电源设计及理想的减少电源设计的麻烦和开发时间,软件包括滤波器设计,电源PWM拓扑省口。GUI还是一个信息中心,显示所有读出监视的状态及ADP1043A的标志。

6 寄存器的细节描述

寄存器0*04到0*07是锁定故障的寄存器,再次寄存器中标志在故障移去后设有复位,标志也由寄存器来清理,注意,锁存位中是时钟低到高电平的传输,还要注意这些寄存器位在读时可以清除,除非,故障仍旧存在,推荐锁住故障寄存器,在故障去除后,在确保寄存器复位。

其它寄存器还有:数值寄存器、电流检测和电流限制寄存器、电压检测寄存器、ID寄存器、PWM和同步整流时序寄存器、数字滤波由调节寄存器、自适应死区时间寄存器。

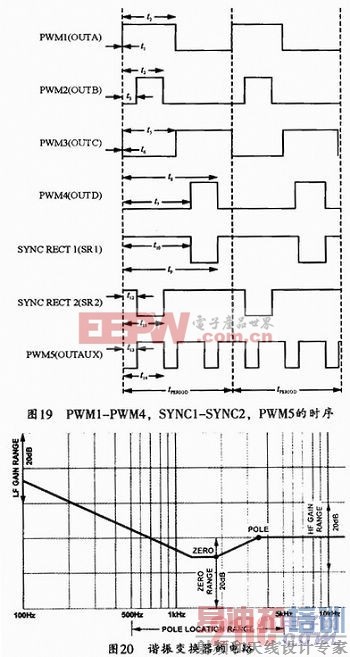

图19是PWM1—PWM4, SYNC1—SYNC2,PWM5的时序。

7 谐振模式的工作

ADP1043A支持谐振变换器的工作,谐振变换器是对应传统的固定频率变换器而言的,他们提供高的开关频率,小的几何尺寸,高的转换效率,用图20是一个用途广泛的谐振变换器的电路。[p]

7.1 谐振工作模式的使能

令ADP1043A进入谐振模式工作的开关变换器,寄存器0*40必须设置成D*3F值,在谐振模式下,PWM输出有固定的占空比,采用变频式工作。

7.2 谐振模式下的同步整流模式

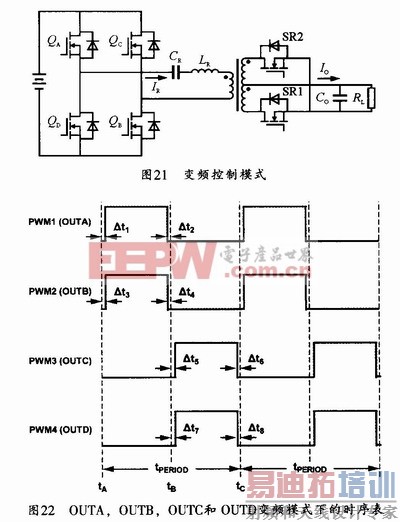

在变频控制模式下,OUTA和OUTB仅在第一个开关周期的前半时段为高电平(tA-tB),反之OUTC和OUTD仅在第一个开关周期的后半时为高电平,如图21所示。

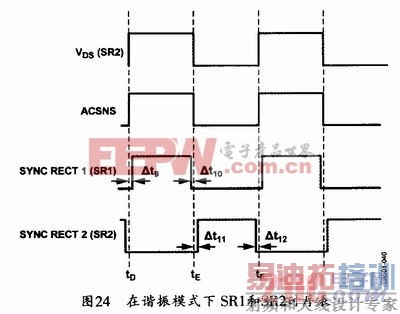

同步整流的控制在谐振模式下复杂化了,ADP1043A的ACSNS比较器用于控制SR信号,在谐振模式下工作时,SR1输出驱动也由ACSNS比较器的上升沿进行,而SR2输出驱动由此比较器的下降沿驱动,见图22。

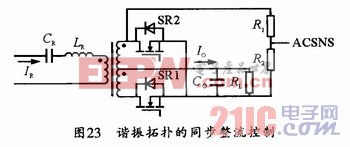

下面是ADP1043A怎样用于串联谐振拓扑中实现同步整流控制的实例,SR2的VDS电压可以用于控制SR的信号,ACSNS端接到SR2VDS电压的分压器,它提供一个时间信息给两个同步整流器驱动,如图23所示。

在获得时序信息之后SR1由ACSNS比较器的上升沿驱动,SR2由ACSNS比较器的下降沿驱动,如图24所示,用此方法,就可以实现同步整流,对SR1和SR2信号独立地调节其开启及关断的延迟。

这个例子不是唯一控制SR信号的方法,如果用户有其他方法控制SR信号,它可以代替用链接ACSNS输入的方法。

7.3 调节PWM输出的时段

为了精确调节PWM输出时段,下列寄存器可用于设置死区时间和PWM输出的岩石,寄存器0*41-0*49寄存器0*4B-4F,寄存器0*51-57。调节的死区时间为5ns,参看谐振模式寄存器的描述,润、案件GUI也可以用于频率改制的设置。

7.4 频率限制的设置

最小频率设置由寄存器0*42和0*44的前四位。

7.5 谐振工作模式下的反馈控制

与传统的固定频率PWM变换器不同,谐振变换器使用改变频率的方法调节的,当ADP1043A工作在谐振模式下,检测电压低于基准电压时,开关频率降低,这令ADP1043A能以零电压开关模式去控制谐振变换器。

虽然开关频率是变化的吗反馈电压取样频率固定在400KHz,反馈滤波的参数系基于该频率,计算滤波器参数的方法与固定的PWM模式是相同的。

7.6 在谐振模式下的软启动

在软启动中,ADP1043A的基准向上斜,由反馈系统闭环,开关频率减小,从最高限制到稳压值,软启动时间设置及滤波器设置是固定频率的PWM模式是相同的。

7.7 轻载下的工作

为了控制变换器在非常轻载的工作,ADP1043A可以工作在跳跃模式下,用寄存器0*4A使能和禁止,当开关频率高于跳跃式阈值时,即进入跳跃式模式工作,此阈值由进入值加上0*10决定。

7.8 OUTAUX在谐振模式下的工作

在谐振模式下,他不能用作控制信号,当然,OUTAUX可用于其他作为固定频率的PWM信号,其有固定的占空比。

7.9 谐振模式下的保护

所有标志及保护功能在谐振模式下都能正常工作,与固定频率时相同。

7.10 谐振模式下寄存器的描述

◇PWM的开关频率设置表。

◇OUTA上升沿死区时间。

◇最低开关频率的限制设置。

◇OUTA下降沿死区时间。

◇最低开关频率的限制设置。

◇OUTB上升沿死区时间。

◇最高开关频率的限制设置。

◇OUTB下降沿死区时间。

◇最高开关频率的限制设置。

◇OUTC上升沿死区时间。

◇谐振模式下的猝发模式工作。

◇OUTC下降沿死区时间。

◇OUTD上升沿死区时间。

◇OUTD下降沿死区时间。

◇SR1上升沿死区时间。

◇SR1下降沿死区时间。

◇SR2上升沿死区时间。

◇SR2下降沿死区时间。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:UPS供电系统与发电机组的匹配兼容性

下一篇:电磁干扰及常用的抑制技术