- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高压大功率PS ZVS PWM DC/DC FB变换器数字式移相脉冲发生器

录入:edatop.com 点击:

1 引言

由于需要设计的电源输出电压变化范围大(0~5KV),而且输出电流保持在3~6A之间可调;较为困难的在于PS ZVS PWM DC/DC FB变换器移相脉冲的产生,目前市场上有UC3875、UC3879等芯片用于实现移相PWM控制方式;但是,这类芯片多用于输出固定电压的变换器,并且变换器的输出电压较低,其控制方式为将输出电压反馈给芯片,芯片根据输出电压调节移相脉冲的移相角。如果使用这类芯片产生移相脉冲(例如UC3879),那么可能的方式是通过控制其反馈电压输入端的电压来控制移相脉冲的移相角;不过这类芯片的缺陷在于其移相角度难于精确控制;而在保证输出电流恒定的情况下,需要精确控制移相角,故本文设计了全数字式移相脉冲产生电路。

2 超前桥臂移相脉冲的产生电路

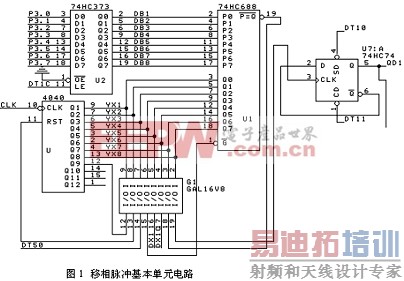

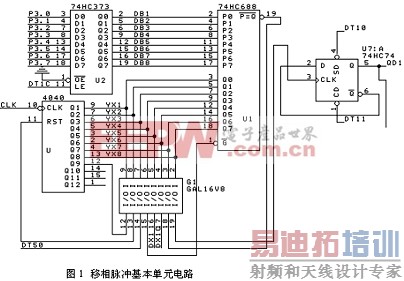

本文的移相脉冲产生电路主要由四个基本组成,每个基本单元负责产生一路触发信号。基本单元电路见图1。基本单元由数字比较器(74HC688)、锁存器(74HC373)、计数器(4040)、GAL(GAL16V8)、D触发器(74HC74)组成。计数器(4040)和GAL16V8组成计数溢出值为400的计数器,其输入时钟频率为8MHz;之所以使用GAL16V8是为了调试时可灵活设定计数溢出值、逻辑关系可调。计数器的计数值与锁存器(74HC373)的输出值(该值由80C196KC通过总线提供)作为数字比较器(74HC688)的输入,当二者相等输出低电平信号,触发D触发器(74HC74)输出翻转。CPU通过DT50可控制计数器工作与否,通过DT10、DT11可对D触发器置初值。图1中GAL16V8的逻辑关系为:管脚2、5、12相与在和管脚14进行或运算,通过管脚13输出;即计数器计数满400时复位或CPU进行强制复位。管脚12、2、5进行与非运算通过管脚15输出;即计数器计数满400时,禁止比较器工作,使其输出1。管脚2、5、12进行与非运算在和管脚18进行与运算,通过管脚19输出(GAL实现此关系为: );即比较器输出为0或计数器溢出,均产生由1到0的跳变,以使D触发器翻转。管脚17为管脚16的非,用于CPU置比较器动作的值。图中QD1为IGBT的驱动信号。

);即比较器输出为0或计数器溢出,均产生由1到0的跳变,以使D触发器翻转。管脚17为管脚16的非,用于CPU置比较器动作的值。图中QD1为IGBT的驱动信号。

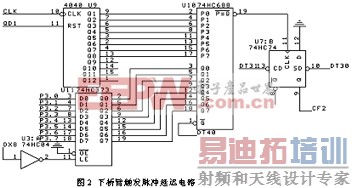

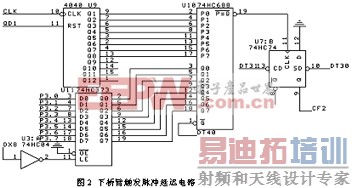

实际上图1为超前桥臂的上臂触发脉冲产生电路,其下臂的触发电路与其基本相同;只不过其不使用锁存器(74HC373),而是与上臂的触发电路共用DB1~DB8信号,即它们脉宽相等;为了实现上、下臂的交替导通以及防止直通所需的延迟,当上臂触发脉冲发生由1向0的跳变,下臂触发脉冲产生电路要有一定的延迟,图2的电路实现这种功能。其基本原理为CPU通过总线给U11(74HC373)置数(即延迟时间),当该值当该值与4040的计数值相等,比较器74HC688输出0,

U7:B(D触发器)输出0,即CF2输出0,CF2连接下臂触发脉冲产生基本单元GAL16V8的14脚(图3.1中DT50对应的位置),以允许下臂触发脉冲产生电路开始工作。图中QD1信号为上臂的触发信

号,当其为0时,计数器(4040)开始工作以确定延迟时间。CPU通过DT31、DT30可给U7:B(D触发器)预置初值,另外可通过DT40控制比较器(74HC688)工作与否。实际应用中U7:B(D触发器)预置1,其被触发后一直输出0,除非重新置数。

3 滞后桥臂移相脉冲的产生电路

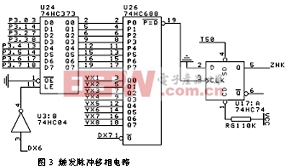

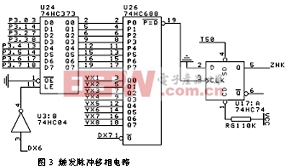

滞后桥臂的触发脉冲产生电路基本结构与超前桥臂的触发脉冲产生电路相同,可参见图1和图2。但是,为了实现滞后桥臂相对于超前桥臂的脉冲移相功能需要有延迟电路,图3的电路完成此功能。CPU通过总线给U24(74HC373)置数以确定移相角的大小,比较器U26(74HC688)的信号YX1~YX8取自超前桥臂上臂触发脉冲产生电路的计数器(图1中4040的Q1~Q8),当计数器(U26)的输入相等即到达移相角输出0,D触发器U17:A翻转输出0,即ZHK为0,ZHK用于触发滞后桥臂的触发脉冲产生电路开始工作(ZHK的连接位置相当于图1的DT50)。由于U17:A的D端接地,一旦ZHK输出0,除非通过T50强制置1,否则一直输出为0。另外可通过DX7控制比较器的工作与否。

4 结语

以上给出了一种PS ZVS PWM DC/DC FB变换器移相脉冲的产生电路,该电路通过CPU对其控制可以灵活调节移相角度,改变触发脉冲宽度等优点,可以依照此电路的设计思想,用CPLD等复杂可编程逻辑器件来实现。

参考文献:

【1】阮新波,严仰光;直流开关电源的软开关技术;科学出版社;2000年。

【2】王聪;软开关功率变换器及其应用;科学出版社;2000年。

【3】钟利平,刘成芳;新型相移PWM控制器UC3879及其在零电压全桥变换器中的应用;国外电子器件;1996年8月。

由于需要设计的电源输出电压变化范围大(0~5KV),而且输出电流保持在3~6A之间可调;较为困难的在于PS ZVS PWM DC/DC FB变换器移相脉冲的产生,目前市场上有UC3875、UC3879等芯片用于实现移相PWM控制方式;但是,这类芯片多用于输出固定电压的变换器,并且变换器的输出电压较低,其控制方式为将输出电压反馈给芯片,芯片根据输出电压调节移相脉冲的移相角。如果使用这类芯片产生移相脉冲(例如UC3879),那么可能的方式是通过控制其反馈电压输入端的电压来控制移相脉冲的移相角;不过这类芯片的缺陷在于其移相角度难于精确控制;而在保证输出电流恒定的情况下,需要精确控制移相角,故本文设计了全数字式移相脉冲产生电路。

2 超前桥臂移相脉冲的产生电路

本文的移相脉冲产生电路主要由四个基本组成,每个基本单元负责产生一路触发信号。基本单元电路见图1。基本单元由数字比较器(74HC688)、锁存器(74HC373)、计数器(4040)、GAL(GAL16V8)、D触发器(74HC74)组成。计数器(4040)和GAL16V8组成计数溢出值为400的计数器,其输入时钟频率为8MHz;之所以使用GAL16V8是为了调试时可灵活设定计数溢出值、逻辑关系可调。计数器的计数值与锁存器(74HC373)的输出值(该值由80C196KC通过总线提供)作为数字比较器(74HC688)的输入,当二者相等输出低电平信号,触发D触发器(74HC74)输出翻转。CPU通过DT50可控制计数器工作与否,通过DT10、DT11可对D触发器置初值。图1中GAL16V8的逻辑关系为:管脚2、5、12相与在和管脚14进行或运算,通过管脚13输出;即计数器计数满400时复位或CPU进行强制复位。管脚12、2、5进行与非运算通过管脚15输出;即计数器计数满400时,禁止比较器工作,使其输出1。管脚2、5、12进行与非运算在和管脚18进行与运算,通过管脚19输出(GAL实现此关系为:

实际上图1为超前桥臂的上臂触发脉冲产生电路,其下臂的触发电路与其基本相同;只不过其不使用锁存器(74HC373),而是与上臂的触发电路共用DB1~DB8信号,即它们脉宽相等;为了实现上、下臂的交替导通以及防止直通所需的延迟,当上臂触发脉冲发生由1向0的跳变,下臂触发脉冲产生电路要有一定的延迟,图2的电路实现这种功能。其基本原理为CPU通过总线给U11(74HC373)置数(即延迟时间),当该值当该值与4040的计数值相等,比较器74HC688输出0,

U7:B(D触发器)输出0,即CF2输出0,CF2连接下臂触发脉冲产生基本单元GAL16V8的14脚(图3.1中DT50对应的位置),以允许下臂触发脉冲产生电路开始工作。图中QD1信号为上臂的触发信

号,当其为0时,计数器(4040)开始工作以确定延迟时间。CPU通过DT31、DT30可给U7:B(D触发器)预置初值,另外可通过DT40控制比较器(74HC688)工作与否。实际应用中U7:B(D触发器)预置1,其被触发后一直输出0,除非重新置数。

3 滞后桥臂移相脉冲的产生电路

滞后桥臂的触发脉冲产生电路基本结构与超前桥臂的触发脉冲产生电路相同,可参见图1和图2。但是,为了实现滞后桥臂相对于超前桥臂的脉冲移相功能需要有延迟电路,图3的电路完成此功能。CPU通过总线给U24(74HC373)置数以确定移相角的大小,比较器U26(74HC688)的信号YX1~YX8取自超前桥臂上臂触发脉冲产生电路的计数器(图1中4040的Q1~Q8),当计数器(U26)的输入相等即到达移相角输出0,D触发器U17:A翻转输出0,即ZHK为0,ZHK用于触发滞后桥臂的触发脉冲产生电路开始工作(ZHK的连接位置相当于图1的DT50)。由于U17:A的D端接地,一旦ZHK输出0,除非通过T50强制置1,否则一直输出为0。另外可通过DX7控制比较器的工作与否。

4 结语

以上给出了一种PS ZVS PWM DC/DC FB变换器移相脉冲的产生电路,该电路通过CPU对其控制可以灵活调节移相角度,改变触发脉冲宽度等优点,可以依照此电路的设计思想,用CPLD等复杂可编程逻辑器件来实现。

参考文献:

【1】阮新波,严仰光;直流开关电源的软开关技术;科学出版社;2000年。

【2】王聪;软开关功率变换器及其应用;科学出版社;2000年。

【3】钟利平,刘成芳;新型相移PWM控制器UC3879及其在零电压全桥变换器中的应用;国外电子器件;1996年8月。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

射频和天线工程师培训课程详情>>