- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

数字系统的电源去耦设计

工程师们在设计PCB电源分配系统的时候,首先把整个设计分成四个部分:电源(电池、转换器或者整流器)、PCB、电路板去耦电容和芯片去耦电容。本文将主要关注PCB和芯片去耦电容。电路板去耦电容通常很大,大约是10mF或者更大,而且主要用于特定场合中。

设计一个去耦电容包括两步。首先,整流器根据电气计算电容值,然后将电容放置在PCB上。确切地讲,电容放在离数字芯片多远的地方合适?但人们常常忽略了PCB本身就是去耦设计的一部分。本文将讨论在哪里电路板适合去耦设计。

去耦需求

基本上,电源通过一根导线向数字芯片提供能量。这个电源有可能离芯片比较“远”。电源线为5 英寸长的16 AWG的电线和4英寸长的20mil的走线并不少见。这些导线具有电阻、电容和感应,这些都影响能量的传送。电感和导线的长度成正比,是产生大多数质量问题的原因。

走线需要着重考虑,因为它决定了总的电感和电流流动的环路环路。这个环路环路能够而且很可能会辐射电磁干扰(EMI)。

在芯片的旁边放置一个小电源(比如电容),能让电容到芯片Vcc管脚之间的走线长度最小,从而减少环路面积。这能尽量减少由导线电感引起的电压降问题。由于回路环路减小了,所以EMI也减小了。

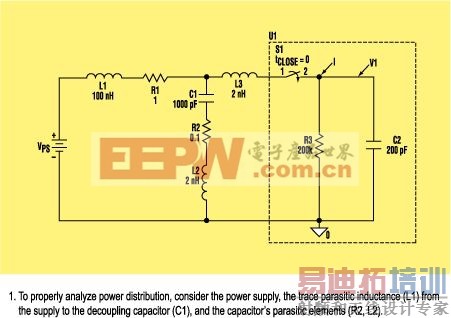

直接把数字芯片U1连接到电源上意味着可能需要几英寸的走线。可以将具有寄生电感L2和R2的电容C1插入到电路中离芯片比较近的地方,距离小于1英寸(图1)。L3是C1 和 U1之间的导线电感。L1 和 R1是从电源到电容之间导线的寄生参数。

这样,可将走线长度减小到mil量级,将导线阻抗减小到可以应用的程度。C2在这里非常重要,它决定电源必须供给多少电流。C2代表了U1的内部负载和U1必须驱动的外部负载。当S1关闭时,这些负载连接到电源,并马上需要电流。

电感是电源和开关之间阻抗的主要来源。例如,对于10mil宽度的走线,电阻、电容和电感分别大约是0.02Ω/in,2 pF/in和20nH/in。这些是用于PCB板的走线(微带线和带状线)和导线的典型数据。当频率大约高于100 kHz时,感抗jΩl是主要阻抗。

因此,增加C1具有两个作用。一是它将减少开关期间,电源和芯片之间的导向电感。这将保护V1(也就是到U1上的Vcc) 不会减小到低于进行正确电路操作的所需电压值。另外,它可减小高频电流流动的环路面积以及相应的EMI。

因此,电容将V1保持住,但需要将V1保持多高呢?这个问题主要集中在器件的噪声裕量,例如最小的电压噪声裕量VNmmin,这个噪声裕量可以存在,并仍允许正确的电路运行。(这有点难以计算,因为实际值依赖于半导体的噪声裕量,近似和电源电压成正比。)根据图1,正确的工作运行意味需要满足下面条件:

VNmmin ≥ VPS D VZmax (1)

在该图中,VZmax完全落在L3上。

电流I也需要考虑。简单讲,这是数字输入所需要的电流,设计工程师必须确保它的供应。因为它是所需的最大电流,Imax,因此电源和开关之间的最大阻抗Zmax不会大于:[p]

|Zmax|≥(VZmax/Imax) (2)

从电源到芯片的线路是5英寸长的16-AWG导线和4 英寸长、20mil宽的走线,它将提供100nH的电感。在某些频率f上,感抗将大于所能容忍的Zmax。这个频率将通过变换电感的阻抗方程得到:

fmax = |Zmax|/2πL (3)

在这个频率之上,C1不能提供足够的电压来满足器件所需的噪声裕量,信息也无法成功地传输。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:高压晶闸管触发器

下一篇:通信电源集中监控技术在通信电源中的应用