- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

降低视频密集型便携式产品的能耗

随着 3G无线网的发展,加上集成电路(IC)技术的不断进步,便携式消费电子设备拥有了令人目眩的播放各种视频内容的能力。不断增加的移动产品让用户进入了多彩的视觉体验之中,如实时视频、交互式游戏、交互式地图、网页浏览还有高分辨率照片。并且,不论是基本的手机,还是全功能的PDA,这些功能都在产品的吸引力方面起着至关重要的作用,从而对其市场成功也影响巨大。

但是,实现这此功能的图像处理器能耗都很大,因而给便携系统设计师提出了挑战。图像处理总是需要密集的计算,同时所需时间周期也会延长。举例来说,能处理视频的移动设备必须能够对输入的每一帧进行解压、解码、调整尺寸并对之施加图形过滤器。然后它还要按每秒 30次的频率重复这些计算,才能保证输出到移动设备显示屏的视频流。这是实实在在的工作负载,对电能的胃口也非常大。

消费者对富视频产品的渴求看上去无穷无尽,而尽量降低能耗、延长电池使用时间对便携式移动产品来说将一直是个稳定的需求。解决这种互相冲突的目标需要一个全面综合的方法来节省电能。便携产品设计师备必须在整个设计流程上部署节能技术,以便在待机能耗和运行能耗两方面都达到要求。

耗电的器件

要想对移动设备的能耗进行优化,首先必须理解静态和动态耗能器件。静态能耗是待机能耗的主要组成部分,主要来自于晶体管的泄露电流。缩小器件尺寸的一个副产品就是增加了晶体管的泄露电流。

对设计师来说有一点是幸运的,即泄露可以在综合阶段使用多电压临限单元进行自动的标定。在综合过程中,可以根据电能和性能的折衷选择单元。高临限电压的单元可以减少泄露电流,但相对于低临限电压的单元,它的开关要慢许多。在时序要求不严格、开关可以慢一点的电路中,可以使用高临限电压单元来降低静态能耗。技术的进步带来了一系列不同临限电压的单元,静态能耗也就通过低能耗的实现工具得到了自动的优化,因此大体上这个问题对设计者来说已经是透明的了。

活动能耗,也就是动态能耗,是器件运行的结果,通过消除不必要的开关活动就能降低一些。寄存器传输级( RTL)时钟门控是降低动态能耗最常用的技术。时钟门控通过有选择地关闭时钟来消除不必要的开关活动,从而极大地降低计算密集型应用如图像处理中的动态能耗。

时钟门控技术

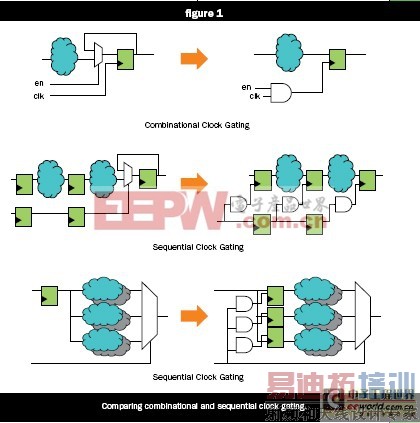

现在有两种类型的时钟门控技术,分别是合并型( Combinational)和顺序型(Sequential)(见图1)。合并型时钟门控是直接在RTL代码中取代条件声明,把时钟门控单元插入到寄存器的时钟通路中。低能耗的RTL综合工具会在模式匹配的基础上自动识别并插入合并型的时钟门控。至于低能耗综合工具在多大程度上可以使用时钟门控这个问题,它要受到RTL如何编码的制约。低能耗的综合工具是通过在RTL代码中,通过在定义声明之前找到明显的“如果(IF)”条件来找到可以插入时钟门控的机会的。但是,这些工具并不能分析并决定何时在何处给RTL代码插入这种“如果(IF)条件”以便降低能耗。还是要依赖RTL设计者在代码中明显地写上这种“如果(IF)条件”,低能耗综合工具才能把它们翻译成节能的时钟门控。

顺序型时钟门控是一种更强大的优化技术,它在计算密集型应用中降低能耗的能力已经得到验证。与合并型时钟门控不同,顺序型时钟门控并不是简单的翻译。它包含了对设计行为的序列分析。序列分析会对整个电路功能进行设计状态和周期的巡视,识别出不必要的开关动作,诸如并发中无用的数据计算等。之后它能找出相关的逻辑条件来消除这种开关动作。

举例来说,当一个寄存器的输出被留在当前电路周期中的时候,序列分析就能用逻辑条件来关闭合并逻辑中和在前一个周期中生成这个数据的寄存器中的开关。这种序列关系可能向前或向后在多个周期中传播。 RTL设计总是包含有多重序列关系,它可以用来减少开关动作,并且因此可以优化寄存器、内存、时钟以及合并逻辑的电能消耗。

序列时钟门控能带来的节能效果是非常显著的,特别是在诸如视频处理这类应用中,这种应用一般都会支持多种视频格式和依赖于数据的算法。根据输入视频流的不同,通常只需要对其中的一部分进行解码计算和过滤器操作。因此,如果设计师能充分理解设计中的序列关系,就会发现这里有许多可以使用时钟门控的机会。

部署时钟门控

在实现时钟门控方法学时有三个关键因素:完全地识别出所有可用的时钟门控机会;精确地生成可以利用这些机会的 RTL代码;有效地对这些加入了时钟门控的RTL代码进行验证以确保它仍然保留着原有功能。

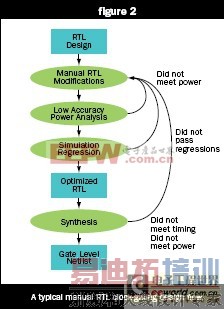

只到最近,加入时钟门控的一般方法还是要设计者自己去查看代码,寻找时钟门控的机会并手工在 RTL代码中加入所需的IF条件。典型的时钟门控设计工作流包括手工加入时钟门控优化代码,使用RTL能耗估计方法来评测这些优化方法的效果,最后运行模拟回归来验证所需要的功能都还在。最后是对RTL代码进行综合,同时可以对门级的电能消耗进行估算以便决定是否还需要更多的时钟门控(见图2)。

在这个方法中还有许多低效率的地方。由于电路中时钟门控的机会点非常多,而且使用条件又非常复杂,设计师总会在审查并修改 RTL代码方面花费大量的时间。同时,由于并非所有的时钟门控优化方法都能带来节电效果,其中甚至有一些会对时序和面积有不良影响,所以还需要用试算的方法来得到最低能耗的设计。这种手工工作是劳动密集型的,它会延长开发周期并给RTL模拟带来额外的要求。又因为时钟门控优化方法不能用传统的合并等效检测工具进行验证,所以还必须开发新的模拟测试基准和评测工具,来验证新的时钟门控方法没有影响原有的功能。解决这一困境的自然方案就是设计自动化。

在 RTL设计流中增加能耗优化工具

在采用新的能耗优化工具时,设计团队要随时记着几个关键考虑。第一,新工具带来的电能节省可以补充并累积到现有能耗优化工具上,这一点非常重要。第二,为了避免学习曲线过长并增加脚本开发工作,新工具应该能使用标准的文件格式,并且能够加入现有的设计流程之中。第三,非常重要的一点是新工具应该提供一个全面的解决方案,不能在设计流中的其他地方带来新问题。比如,自动识别时钟门控机会是很有用的,但如果这个工具不能生成优化过的 RTL代码、并全面验证所有原有功能都没有失效,那它就会对生产率带来负面冲击。

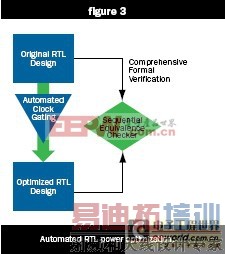

最近,可以自动进行识别、在 RTL设计中插入并验证序列时钟门控的商业解决方案已经上市了(图3)。使用这种自动序列时钟门控和验证工具为视频密集型便携式应用带来了巨大的节能效果。

这些功能包含在 Calypto系统公司的PowerPro CG(时钟门控)及SLEC CG中。PowerPro CG是一款自动化的RTL电能优化解决方案,经验证它可以带来最高达60%的电能节省,同时对面积和性能影响很小甚至没有影响。SLEC CG是一个序列等效检测工具,它可以验证序列时钟门控的优化。这些工具补充了现有的低能耗设计工具流,它们可以分析RTL设计中的序列行为,识别出时钟门控机会,比已有的工具更强大。它们可以读取标准的、可综合的Verilog及VHDL RTL代码,从而可以嵌入到现有的设计流中去。

另外,生成的能耗优化的 RTL代码同原来的带有额外时钟门控逻辑的RTL设计是一样的。能耗优化的RTL代码还要使用序列逻辑等效检测工具进行全面的验证,以确保没有带来功能上的改变。能耗优化的RTL设计可以直接进入低能耗综合,以便拥有下游电能优化能力的更多优势。通过把设计师从繁杂的设计分析、手工修改RTL代码以及费时的模拟工作中解放出来,生产效率和节能 [p] 效果都得到了提升。

结论

在计算密集、低能耗并加入能耗优化技术,诸如在现有设计流中加入序列时钟门控的设计过程中,电能优化是一个关键需求,设计师因而可以在处理视频的同时极大地消减电能消耗。依靠当前的自动化序列时钟门控解决方案,设计师可以节省更多电能,同时提高现有的手工时钟门控方法的设计效率。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:单相变压器城市照明节电新系统

下一篇:高压晶闸管串联阀触发电路的设计