- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

关于封装、出gerber以及clearance设置的一些总结&问题,请帮忙

该工具栏对应的功能,其中标记的图标对应的功能为 Add New Label

Terminal /2D line /Text /Copper/Copper Cut Out/Keepout/From Library/Wizard/Add New Label

做封装时,Terminal /2D line /Text /Copper工具分别对应Design items中的pads /lines /text /Copper,Keepout工具对应Outlines中的Keepout。做好封装在Layout中调用该封装时,Design items、Keepout是不能单独被选中、操作的,而必须作为一个component来进行操作。要修改的话也只能进入Edit Decal才能修改的。而在出gerber时,Terminal对应的是pads;2D line画的图形以及Text均对应为Outlines(坛子里有大虾说过在Layout中line画的图形对应为outlines,个人没有试验出来,因为filter中没有选项来让选中outlines);Keepout在Layout中对应的是什么我也还不确定,但是可以肯定的是,在出gerber时,它对应的是Keepout。

这里有个问题,就是在做封装时,在哪些情况下是需要做keepout的?画keepout时其准则是什么?

至于Copper Cut Out,在Layout中还能看到,但是在出gerber时,不管选中什么都不能导出该内容。

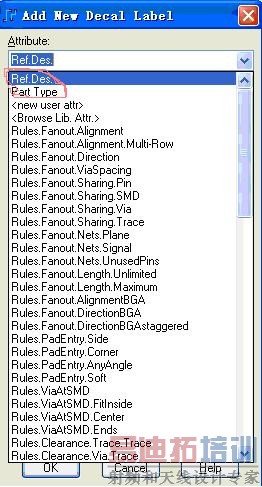

Add New Label工具可以添加一些Label,诸如Res.Des.,Part Type等Label,这些在Layout中是可以单独选中并操作的,在出gerber时也是有相应对应的。常用的Label主要是Res.Des.和Part Type。其他的Label没有使用过,所以不是很清楚,所以就不做说明了。

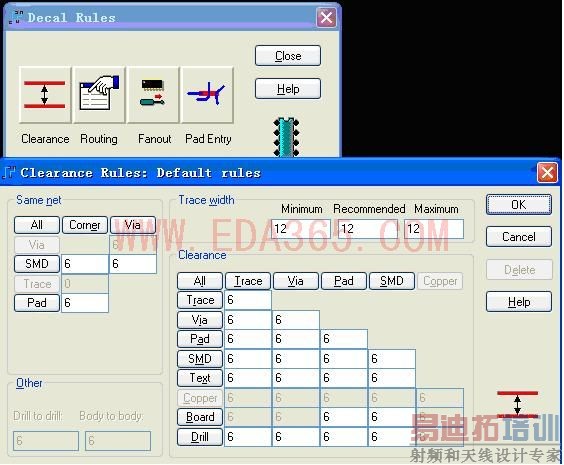

在封装设计时,还有Decal Rules,这个有什么好处呢?有在做封装时设置这个的么?如果设置的话,大致都是怎样设置的呢?

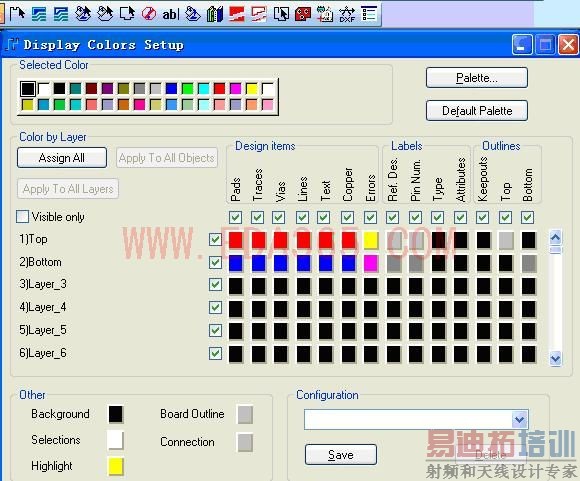

Layout中相关的items:

他们在出gerber时的所对应的很明了,所以就不说了。

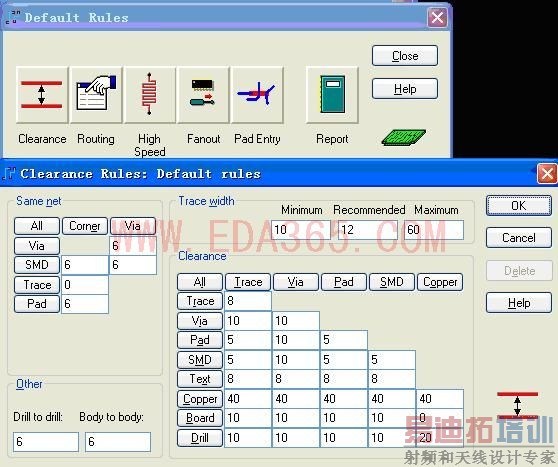

2.Layout中Design Rules中clearence设置相关

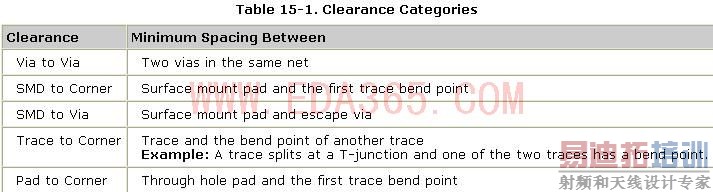

Same net部分在手册中已经有了说明,如下图所示:

Clearance部分就要说明一下了。

首先得了解trace、via、pad、smd、text、copper、board、drill在Layout中指的是哪些对象,只有明白了这个,才能设置好想要的clearance。

Trace、via都很明了,而pad指的是插件的焊盘(through hole pad),smd指的是贴片的焊盘(surface mount pad),text、copper、board也很明了。最后那个drill我还没有明白它指的是什么。

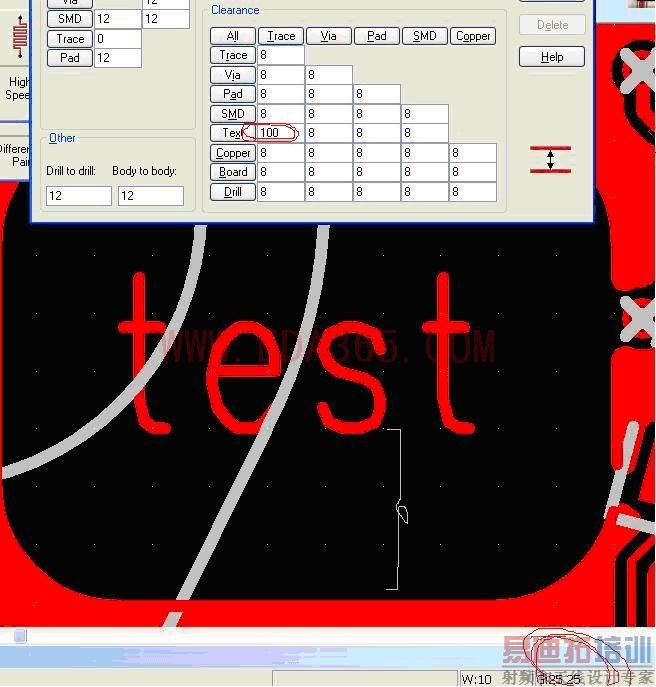

表格中已经包含了大部分的对象之间的间距规则设置。除了lines没有做出说明外,其他的都已经做了说明。但是要注意的是,text与copper之间的间距是遵照text与trace之间的规则。如下图所示。

最后那个drill to drill有什么用处呢?

body to body指的又是什么呢?本以为指的是元件跟元件之间的最小距离,但现在发现好像不是那样的

突然想起在verify design 时,设置的clearance值对在封装中添加的line/text/copper也是有影响的,所以一般建议把line/text画到丝印层等相关层上去

检查间距时,发现在一些元件的text处和我的布线交叉时,会报间距太小等错误!而当我打开该pcb元件封装时,发现这些text是在top的位置;而我把这些text改到顶层丝印层时,就没有错误了(在封装中添加的text也是如此,而且这种text在layout是outline类型的,要想在丝印层显示出来,必须设置好丝印层outline的显示颜色)

我发现每次更改过tool-verify design-clearance-setup中的一些check后,检查,再改回原来的设置,居然报的错误数目相差很多,有时候No Error,有时3个,有时15个,有时60多个。错误基本都处在元件外框的text标识和走线的重叠处。

报错误如下:

(xxx,yyyL1)distance between tracks too small: COMPONENTS FREE TEXT, TRACE (aaa, bbb) distance is less than 0.1524

(xxx,yyyL1)distance between tracks too small: COMPONENTS FREE TEXT, TRACE (aaa, bbb)overlapping

自己顶起

帮你顶起

LZ的说的问题,我也遇到过,呵呵,帮你顶下

body to body 不是 器件与器件的距离吗?

帮忙顶下,总结的很细。

mark,学习之!

总结的好,以前很多自己还没有认识到

是的 只是默认设置是不检查该项的 而我不知道 所以就困惑了

我个人觉得,每次在完成布局之后还是要去检查一下body to body的间距问题,因为会出现,两个元件重叠而被忽视的问题,到时候等到出图了还是没有发现,后果就严重了。body to body指的是原件边框和元件边框的间距(注意:特指边框在和pad是同一层的,也就是,如果边框不画在元件层,是drc检查不出来的,所以要求做库的规范化)。

好东西!

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:关于S3C2440 的布线

下一篇:板框的的坐标