- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

一种改进的基于扫描的电路设计

引言

近年来,随着科学技术的不断发展。单一芯片中所含的晶体管数目越来越多,其电路也越来越复杂。

为了确保芯片在制作完成后的正确性,有关电路测试的这个问题越来越受重视。而且其测试的难度及成本也越来越高,于是如何有效地检验电路的正确性,并大幅度地降低测试成本,成为我们现在研究的热点。通常我们在设计芯片的同时,可以根据芯片本身的特征,额外地把可测性电路设计(Design For TESTability)在芯片里。谈到可测性的电路设计,内建自测试(BIST)和基于扫描Scan—Based)的电路设计是常被提及的。

基于扫描的电路设计是可测性设计中最常用的一种方法。它是属于TEST—Per—Scan测试方法的电路。

目前的测试方法有两种,一种是TEST—Per—Scan,另一种是TEST—Per—Clock,这两种测试方法各有各的优缺点。所谓TEST—Per—Scan的运作方式,就是我们将一个电路里的全部或部分寄存器串联起来,形成一条扫描链,然后将测试序列在每个周期移入一个值,直到测试向量填满整个扫描路径为止,再经过一个周期后,我们将待测电路的测试结果传到扫描链里。最后移出做压缩分析。这种方法的优点是很容易运用在任何商业性的设计流程中,而且其硬件架构对系统功能的影响较小,控制硬件设计也较为简单:缺点是要*较多的时间来产生测试向量,测试速度慢。所谓TEST—Per一Clock,就是当我们在测试电路的时候,每一个周期都送进一个新的测试向量进入电路,同时在电路的输出得到测试的结果,所以这种方式的电路测试时间较短,速度较快。

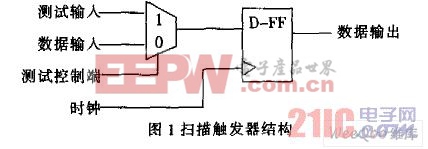

基于扫描的电路设计,主要是将待测电路内的寄存器,全部或部分用扫描寄存器来代替,让我们在对电路进行测试的时候可以轻易地控制其输入及输出,扫描寄存器最常用的结构是多路扫描寄存器,它是在普通寄存器的输入端口加上一个多路器, 如图1所示。测试控制端即多路器的选择端,数据输入端为正常的功能输入端。此外还有测试输入端、时钟输入端和数据输出端。当测试输入端为“0”时,寄存器为正常的功能输入,电路处于正常模式;当测试输入端为“1”时,寄存器为扫描输入。电路就转换成扫描模式。很明显。基于扫描的电路设计可以增加待测电路的可控制性和可观察性。这种设计方式。优点是需要额外的硬件空间较少,而且测试的效果较好,缺点是测试时间太长。造成测试时间长的原因有多个方面,我们可以通过分析基于扫描的电路设计来得到。这个缺点,正是我们想要改进的部分。

2 基于扫描的电路的基本单元

2.1 线性反馈移位寄存器(LFSR)

最简单的测试向量产生器就是由线性反馈移位寄存器(Linear Feedback Shift Registers,LFSR)来组成的。因为当时钟信号改变时,线性反馈移位寄存器内D触发器的值就会改变,此时我们就可以将这些会一直改变的值当成测试向量,送给电路做测试。

一般的线性反馈移位寄存器可以分为两类,分别是Extemal XOR线性反馈移位寄存器和Internal XOR线性反馈移位寄存器,如图2所示。这两种线性反馈移位寄存器的主要差别在于External XOR线性反馈移位寄存器的modulo一2加法器是放在电路的反馈路径上。而Internal XOR的线性反馈移位寄存器的加法器则是放在两个寄存器之问。这两种不同结构的线性反馈移位寄存器所产生出的测试向量也不一样,ExternalXOR线性反馈移位寄存器所产生的测试向量有下列特性:每个向量与下个向量之问的关系,是向量中的位分别往右移了一位。而Internal XOR的线性反馈移位寄存器由于modulo一2加法器是在寄存器之问,所以产生的测试向量看起来比External XOR线性反馈移位寄存器有更随机的特性,所以我们必须选择InternalXOR LFSR作为测试向量产生器。

[p]

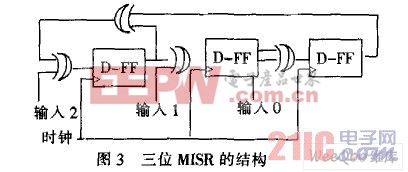

2.2 多输入特征寄存器(MISR)

多输入特征寄存器(Multiple Input Signature Reg—ister,MISR)是线性反馈移位寄存器的一种。如图3所示,将待测电路的输出部分加入线性反馈移位寄存器里,就成为一个多输入特征寄存器。

多输入特征寄存器最主要的特性是它的状态。即其寄存器的值,不仅与现在的状态有关,还与当时的输入值有关,可以表示为:Next state=MISR(Cur—renLstate,Input),而其中MISR(……)可以代表特征式不同的多输入特征寄存器。

3 基于扫描的测试架构的改进

为了减少基于扫描的电路设计的测试时间,就必须深入了解它的电路设计,了解为何其会消耗那么多的测试时间,然后来改进测试架构。

3.1 用向量压缩来减少测试时间

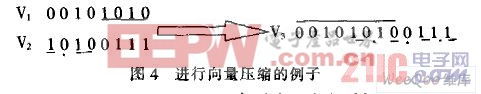

在测试过程中,我们有时可以发现,我们将要传入扫描链的测试向量,已经部分地包含在已经传入的测试向量序列中了,如图4所示。V1向量的后半部分刚好等于V2向量的前半部分“1010”,如果在传输向量的时候,先传输V1再传输V2,那么我们就只需要将V2的后半段向量信息传入扫描链就可以让V2原本的信息在扫描链中完整地呈现,如图中V3所示。很明显,我们原来要输入的测试向量的长度为16位,压缩后只有12位,节省了V2的前半部分传入扫描链的时间,从而减少了测试的时间,而且测试信息也没有减少,不会影响故障覆盖率。

3.2 用TEST—Per-Clock来缩短测试时间

我们对造成测试时间不够理想的原因进行分析:

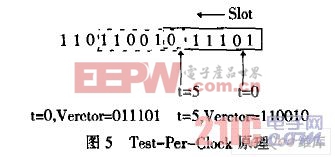

传统的基于扫描的测试电路是采取TEST—Per—Scan的方式来进行测试的,也就是说要先将测试向量扫描到电路内的由扫描寄存器所组成的扫描链内。然后才可以完成一次测试;将测试向量扫描到待测电路这个步骤是一位一位地进行的,所以如果一个电路需要长度较大的测试的向量时,那么在这整个测试过程里。将会花很多的时间在将测试向量输入到扫描链的这个步骤上,从而增加了测试时间。这个结构的测试向量的产生是利用LFSR产生出的伪随机向量,并将其送入电路做测试。用LFSR产生测试向量会产生出许多没有作用的测试向量,而这些没有作用的测试向量又会产生大量多余的时间将其送入扫描链中,造成测试时间更严重的浪费。如果采用TEST—Per—Clock的方式做测试,在扫描链里原本的测试向量,在用一个时钟的时间移进来一位之后,扫描链所含的值即是测试向量,对待测电路而言,其实都是一个新的测试向量,而且也具有伪随机向量的特性,如果此测试向量是有效的,我们的测试时间就只用了一个时钟的时间,而如果此测试向量无效,原本测试到没有作用的测试向量时所需的付出的时间代价,由于用了新的测试向量填满整个扫描链所需的时间,减少到只需一个时钟移进一位的时间。[p]

如图5所示,每个时钟周期。Slot会往左移动一位,即在Slot内产生一个新的测试向量,而Slot大小可以看成扫描链的大小。

不过,由于每个时钟都要作测试,所以每个时钟在测试后都会产生新的测试结果。传统的基于扫描的测试环境里,电路输出结果传送出来的同时也将新的测试传进扫描链里。

如果输出的向量只有一位就不会有这样的问题。

因为我们现在要产生一个新的测试向量所需要的时间只有一个时钟周期,所以时问刚刚好。但是一般而言,待测电路的输出向量都会超过一位。所以我们在观察电路输出结果这个步骤上就会有问题。为了解决这个问题,需要对传统的基于扫描的测试电路做些修改。在待测电路的输出部分,可以用MISR来取代原来的扫描链电路,也就是将输出送到MISR做特征分析,如图6所示。

但是由于电路越来越复杂,电路的主要输入与输出的个数就会很多,如果对这样的待测电路加测试电路,将会出现外加电路面积过大的问题。所以我们针对MISR的部分提出一个方法,使得因测试而增加得MISR可以尽量地缩小。

缩小MISR的大小最直接的想法是将主要输出经组合电路压缩变小,但是这样会使错误覆盖率降低,使测试向量变多,这些问题在文献中谈到了。造成错误覆盖率降低的原因是如果我们将有共同输入向量的两个主要输出通过组合电路合并的话。将可能会造成原本可以测试到的错误,在合并后就测试不到了,所以造成了错误覆盖率的降低。

为了避免这个情况的发生,我们在向量压缩的过程中。只有将没有共同输入向量的主要输出合并在一起,就不会有问题出现了。如图6所示,两个不同的待测电路的主要输出经过合并以后输出到MISR,这样用一个与门代替了一个寄存器以便减少面积,而错误覆盖率则因为两两合并的主要输出端都没有相同的主要输出资料,所以就没有错误覆盖率降低的问题存在,即原来可以被侦测到的错误,在经过主要输出端合并之后仍然可以被侦测到。

4 结论

经过改进后的基于扫描的测试架构,用向量压缩来减少测试时间,并且将TEST—Per-Scan的测试方式改成了TEST—Per-Clock的测试方式,加快了测试的速度。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:电器可靠性试验监控系统的研究开发

下一篇:高压断路器机械特性测试仪测试解决方案