- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

一类序列信号检测器的设计

摘要:介绍了一种二进制序列信号检测器的3种设计方法,该电路可应用于安全防盗、密码认证等加密场合,以及在海量数据中对敏感信息的自动侦听。电路采用数字系统设计方法,步骤程序化,电路可靠性高。

关键词:序列信号检测;数字电路;自动侦听

二进制序列信号检测器是一种能够检测输入的一串二进制编码,当该二进制码与事先设定的码一致时,检测电路输出高电平,否则输出低电平。该检测电路可广泛用于日常生产、生活及军事。例如,可以用在密码认证中,当输入密码与事先设定的密码一致时,认证成功。再如在军事领域,比较关心的是敌方通信中某些感兴趣的内容,而通信数据是海量且加密的,没有必要一一破译,只要破译部分关键词后,就可在侦听过程中,只检测这些关键词,一旦侦听到,立即启动记录仪,记录关键词时段的通信内容加以解密。在许多电子技术资料中也有一些序列信号检测电路的设计,但设计方法单一、扩展性不强。下面通过实例来说明电路的3种设计方法。

设计任务:设计一个二进制序列信号检测器,它有一个输入X,当接收到的序列为1001,则在上述序列输入最后一个1的同时,电路输出Z=1,否则输出为0,输入序列可以重叠。例如:当输入X的序列为0100100101001(首位在左),对应输出Z=0000100100001。

1 用分立触发器设计

触发器的种类很多,其中双端输入的JK触发器和单端输入的D触发器最具代表性。由于用D触发器设计的电路更为简单,故采用它来设计电路。

1.1 逻辑抽象

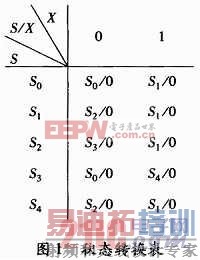

由于待检测的序列为1001,故设电路在一直输入0时的状态为S0,输入一个1以后的状态为S1,连续输入10以后的状态为S2,连续输入100后的状态为S3,连续输入1001后的状态为S4。于是得到状态转换如图1所示。

选取第1、3行解释其原理:S0表示接收到的是0,当在此基础上再接收到一个0后变为00,而需要检测的序列是1001,所以电路状态仍然停留在S0上;当电路在S0的基础上接收到1后表示接收到1001序列中的第一个1,于是电路状态转为S1。同理S2表示已经接收到10,当在此基础上接收到0后变为100,电路转到S3,但是接收到1后则变为101,于是前面接收的两位代码失去作用,只有第3位的1可作为1001的第一位,所以电路状态转回S1。[p]

通过观察状态转换表,可以发现,S1和S4在同样的输入下有同样的输出,而且状态转移后得到同样的次态。因此它们是等价的可以合并,于是,状态转换表可以化简如图2所示。

从物理概念上也不难理解这种情况。当电路连续接收到1001后,输出为1,但序列可以重叠,故最后一个1可作为下一个1001序列的第一位,所以电路在连续接收到1001后的状态S4实际上就是S1。

1.2 编码

由化简后的状态转换表2可知,电路总共有4种状态(S0~S3),而每个触发器的输出Q可以用0或1表示两种状态,于是两个触发器的输出Q1Q0的4种00、01、10、11就可以表示这4种状态S0~S3。这个过程即为编码。

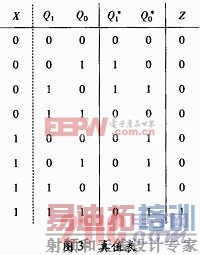

1.3 列真值表并写出状态方程

将化简后的状态转换为表中各状态,用编码表示![]() 即得到真值表,如图3所示。其中表示Q1Q0的下一状态。写出关于X,Q1,Q0的方程,即电路的状态方程,如式(1)所示。

即得到真值表,如图3所示。其中表示Q1Q0的下一状态。写出关于X,Q1,Q0的方程,即电路的状态方程,如式(1)所示。

1.4 作逻辑电路图

由于D触发器的特性方程为Q*=D,从而根据该方程就可以画出逻辑电路图,如图4所示。

[p]

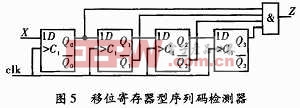

2 将触发器接成移位寄存器进行设计

以上设计方法主要依靠电路的状态转换实现序列码检测,虽然所得电路简单,但是设计过程较复杂,特别是当需要检测的序列码位数较长时,工作量较大。为此,将触发器接成移位寄存器的方式,可简化电路设计,同时也便于扩展成位数更多的序列码检测器。用4个D触发器接成的向右移位寄存器。电路如图5所示。

由图5可知,![]() 。在移位脉冲clk作用下,输入端X输入的二进制码依次向右移动,每当出现一个完整的1001序列时,输出端Z便出现高电平。这样就实现了序列码检测的功能。

。在移位脉冲clk作用下,输入端X输入的二进制码依次向右移动,每当出现一个完整的1001序列时,输出端Z便出现高电平。这样就实现了序列码检测的功能。

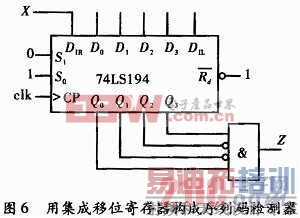

3 用中规模集成电路进行设计

既然用移位寄存器可以实现序列信号检测,那么用集成移位寄存器加少量门电路同样可以实现,而且电路可靠性更高。用4位集成移位寄存器74LS194,实现的序列1001检测器,如图6所示。

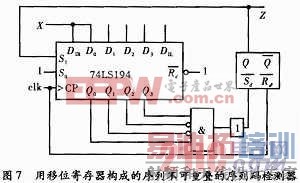

4 当序列不可重叠时的电路设计

用以上3种方法设计出的电路,都是可序列重叠的序列码检测器,若要求被检测的序列不可重叠,则在方法1中,只需要根据实际情况修改状态转换表即可.后面的设计原理及步骤不变。这种设计方法存在的问题仍然是当待检测的序列位数较长时,设计工作量大、电路可靠性降低。在采用第2、第3种方法设计时,需增加部分控制电路,为保证输入与时钟的同步性,需要使得每当检测出一个序列时,直接将序列的下一位置入寄存器最低位,同时置寄存器其余各位为序列码最后一位的反码以消除重叠代码的影响。此外再用一个锁存器使输出高电平多保持0.5个时钟周期,其优点是:可以消除移位过程中的竞争冒险,使得输出波形更稳定、电路可靠性更高,电路如图7所示。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...