- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于暂态行波法的配电网故障定位装置研究

摘要:针对我国配电网的现状,设计了一种基于暂态行波法的故障定位装置。通过FPGA进行高速数据采集,准确捕获暂态故障行波信号以保证装置的定位精度,通过MCU控制故障信息的远传, MCU+FPGA的结构解决了高速数据采集与低速任务处理之间的矛盾;GPS精确授时保证了各监测点采样的同步;采用双存储器,保证了故障数据无死区记录,提高了装置的可靠性。

关键词:行波;故障定位;高速数据采集;GPRS;GPS

引言

我国配电网由于早期投资不足,设备老化和技术性能低劣,故障频发,往往一点故障引发全线甚至大面积停电,因此必须尽快找到故障线路,排除故障。然而与输电网相比,配电网结构复杂,分支点多,特别是10kV配电网,故障排查极其困难。配电网故障的准确及时定位是电力部门急需解决的一个难题。本文采用暂态行波定位方法,介绍了一种配网故障定位装置,并给出了其软硬件设计。

行波故障定位简介

所谓行波,是指沿线路传播的电压、电流波,分为稳态行波和暂态行波。暂态行波只在故障时产生,不可重复,并且在系统达到稳态时衰减为零,具有易逝性。若线路某一点发生故障,则会在该点产生暂态行波以接近光速的速度向线路两端传播,并在波阻抗不连续的地方发生反射和折射。由于实际线路损耗的存在,行波在传输过程中会发生衰减、畸变,出现失真现象,再加上反射波、折射波的叠加,都给行波的获取带来困难,但是初始行波到达时的幅值最大,波头变化率也最大,此时最容易进行捕捉。因此,本文通过记录故障产生的初始波到达测量点的GPS 同步时钟精确时间值,由离故障点最近的两个测量点测得的GPS时间差计算故障点精确位置,可以不受故障点透射波的影响。

系统结构

整个系统由安装在测量点的若干故障定位装置、通信链路和中心端三部分构成,如图1所示。本文主要介绍故障定位装置的设计。定位装置通过感应式的电压传感器采集行波信号,监测到故障后,在移动通信网络和互联网的基础上,通过GPRS DTU将故障信息传到中心端,中心端根据至少两个测量点上传的数据和时间信息,利用小波分析理论,将故障初始行波浪涌在较低尺度(较高频带)下第1个小波模极大值点所对应的时刻作为行波波头到达时刻,即故障发生的时间,利用各测量点检测到故障的时间差计算故障点离各测量点的距离,从而确定故障点的位置,及时调度人员排除故障。

故障定位装置的硬件电路设计

故障定位装置主要由外围的电压传感器、GPS授时模块、GPRS DTU传输模块以及信号调理电路、ADC、FPGA、SRAM数据存储器和MCU构成,如图2 所示。

其中,FPGA和MCU是整个电路的核心。FPGA负责数据的高速采集,它控制ADC实时采集数据,并判断是否发生故障,若没有故障发生,将数据存入SRAM即可;否则,需锁定GPS模块的时标,及时通知MCU将记录下的故障波形和时标信息取走;MCU负责在发生故障时从FPGA获取故障相关信息,并通过GPRS DTU将数据上传到监控中心,完成数据的远程通信任务。这种MCU+FPGA的结构,充分利用了可编程逻辑器件并行、高速的特点和MCU在任务处理方面的优势,既保证了数据采样的速度,又解决了与低速任务处理之间的矛盾。下面对各部分电路以及所采用的元器件进行介绍。

电压传感器

由于10kV线路中的高压信号不能直接进入定位装置,需先进行转换,以往装置多通过电压互感器、电流互感器将信号变换成检测装置可用的低电压小电流信号,成本极高,本装置通过专利技术的感应式电压传感器获取信号,可大大降低成本。电压传感器安装于高压线路或变压器的高压绝缘瓷柱的伞形瓷盘下面,金属质地的采集端子靠紧瓷柱,与高压线之间形成一分布电容,高电压信号经这个分布电容耦合到采集端子,变为2~10V左右的电压,这几伏电压的高低,真实反映了高电压的变化。2~10V电压再经放大器进行电流放大,作为采样电压输出。

[p]信号调理电路

由于电压传感器输出的电压信号不正好在ADC的量程范围内,故需要对信号进行调理,以满足高速ADC的要求,保证ADC的正常工作,避免造成ADC的损坏。

高速数据采集及存储电路

高速数据采集及存储电路是行波法故障定位装置的核心部分,主要由FPGA、ADC模数转换器和2片SRAM构成。其中,FPGA采用Altera公司的240引脚PQFP封装的EP1C12,它具有12, 060 LEs、52个M4K RAM blocks、2个PLLs、173个用户I/O。ADC采用ADI公司的AD7822,它是一种8-bit A/D转换器,单极性输入,并行输出;内含取样保持电路,具有转换后自动Power-Down的模式,电流消耗可降低至5μA以下。转换时间最大为420ns,可满足1μs采样一次的转换要求,SNR可达48dB,INL及DNL都在±0.75 LSB以內。可应用在数据采样、DSP系统及移动通信等场合。SRAM的任务是存储高速ADC转换的数据,由于高速ADC的转换速率很高,这就要求数据存储器有较大的存储容量和较短的读/写时间,这里采用ISSI 公司的IS61LV25616。IS61LV25616是256k×16的高速异步CMOS静态RAM,读写速度可达10ns,完全可以满足要求。

具体工作过程: 线路正常运行时,没有暂态信号输入,3片AD7822在FPGA产生的高频时钟脉冲控制下并行地进行采样和数据转换,并将转换的数据循环存储在2片SRAM中的一片上,SRAM中永远保留着等于RAM容量的最新数据。当三相故障行波信号中任一相的幅值高于预设的门槛值时,表明有故障行波信号被监测到,锁存当前的时标,同时开始一个10ms的计时延时,在这段时间内继续将ADC转换的数据存储到当前的一片SRAM。当10ms延时结束时,切换地址数据总线将采集的数据存储到另一片SRAM上,同时通知MCU取走第一片SRAM中的故障行波数据和锁存的时标,并通过GPRS DTU远传给中心端服务器做进一步的处理,实现故障波形分析,进而实现故障定位。若只采用1片SRAM,在10ms延时结束后,需暂时停止数据采集,待SRAM中数据取走之后才能重新采集数据,以保证有用的故障信息不被冲掉。如果在转存暂态数据期间线路发生故障,则不能对其进行监测,造成故障数据漏记,无法定位。采用双SRAM,由于MCU转移数据和高速ADC继续采集数据可以在FPGA的协调下同时进行,从而在一定程度上解决了以往装置存在的循环存储器死区问题。

单片机外围电路

单片机(MCU)外围电路主要包括3部分:与GPRS DTU连接的数据远传电路、与GPS模块连接的时间获取电路和与FPGA之间的数据通信电路。根据单片机需完成的功能,本系统中采用Microchip高性能RISC CPU PIC18F8520,它内部有32kB的FLASH程序存储器和2kB的SRAM数据存储器、1kB的EEPROM数据存储器;运算速度可达10MIPS;可以工作在DC~40MHz的时钟频率范围之内;具有外部存储器接口,可方便地访问外部存储器中的程序或数据,便于与FPGA的数据通信;具有2个USART接口,支持RS-485和RS-232,其中一个USART接口与GPRS DTU连接,可对DTU进行配置并传输数据,另一个与GPS模块相连,用来获取精确到秒的时间信息。

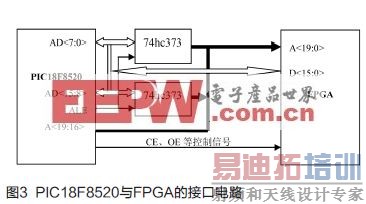

无线通讯模块采用成都众山科技ZSD2110 GPRS DTU。ZSD2110是一款使用GPRS进行无线数据传输的终端设备,支持透明数据传输和用户自由控制传输模式,本系统中采用透明数据传输模式,不用关系复杂的网络协议,通过全透明串行口,就可进行无线数据收发,可大大简化单片机软件程序的设计。GPS授时模块采用Garmin的GPS15XL,它是12通道的GPS接收机,精密授时类型精度可达±50纳秒(典型值);具有串行端口,输出为RS232,输入可为RS232或者具有RS232极性的TTL电平,波特率从300~38400可选,默认为4800。可输出NMEA0183 2.0/3.0的ASCII码语句/Garmin二进制格式信息。非常适合应用于车辆导航、海事导航、电力系统校时等。由于DTU和GPS模块都是通过串行口与单片机连接,接口比较简单,需特别说明的是单片机与FPGA之间的数据通信接口电路。单片机PIC18F8520需通过其EMI接口从FPGA获取故障波形数据和时标信息。由于PIC18F8520的EMI接口中16bit数据线和低16bit的地址线共用,与FPGA之间不能直接相连,接口连接如图3所示。

故障定位装置的程序设计

故障定位装置的程序设计包括FPGA的内部逻辑设计和单片机的软件设计。

FPGA内部逻辑设计

FPGA的内部逻辑通过Altera公司的Quartus II集成环境,采用Verilog HDL硬件描述语言开发设计,分为以下几个模块。

(1)时钟信号生成模块:将50MHz的输入时钟通过计数器分频得到需要的时标标定电路的时钟信号、ADC转换时钟信号等系统需要的各种频率的时钟信号。

[p](2)A/D控制模块:控制A/D转换芯片进行A/D转换。

(3)故障判定模块:将A/D转换得到的数字信号瞬时值与预设的门槛值比较,判断是否发生故障。

(4) 延时模块:产生故障发生后大约10ms的延时信号。

(5)SRAM控制模块:将采样数据写入SRAM;2片SRAM之间的总线切换;读出S M中的数据送往MCU。

单片机软件设计

单片机程序在MPLAB IDE8.10环境下,采用MPLAB C18编译器,用C语言编程实现,主要包括下述功能:

(1)对GPS模块的初始化、配置以及从GPS模块获取精确到秒级的时间信息(年、月、日、时、分、秒);

(2)通过EMI接口从FPGA中获取故障波形数据和精确到微秒的时标信息;

(3)通过USART接口对DTU进行设置以及将故障波形数据和完整的时标信息通过DTU上传。

结语

本文介绍的基于暂态行波定位原理的10kV配电网故障定位装置,通过实验证明,MCU+FPGA的设计方案可以很好地解决高速数据采集和顺序任务控制间的矛盾,实现高速数据采集和其他任务的并行处理,经测试,电路运行良好,可以达到设想的要求,具有一定的实用价值。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:电感的磁学知识详解

下一篇:浅谈LED照明电器的检测与认证