- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

一种基于CPLD的QDPSK调制解调电路设计

随着无线通信频带资源的日益紧张,研究和设计自适应信道调制技术体制是建立宽带移动通信网络的关键之一。在宽带CDMA系统中的前向和上行链路都使用的QDPSK(四相相对相位调制)技术它是一种宽带和功率相对高效率的信道调制技术,因此在自适应信道调制技术中得到了较多应用。四相相对相位调制和解调,大多采用计算机仿真实现或者理论算法研究,具体应用电路较少。CPLD(复杂可编程逻辑器件)采用E2CMOS工艺制作,一般由3种可编程电路组成,即可编程逻辑宏单元,可编程输入/输出单元和可编程内部连线。它可利用EDA技术中的MAX+PLUSII作为开发工具,将设计的电路图或硬件描述语言编写的程序综合成网表文件写入其中,制成ASIC芯片。利用CPLD的突出优点设计的QDPSK调制解调电路集成度高,数据速率快,同时具有较大的灵活性和实用性。

1 QDPSK调制解调的原理

QPSK(四进制绝对移相键控)与2PSK不同,是利用载波的4种不同相位来表征数字信息,即对输入的二进制数字序列先分组,将每2个比特编为一组,然后用4种不同的载波相位进行表征。

在2PSK(二进制绝对移相键控)信号相干解调过程中会产生180°相位模糊,同样,对QPSK信号相干解调也会产生相位模糊问题,并且是0°、90°、180°和270°等4个相位模糊。因此,在实际中更实用的是四相相对移相调制,即QDPSK方式。

QDPSK信号是利用前后码元之间的相对相位变化来表示数字信息。实现四相差分移相调制的方法有正交调幅法和相位选择法。相位选择法QDPSK调制器具有硬件实现简单、价格低等优点,被广泛采用,并且这种调制器非常适合数字电路实现。图1为用相位选择法产生QDPSK信号的组成框图。

图1中首先把二进制数据流经串/并变换,割裂成并列的2行,每串数据的速率是原数据速率的一半;然后对2路信号进行差分编码;四相载波发生器分别送出调相所需的4种不同相位的载波。按照串/并变换器输出的双比特码元的不同,逻辑选相电路输出相位的载波。

例如,如果输入的二进制数字信息序列为1001001110…,则可以将它们分成10,01,00,11,…,由于每一个载波相位代表2个比特信息,所以每个四进制码元又被称为双比特码元。差分编码后双比特码元cd为11时,输出相位为0°的载波;cd为01时,输出相位为90°的载波;cd为00时,输出相位为180°的载波;cd为10时.输出相位为270°的载波。

QDPSK的解调有相干解调加码反变换法(极性比较法)和差分相干解调(相位比较法)。QDPSK相干解调加码反变换法解调框图如图2所示。

图2所示解调原理是:对QDPSK信号进行相干解调,恢复出2路相对码,经过码反变换器变换为2路绝对码,再经过并/串转换器,从而恢复出发送的数字信息。在解调过程中,由于载波相位模糊性的影响,使得解调出的相对码也可能发生倒置,但经差分泽码(码反变换)得到的绝对码不会发生任何倒置的现象,从而解决了载波相位模糊性的问题。

2 基于CPLD的QDPSK调制解调电路

2.1 QDPSK调制电路

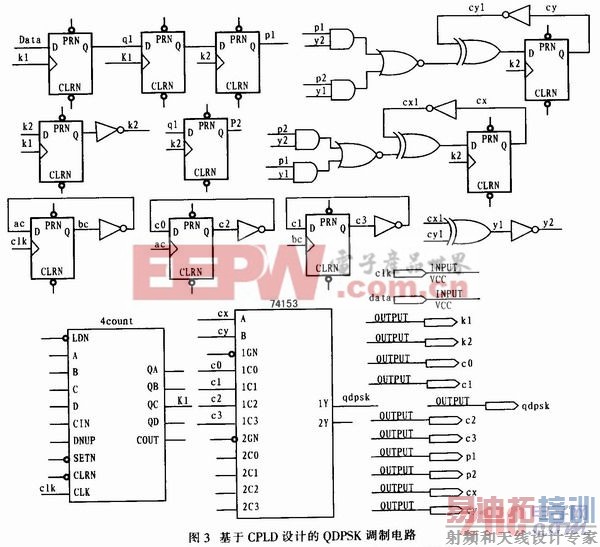

基于CPLD的QDPSK调制电路如图3所示。[p]

图3所示QDPSK调制电路引脚关系为:引脚k1表示数据时钟clk经过计数器4count的八分频输出,引脚k2表示数据时钟k1的二分频输出,引脚ac和bc表示数据时钟clk的二分频输出和二分频反相输出,引脚c0和c2表示数据时钟ac的二分频输出和二分频反相输出,引脚c1和c3表示数据时钟bc的二分频输出和二分频反相输出,c0、c1、c2和c3组成四相载波。引脚p1和p2表示输入信码数据data在时钟的作用下串并转换后的输出。引脚cx和cy表示信码数据串并转换后,在同步时钟的作用下差分编码后的输出,引脚qdpsk表示输入的信码数据在同步时钟的作用下四相差分移相键控信号输出。

图3所示电路器件均可从MAX+PLUSⅡ器件库中调用。其中二分频电路涮用1个D触发器和1个非门组成;串并转换电路调用4个D触发器组成;差分编码电路调用2个二异或门、2个D触发器、4个2与门、2个或非门和2个非门组成:四相选相电路调用1个74153组成。调制电路在MAX+PLUSⅡ平台上编译、仿真通过后,打包产生qdpskb组件。

2.2 QDPSK解调电路

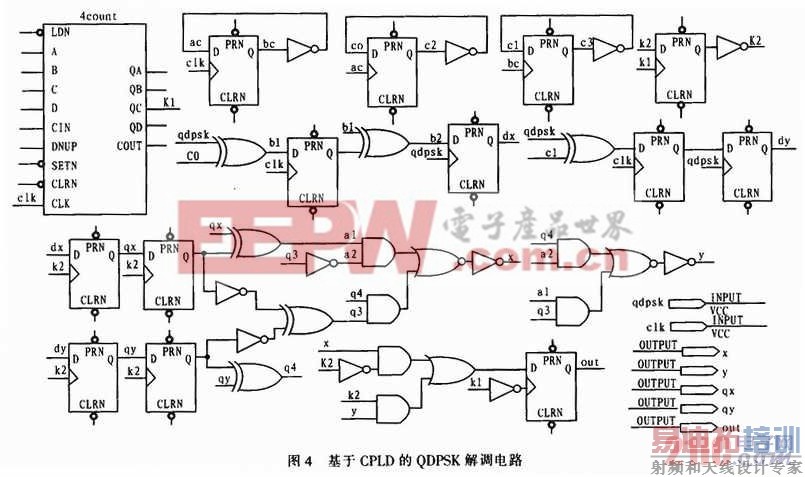

基于CPLD设计的QDPSK解调电路如图4所示。

图4所示QDPSK解调电路引脚关系为:引脚clk表示恢复的数据时钟,引脚k1表示数据时钟clk经过计数器4count的八分频输出,引脚k2表示数据时钟k1的二分频输出,引脚ac和bc表示数据时钟clk的二分频输出和二分频反相输出,引脚c0和c2表示数据时钟ac的二分频输出和二分频反相输出,引脚c1和c3表示数据时钟bc的二分频输出和二分频反相输出,c0、c1、c2和c3组成四相载波。引脚qdpsk表示四相差分移相键控信号输入,引脚qx和qy表示四相差分移相键控信号的相干解调输出。引脚x和y表示相干解调输出在同步时钟的作用下差分译码后的输出,引脚out表示信码差分译码后经并串转换恢复的信码数据输出。

电路器件从MAX+PLUSⅡ器件库中调用。其中二分频电路调用1个D触发器和1个非门组成;相干解调电路调用3个异或门、6个D触发器组成;差分译码电路调用2个D触发器、3个异或门、5个非门、4个与门和2个或非门组成;并串转换电路调用2个非门、2个与门、1个或门和1个D触发器组成。解调电路在MAX+PLUSⅡ平台上编译、仿真通过后,打包产生qdpsky组件。[p]

2.3 利用CPLD设计的QDPSK调制解调电路

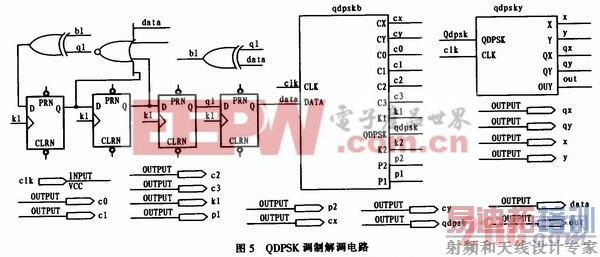

将设计的QDPSK调制电路“qdpskb”组件和解调电路“qdpsky”组件连接在一起,为了仿真实验方便,信码数据输入采用四级伪随机码电路——从MAX+PLUSⅡ器件库中调用4个D触发器、2个异或门和1个四或非门,解调电路中位定时恢复电路产生的数据时钟直接采用qdpsk调制电路数据时钟,调制解调电路直接相连,组成的QDPSK调制解调电路如图5所示。

QDPSK调制解调电路的引脚关系为:引脚clk表示数据时钟输入,引脚k1表示数据时钟clk的八分频输出,引脚data表示四级伪随机码电路数据输出,引脚c0、c1、c2、c3表示四相载波。引脚p1和p2表示信码数据data在时钟的作用下串并转换后的输出,引脚cx和cy表示差分编码后的输出,引脚qdpsk表示四相差分移相键控信号输出。引脚qx和qy表示四相差分移相键控信号的相干解调输出,引脚x和y表示差分译码后的输出,引脚out表示信码差分译码后经并串转换恢复的信码数据输出。

3 实验结果

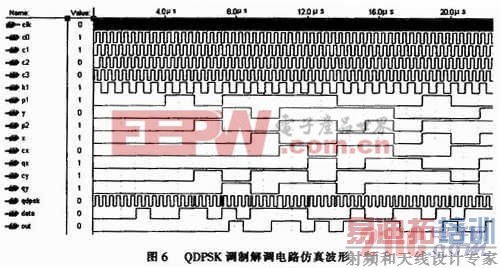

利用MAX+PLUSⅡ开发工具建立波形输入文件,在File菜单里面选择New打开新建文件类型对话框,选择Waveform Editor File项,单击“OK”。在波形编辑器窗口的Name下单击鼠标右键,出现浮动的菜单,选择Enter Nodesfrom SNF…可以打开“从SNF文件输入观测点”的对话框。在Type区选择Input和Output,在默认的情况下是打开的,单击“List”按钮,可在Available Nodes&Groups区看到设计文件中使用的输入/输出信号,单击“=>”按钮可以将这些信号选择到Selected N0des&Groups区。单击“OK”按钮,关闭对话框即可看到波形编辑窗口,将此波形文件保存为默认名。在波形文件中添加输入/输出信号名后,就可以开始对输入信号建立波形了。QDPSK调制解调电路仿真波形如图6所示。

示波器测试调制解调电路输出,实测结果完全正确,表明达到了设计要求。

示波器测试调制解调电路输出,实测结果完全正确,表明达到了设计要求。

4 结论

本文利用CPLD器件,设计出的QDPSK调制解调电路,利用了EDA技术中的MAX+PLUSⅡ作为开发工具,将设计的电路图综合成网表文件写入其中,制成ASIC芯片。其突出优点是自顶向下设计,查找和修改错误方便,同时先仿真,正确后再下载测试并应用,具有较大的灵活性;调制和解调放在一块芯片上,集成度非常高;解调电路输出数据延时约5.2μs,数据速率快。本文提出的QDPSK调制解调电路,已应用于小型数据传输系统中。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:华明FJK-1型漏电断路器原理分析

下一篇:一种基于开关电容技术的锁定放大器设计