- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于可编程计数器的时序逻辑电路设计

各种MSI中规模数字集成电路都有自己的主要特性和应用目标,如果进行非常规使用,则改变它的使用方向,就可进一步发挥其功能和作用。扩展专用集成电路的应用领域是一项有实际意义的研究。本文研究了MSI可编程计数器改变应用方向的逻辑修改方法及时序逻辑电路的设计技术。

1 基本原理

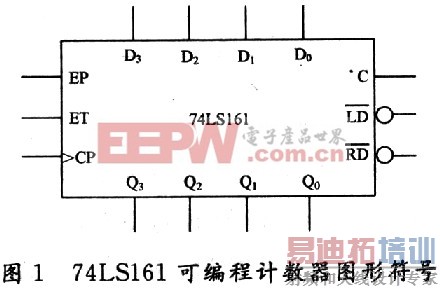

74LSl61是可编程中规模同步4位二进制加法计数器,图1为其图形符号。其中,Q3,Q2,Q1,Q0为计数状态输出端;C为进位输出端;EP,ET为计数控制端;

表1为可编程计数器74LSl61的功能表。

由表1可知,在![]() 条件下,74LSl61可编程计数器由EP,ET及

条件下,74LSl61可编程计数器由EP,ET及![]() 控制具有计数、预置数和保持三种功能。

控制具有计数、预置数和保持三种功能。

用74LSl61可编程计数器Q3Q2Q1Q0端的代码组合表示时序逻辑电路的各个状态,由输入变量控制EP,ET及![]() 端,综合利用计数、置数、保持功能,使计数器的状态变化满足所要求的时序,即用计数功能实现“次态=现态+l”的二进制时序关系,用预置数功能实现“次态=预置数”的非二进制时序关系,用保持功能实现“次态=现态”的自循环时序关系,可实现一般时序逻辑电路。

端,综合利用计数、置数、保持功能,使计数器的状态变化满足所要求的时序,即用计数功能实现“次态=现态+l”的二进制时序关系,用预置数功能实现“次态=预置数”的非二进制时序关系,用保持功能实现“次态=现态”的自循环时序关系,可实现一般时序逻辑电路。

1.1 可编程计数器状态转换对控制函数的要求

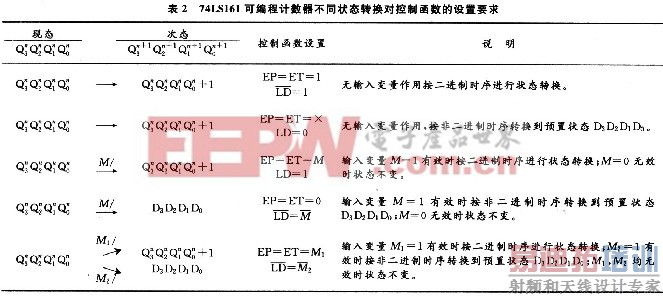

由表1所示的功能表,可确定74LSl61可编程计数器各种状态转换时对控制函数的要求,如表2所示。

1.2 基于可编程计数器时序逻辑电路的基本形式

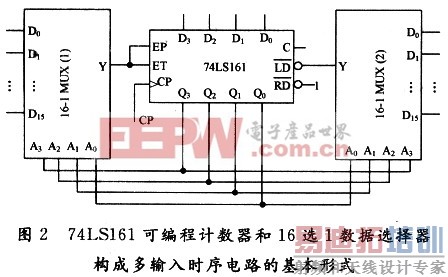

用1个74LSl61可编程计数器和2个16选1数据选择器可构成多输入时序逻辑电路的基本形式,如图2所示。

[p]

图2中,74LSl61计数器的现态输出![]() 作为数据选择器的选择控制变量,数据选择器的Y输出作为74LSl61可编程计数器的EP,ET计数控制信号及

作为数据选择器的选择控制变量,数据选择器的Y输出作为74LSl61可编程计数器的EP,ET计数控制信号及![]() 预置数控制信号,数据选择器的输入端D0~D15作为所构成时序网络的外部信号输入端。

预置数控制信号,数据选择器的输入端D0~D15作为所构成时序网络的外部信号输入端。

74LS161可编程计数器处于不同现态时通过数据选择器选择不同的外部输入信号作用于EP,ET及![]() 端,对74LSl61可编程计数器的基本工作时序进行修改,在时钟脉冲CP的作用下,使计数器的输出状态按所要求的时序关系进行改变,即可实现状态个数不超过16个的一般时序逻辑电路。

端,对74LSl61可编程计数器的基本工作时序进行修改,在时钟脉冲CP的作用下,使计数器的输出状态按所要求的时序关系进行改变,即可实现状态个数不超过16个的一般时序逻辑电路。

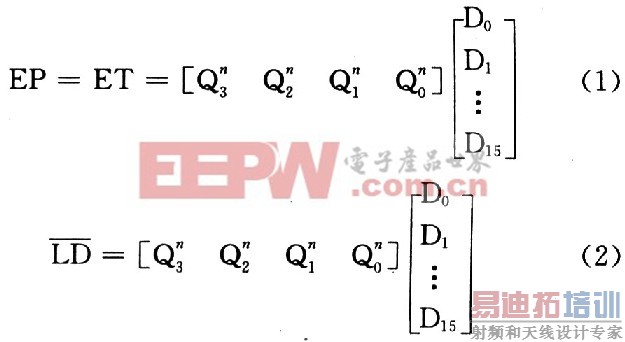

74LS161可编程计数器的EP,ET及![]() 控制函数可写成如下矩阵形式:

控制函数可写成如下矩阵形式:

如果所实现的时序逻辑电路其状态个数不超过8个,可使用74LSl61可编程计数器的低3位和2个8选1数据选择器进行组合。

如果所实现的时序逻辑电路其状态个数不超过4个,可使用74LSl61可编程计数器的低2位和2个4选1数据选择器进行组合。

由状态转换关系,依表2确定式(1),式(2)中输入矩阵的参数。

1.3 时序逻辑电路的输出函数

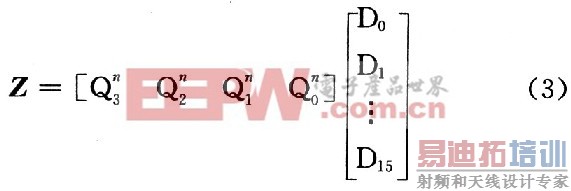

所设计的时序逻辑电路为Mealy型时,输出是现态及输入变量的函数,可写成式(3)所示的矩阵形式并用数据选择器实现,由各状态的输出要求确定式(3)中输入矩阵的参数。

所设计的时序逻辑电路为Moore型时,输出仅是现态的函数:

![]()

用卡诺图化简求出最简输出逻辑表达式,用逻辑门实现。

当每态对应一个不同的输出函数时,可用二进制译码器实现输出函数。

1.4 基于可编程计数器时序逻辑电路的设计

一般设计步骤:

(1)作出状态图

使用MSI可编程计数器及数据选择器设计时序逻辑电路时,状态的简化通常不会简化电路结构,一般不进行状态简化,直接使用原始状态图进行设计,可使各个状态所表示的含义清楚,电路与所实现的逻辑功能之间的对应关系较为明确。

(2)状态分配

进行状态分配时,尽量使用不需进行预置数的二进制时序,尽量对非二进制时序作相邻分配,以利于预置数的简化。

(3)求出EP,ET及![]() 的矩阵式,用卡诺图化简求出预置数最简逻辑表达式,求出输出函数逻辑表达式。

的矩阵式,用卡诺图化简求出预置数最简逻辑表达式,求出输出函数逻辑表达式。

(4)画出逻辑图。

2 设计举例

一个同步时序逻辑电路,输入信号为M1,M2。当M1连续输入4个或4个以上的1时,然后M2输入1个1时,输出Z为1,M1,M2不同时输入1。

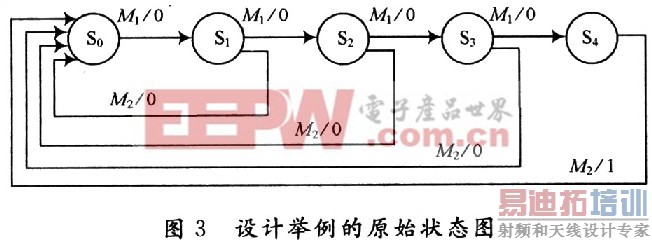

由设计要求作出原始状态图如图3所示。其中,S0状态表示起始;S1状态表示M1输入了1个1;S2状态表示M1输入了2个1;S3状态表示M1输入了3个1;S4状态表示M1输入了4个或4个以上的1。

图3中有S0~S4共5个状态,使用74LSl61可编程计数器的低3位代码进行状态分配,按尽量使用二进制时序的分配原则,状态分配关系为:S0:000;S1:001;S2:010;S3:011;S4:100。

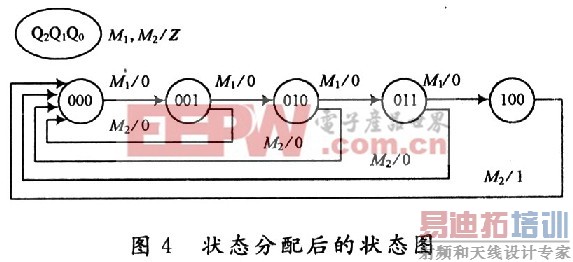

状态分配后的状态图如图4所示。

[p]

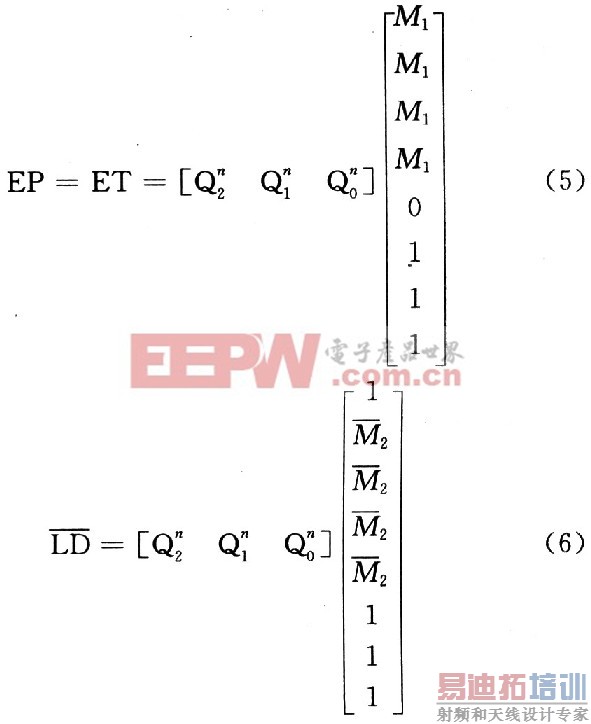

由图4及表2,写出74LSl61计数器的EP,ET及![]() 矩阵方程式:

矩阵方程式:

其中,不使用的101,110和111状态,将EP,ET及![]() 均设置为1,使计数器处于二进制时序状态工作,能自启动。

均设置为1,使计数器处于二进制时序状态工作,能自启动。

作出74LSl61计数器预置输入变量的卡诺图及画包围圈化简如图5所示,各预置输入变量的最简逻辑表达式为:

![]()

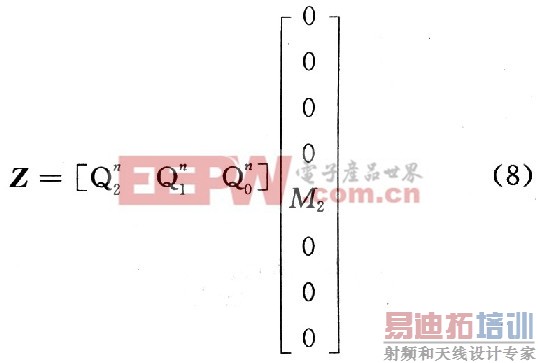

由图4所示的状态图,写出输出函数Z的矩阵方程式:

其中,不使用的101,110和111状态的输出设置为O,亦可设置为1。

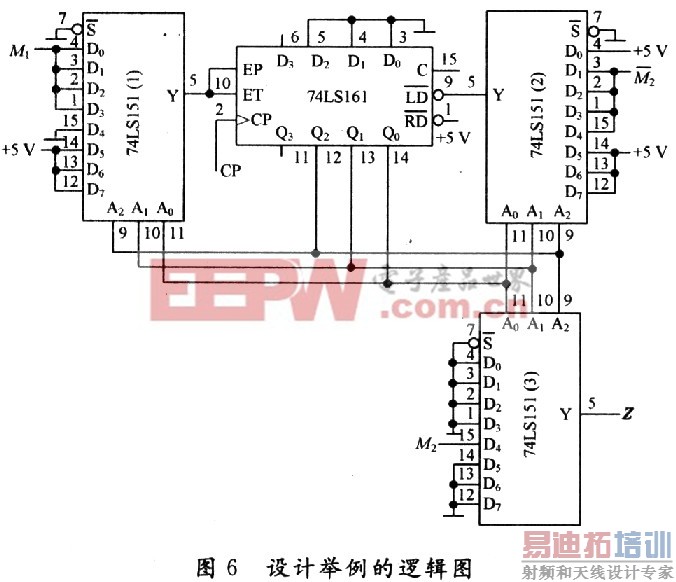

用1个74LSl61可编程计数器,3个8选数据选择器74LSl51按式(5)~(8)画出逻辑图如图6所示。

3 结语

基于可编程计数器的时序逻辑电路设计技术,提出了设计一般时序逻辑电路的状态分配原则及设计步骤,具有实际应用意义。

需要指出,当用单片74LSl61可编程计数器控制EP,ET及![]() 构成模数N16的任意进制计数器时,无输入变量,所用状态仅最后一个是非二进制时序,其余均为二进制时序。由功能表可知,需将EP,ET设置为常数1且不需选择,可将图2所示的一般结构中控制EP,ET的数据选择器简化掉,而

构成模数N16的任意进制计数器时,无输入变量,所用状态仅最后一个是非二进制时序,其余均为二进制时序。由功能表可知,需将EP,ET设置为常数1且不需选择,可将图2所示的一般结构中控制EP,ET的数据选择器简化掉,而![]() 控制函数仅在最后状态为O,可用门简单控制。

控制函数仅在最后状态为O,可用门简单控制。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...