- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速ADC采集系统电路设计的考虑及分析

摘要:高性能ADC采集系统前端电路的设计及ADC本身固有的特点对系统性能的影响至关重要,优化高速采样系统设计取决于很多因素,包括应用性质、系统组成和ADC的结构,本文主要介绍了使用放大器或变压器作为ADC前端电路以及ADC芯片固有特点对系统性能的影响分析。

关键词:模数转换;前端电路;系统性能;阻抗匹配;信噪比

0 引言

在高速中频采样电路系统设计中,低噪声、最大限度的控制波形的畸变、低功耗、良好的增益控制、高度的通带平坦性、最大传输功率、输入驱动能力及最低的幅相失衡等因素是设计师在设计采样电路时追求的优化设计指标,而这些指标的获得和提高取决高速AD采集系统的各个电路环节,本文从高速采集系统中前端调理电路的设计、系统参数的考虑、ADC固有的电路特性以及输入信号的形式等多个方面对系统性能的影响作出了综合性的分析、比较和论证,希望能够对高速采集系统的设计工作起到一定的借鉴和指导作用。

1 放大器或变压器前端调理电路对系统设计的影响分析

1.1 放大器和变压器作为前端调理电路的根本区别

放大器是有源器件,而变压器是无源器件。放大器和其它所有有源器件一样,消耗功率并且产生噪声,变压器不消耗功率并且产生的噪声可以忽略不计。两者均涉及到动态效应问题。

1.2 放大器和变压器作为前端调理电路的优缺点

放大器作为前端调理电路,其性能限制比变压器少,如果必须保持直流(DC)电平,就必须使用放大器,因为变压器是固有的交流(AC)器件。另外,放大器在提供电路的增益方面较变压器容易,因为放大器的输出阻抗实质上与增益无关。另一方面,放大器在通带范围内能够提供平坦的响应,而没有由于变压器寄生交互作用引起的纹波。这些因素均是放大器作为采样前端调理电路优于变压器的方面。

变压器作为无源器件,低功耗、低噪声是其无可比拟的最大优点,当信号的频率很高而且ADC的输入端不允许很大的附加噪声时,变压器具有超越放大器的最大性能优势,此外,在考虑到带宽与噪声的折中方面,如果采用的频率高于150 MHz,变压器在保持SNR和SFDR等方面会较放大器更为出色。

1.3 放大器或变压器前端调理电路选用时所需考虑的因素

前面介绍了两种采样前端调理电路的本质区别及各自的优缺点,但是我们在具体电路设计时只能选择其中一种作为实际的前端调理电路,本文将究竟选择变压器还是放大器来驱动ADC的考虑因素及优选方案,归纳为表1所示。

[p]

2 系统参数对系统设计的影响分析

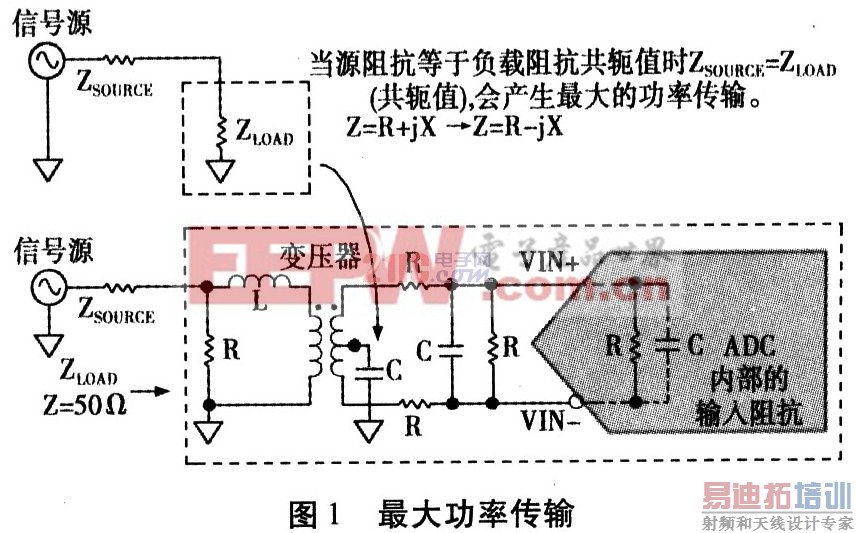

首先,我们在设计高速ADC采样系统电路时,重要的是要考虑到所有的参数,要把每一个元件当作前一级负载的一部份来考虑,并且当源阻抗等于负载阻抗的共轭(见图1)时,会产生最大的功率输出。

下面重点分析系统参数对系统设计的影响:

(1)输入阻抗:输入阻抗是系统设计的特性阻抗,大多数情况下输入阻抗为50 Ω,但可能会要求其它取值。变压器是具有很好互阻性能的器件,其允许用户根据需要耦合不同特性阻抗并且充分平衡系统的总负载。在放大器的设计电路里,阻抗被定义为输入阻抗和输出阻抗,放大器的阻抗特性不像变压器那样随频率变化。

(2)电压驻波比(VSWR):电压驻波比是一项无量纲参数,用来表示在有用带宽内输入功率反射到负载上的比率。当负载ADC达到满度输入时,VSWR是一项用来确定所需要的输入驱动能力的重要参数。

(3)通带平坦度(或者增益均匀性):通带平坦度指在规定带宽内增益响应随频率的变化量(包括正波动和负波动),它可能会表现为波动,或者像Butterworth滤波器那样简单单调地下降,不管是哪一种情况,通常要求通带平坦度小于或等于1 dB,这对于稳定总系统增益至关重要。

(4)输入驱动能力:输入驱动能力是由特定应用需要的系统增益决定。输入驱动能力与带宽指标密切相关,并且依赖于所选择的前端元件,例如滤波器、放大器或者变压器,它们的特性是使输入驱动能力最难达到要求水平的原因之一。

(5)信噪比(SNR):信噪比是在给定带宽内,满度信号的有效值与全部噪声分量平方和的平方根的对数比,但是这不包括失真分量,从前端方面来看,SNR会随着带宽、时钟抖动和增益的增加而降低,在高增益情况下,放大器在低增益时可能被忽略的噪声分量会产生明显作用。

(6)无杂散动态范围(SFDR):无杂散动态范围是满度值的有效值与最大杂散频谱分量的有效值之比。前端杂散有两大危害,一个是造成放大器的非线性(或者使变压器造成不理想平衡),它主要产生二次谐波失真;另一个是输入失配,并且按照一定的增益放大这种失配(在高增益情况下,失配更加严重,并且放大寄生非线性作用),通常将这种情况看作三次谐波失真。

3 ADC固有电路的选择对系统设计的影响分析

3.1 开关电容型ADC电路特性对系统设计的影响

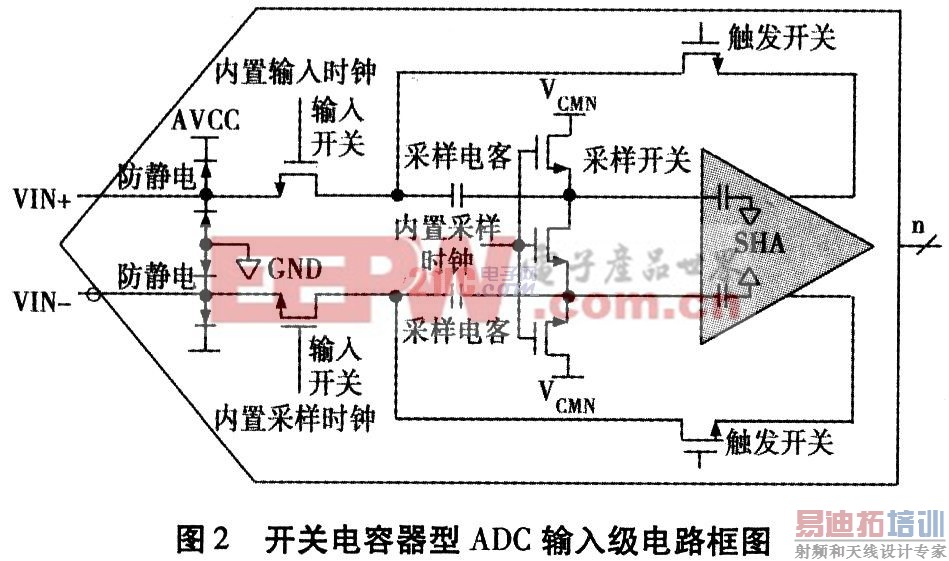

目前流行的CMOS开关电容ADC没有内置的输入缓冲器,所以其功耗比带缓冲器的ADC要低一些。外部信号源直接连接到ADC的内置开关电容采样保持(SHA)电路(见图2)。这会产生两个问题:第一,输入阻抗随时间变化,因为工作方式在采样和保持之间不断切换;第二,注入到采样电容器的电荷会反射回信号源,这可能引起驱动电路里的无源滤波器的过渡延迟。

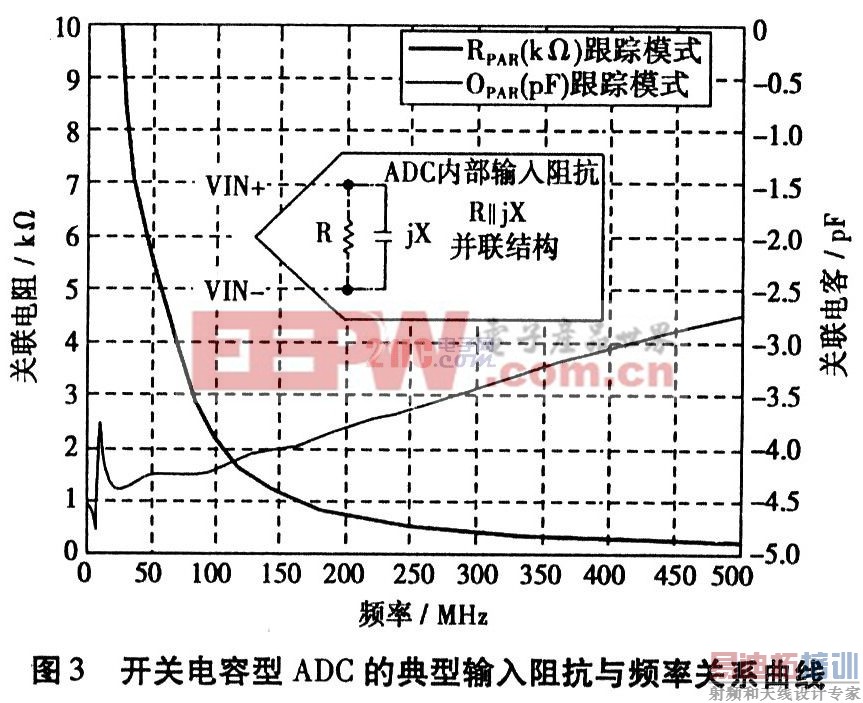

更为重要的是把外部网络阻抗与ADC跟踪模式阻抗匹配具有相当的难度,如图3所示,输入阻抗的实部或阻性阻抗(用蓝色线表示)在低频段(基带)非常高(在几千欧姆范围内),在超过100 MHz的频段下降到2 kΩ以下。输入阻抗的虚部或容性阻抗(用红色线表示),一开始从一个相当高的容性负载,然后在高频段减小大约3 pF。要匹配这样的输入阻抗是一个相当具有挑战性的设计问题,尤其是在频率高于100 MHz的情况下。

[p]

3.2 输入缓冲器型ADC电路特性对系统设计的影响

输入缓冲器型的ADC比较容易理解和使用。输入源阻抗固定,缓冲器由晶体管组成,它以低阻抗驱动ADC,所以大大地减少了注入电荷和开关管引起的尖峰。与带开关电容的ADC不同,输入阻抗在模拟输入频率范围内变化很小,所以选择合适的驱动电路相对容易一些。带缓冲器的ADC特别适合于高线性、低噪声应用;它唯一的缺点是由于它自身的功耗导致ADC总功耗增加。

4 输入信号形式对系统性能的影响分析

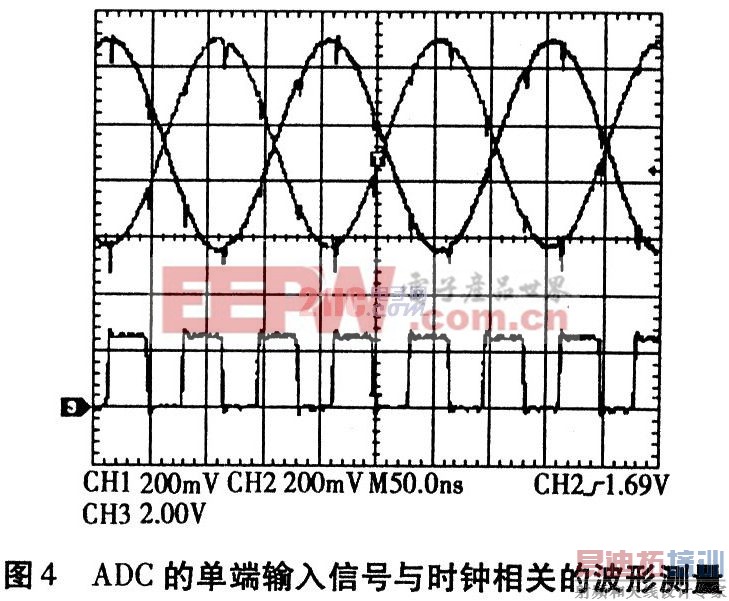

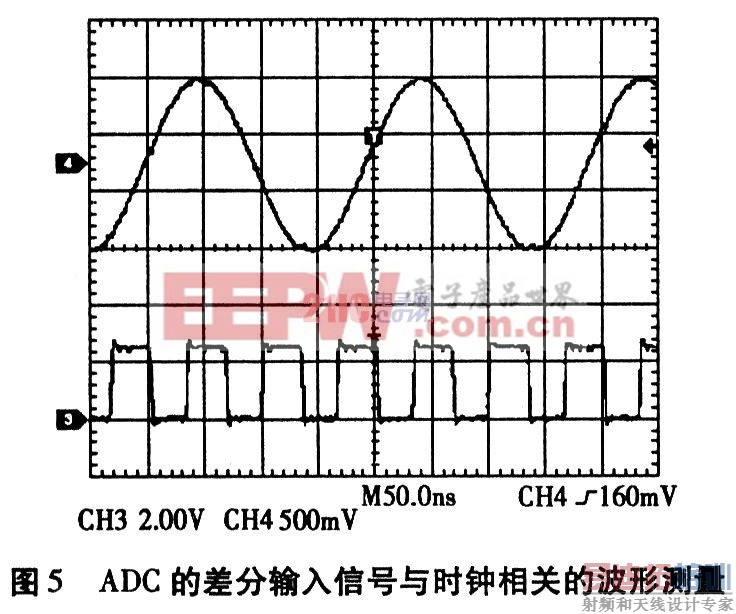

输入信号的形式对于高速采集系统的性能影响至关重要,图4、图5分别给出了单端输入信号和差分输入信号与时钟相关的波形测量图。

图4中示出的ADC的单端输入波形看起来很差,有很多与时钟相关的尖峰干扰,但是,图5证明了单端输入波形受到的干扰几乎完全是由于共模电压的影响。从图5中看出差分形式的输入信号要干净很多,与时钟相关的尖峰干扰消失了。差分信号固有的共模抑制特性能够消除共模噪声,包括来自电源、数字源和电荷注入引起的共模噪声。

5 结论

通过以上对高速ADC采集系统的性能分析,我们认为构成高速采集系统的各个环节,甚至包括ADC器件的固有特性均会对整个高速采集系统的性能造成很大的影响,只有经过对各环节的电路特性进行充分的综合分析和对比,从系统的角度对电路的设计作出正确的选择才是设计出相对完美的高速采集系统的唯一正确途径。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于Topswitch的单片开关电源效率技术方案

下一篇:用仿纹波模式实现降压转换