- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

14位Pipeline ADC设计的带隙电压基准源技术

目前,基准电压源被广泛应用与高精度比较器,A/D,D/A转换器,动态随机存储器等集成电路中。基准电压源是集成电路中一个重要的单元模块。

它产生的基准电压精度,温度稳定性和抗噪声干扰能力直接影响到芯片,甚至整个系统的性能。特别是在D/A,A/D数据转换系统中,基准源的性能与量化器的量化精度密切相关。随着D/A,A/D精度的不断提高,精确稳定的基准源的设计成为关键。因此,设计一个高性能的基准电压源是具有十分重要的意义。

1 分析电路设计及原理

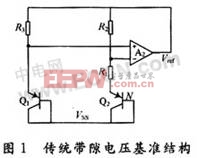

1.1传统带隙基准的分析

传统的带隙电压基准结构中,通过具有正温度系数的VT和一个具有负温度系数电压VBE的线性组合,在输出端得到一个对温度恒定的稳定输出Vref。图1是一个传统的带隙基准电压源。但是在实际应用中,补偿Vref中得不到补偿的高阶电压分量是设计的关键。高阶温度系数主要来自于双极晶体管的温度特性。

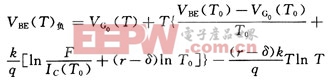

经过整理得到:![]()

根据上式可知在大部分工艺下,通过调节电路,一阶系数项可以很容易消除。但是由于工艺参数r的值和由电阻引入的系数δ不能很好的抵消,使得高阶电压分量仍然存在。即C2项不可能消除,导致温度系数不能达到足够低。

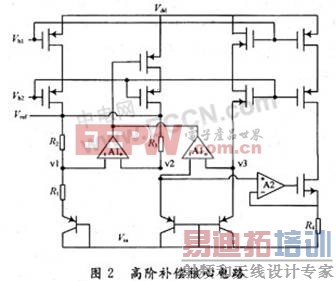

1.2改进的高阶补偿带隙基准源

为了得到温度系数足够低的带隙基准源,高阶温度系数需要进一步补偿,补偿的方法如图2所示的电路结构。在传统的电路基础上,加入补偿电路结构:由于运放A3的增益很大,运放强制Q2和R4的端电压相等,则I4=VBE,Q2/R4,电流镜使流过晶体管Q3的电流:![]()

从而在Q2,Q3的VBE之间产生一个差值Tln T项。这个差值项通过运放gm1,gm2被引入到IR1中来修正VBE,Q1中的高阶项。

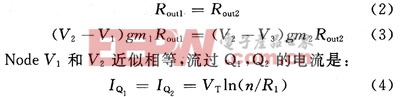

在图2中,输入端连接V1,V2和V2,V3的四输入运放,其输出端连接在一起,因此他们具有相同增益A1,各参数完全相同,即输出阻抗也相同:

对于管子Q1,Q2,他们完全相同,所以他们的端电压只和他们集电极流过电流相关。

令![]() (常数B1,B2由电阻阻值,温度系数和管子VBE电压控制;gm1,gm2是运放A1的输入端跨导,由输入对管子的宽长比和静态工作点决定)在实际设计中,通过调节gm1,gm2来调节降低高阶项,调节R4来消除一阶项。最后进行反复优化可以获得很好的温度系数。

(常数B1,B2由电阻阻值,温度系数和管子VBE电压控制;gm1,gm2是运放A1的输入端跨导,由输入对管子的宽长比和静态工作点决定)在实际设计中,通过调节gm1,gm2来调节降低高阶项,调节R4来消除一阶项。最后进行反复优化可以获得很好的温度系数。

1.3整体电路分析

这里提出的电路结构如图3所示。系统由四个模块组成:省功耗和偏置电路、运放、基准电压输出模块和高阶曲率补偿。基准核心结构和高阶曲率补偿电路部分的工作原理在前面分析的改进带隙基准中有重点讲过。图3左边所示的功耗控制开关VC1,当VC1为低电平(0)时,M6导通,M4关闭,则M7栅极点电位为高,M7关闭,则M7支路电流为0,电流镜M10,M11镜像M7支路电流,导致差分放大器的尾电流为0,差分放大器没有工作,整个电路都没有工作,处于省功耗状态;当VCl为高电平(3.3 V)时,M6关闭,M4导通,则M1到M6组成的偏置电路为M7栅极提供合适的偏置电压。Cascode结构(M8,M9,M10,M11)的偏置是由电压自偏置来实现的。同时M10,M11复制M7支路电流,M12,M13电压自偏置,为尾电流源提供偏置电压。该偏置电路提供一级折叠式共源共栅运放电路中所用的所有偏置电压。在实际电路中,为了满足匹配,偏置电路中管子的长度应该与运放中相应的管子长度相等。

运算放大器是带隙电压基准源电路中的关键部分之一,其环路增益和电路的失调决定了基准源输出的精度和稳定性。为了增加电路的稳定性和降低电路的复杂度,在此尽量采用具有高增益的单级运放,而不采纳二级补偿运放。高增益的单级运放包括套筒式和折叠式运放两种,由于运放连接反馈回路,套筒式运放因输出摆幅太小而不使用,在此使用折叠式运放。

2 仿真结果分析

图3所示电路用0.35μm BSIM 3v3 CMOS工艺,用Cadence Spectre软件模拟得到以下的仿真结果。

2.1基准输出与电源电压关系

图4是基准输出与电源电压(0~3.3 V)关系曲线。仿真结果表明:这种带隙基准电压源结构在正常工作状态下的最小电源电压可达1.6 V,输出基准电压Vref=(1.174 43±0.000 43 V),在-40~+100℃范围内,带隙基准电压源输出电压的温度系数rTC=2.077 ppm/℃。在25℃,3.3 V下,功耗不到110μW(电路总功耗为109.89μW)。在25℃,1.6 V下,功耗不到9μW(电路总功耗为8.453μW)。

对该带隙电压基准源仿真电源电压抑制比(PSRR),得到在3.3 V电源电压下,室温且没有滤波电容时,在100 Hz下为-65 dB。要获得更好的PSRR,可以通过在基准的输出端加一滤波电容来提高PSRR。将Vref经过了一个RC低通滤波电路输出,这样可以改善输出基准电压的电源抑制能力,减小噪声干扰,并且可以减小在电路上电时的基准电压瞬态过冲。[p]

2.2基准输出与温度的关系

图5是典型工艺角下经过高阶曲率补偿的基准电压与温度的关系曲线。由图计算得到在典型(TT)工艺角下,电源电压为3.3 V时,在-40~+100℃工作温度范围内,该基准电压温度系数为2.077 ppm/℃。在整个工作温度范围内,基准输出电压随温度变化不超过±0.15%。另外,由同种工作条件和模拟条件得到该基准在其他两个工艺角温度系数如表1所示。可见,该电路具有很好的温度特性。

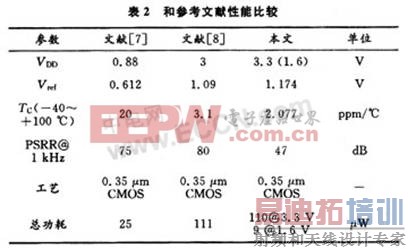

2.3 与参考文献性能比较

与参考文献性能比较如表2所示。

表2为本文设计电路与文献[6]和文献[7]中电路的模拟仿真结果比较。本文电路的供电电压可以低至1.6 V,输出电压1.174 V.在-40~100℃时温漂约为2ppm/℃,且功耗最高不超过110 μW。由此可见,本文设计电路具有低电压低功耗和低温漂的优点,综合性能优异。

3 版图设计

模拟电路的版图设计中器件的匹配以及合理的布局布线对电路性能的影响很大。再考虑到要减小工艺失配的影响,需要对版图进行精心设计。版图设计注意以下几点:

(1)运放的输入管采用大的宽长比例,以减小运放的失调电压,并且其晶体管的沟道要大于工艺最小沟长Lmin。

(2)电路中的关键器件PNP Bipolar晶体管,在实际电路设计中取Q1与Q2的面积比为8:1,然后采用中心对称的设计方法,实现器件的匹配。

(3)集成电路中电阻误差很大,采用电阻分级并联方式,并在电阻周围加上dummy电阻,以减少环境的影响,增强电阻匹配性。

4 结 语

与其他许多高阶曲率补偿带隙电路相比,本文提出的这种带隙基准电压源,具有低电压低功耗和低温漂的优点,且与标准CMOS工艺兼容,结构新颖,综合性能优异,完全符合设计要求。可以很好地应用于高精度比较器、A/D和D/A转换器等模拟集成电路中,该电压源采用0.35μm CMOS工艺,Spectre仿真表明,在-40~100℃时,其温度系数为2 ppm。这种带隙基准可用于14位pipeline ADC中,应用前景广泛。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于FPGA的可编程PWM电路设计

下一篇:以太网供电