- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的可编程PWM电路设计

0 引言

某系统中的H桥驱动电路需要采用2路脉冲宽度调制器(Pulse Width Modulation,PWM)信号来驱动一个电机,以控制其正、反两个方向的运转,且两路信号必须有一定的时间间隔来避免驱动电流过大而损害驱动元件。为使其能灵活应用,针对系统要求,本设计的PWM控制器应具备以下功能:

(1)有3路独立PWM输出,每路输出2个驱动信号,而且其周期、占空比、死区时间应可编程;

(2)对应10 MHz系统时钟,周期为1μs~6.5536 ms;

(3)应用精简地址线,以节省外围引脚及地址资源的占用;

(4)能提供与8/16 bits单片机的双向数据接口,并具有内置的地址/数据锁存器(74lS373)。

1 PWM电路的结构规划

在采用自顶向下(Top_Down)正向设计PWM器件的过程中,芯片的结构划分和规格定制是整个设计的重要环节,因此合理的结构设计将决定整个设计的成败。

PWM输出信号的周期、脉宽、死区时间等参数可以通过加载内部的寄存器来实现,写人PWM芯片的数据分为数据字与控制字两部分。由内部控制逻辑(ControlLogie)模块来处理控制字信息,并译码产生各内部通道的内部信息寄存器片选信号。数据字则通过内部数据总线在各通道模块来传递PWM的特征信息数据。

PWM芯片内部各模块可通过内部片选结合读写使能来完成数据交换。芯片与外围控制器进行数据交换时,可采用双模式接口(8/16 bits),并可通过外置选择引脚DataWidth来选配。

本芯片的核心是由3个完全独立且相同的通道模块(Channel)构成。通道内部的数据接口用于完成外部读写逻辑(RWLogic)传输到内部数据总线的数据收发工作。PWM周期生成模块(ClkGen)则可依据写入的周期信息,输出PWM的周期控制信号。

PWM输出由通道状态机完成,当通道接收到PWM信息数据后,先进行数据校验,合格的数据将在合适的条件下启动状态机,并在不同的状态下完成PWM输出。而不合格的数据则被忽略。

地址/数据锁存依据通用74LS373的逻辑功能,可以通过编写一个完全可替代的L74LS373来实现。

根据上述总体的构建思路,最终给出的芯片总体结构如图l所示。

2 PWM电路的结构设计

从图1所示的PWM电路总体结构可以看出,该PWM电路主要由模块片选译码、控制逻辑、读写逻辑、通道等四个模块组成。[p]

2.1 模块片选译码

该模块主要通过地址信号Addr与片选信号Cs_b的组合逻辑电路生成内部各子模块的片选信号(ControlLogic,3个通道:Channel2,Channel1,Channel0)。

2.2 控制逻辑

该模块主要产生通道内部Regs片选控制信号及各通道的输出控制信号,同时完成精简地址线的操作。

每个通道都包含各自独立的4个16 bits的寄存器,包括正向信号长度、负向信号长度、死区长度、周期长度等。由于控制字寄存器为8 bits,因此.整个芯片至少占用3×4×2+1=25个地址(每个地址存储8 bits数据),传统做法至少需要5根地址线译码,而采用区分数据信息类型(控制字,数据字)的方式则可将地址线精简到2根。相对单片机紧缺的外面地址资源来说,其好处是显而易见的。具体来说,通过对写人ControlRegister(控制字寄存器)的值进行分析,结合数据传输宽度生成内部Regs片选控制信号,就可以通过控制字信息来完成内部Regs的地址译码,同时反馈被操作的寄存器信息到RWLogic模块,从而完成8/16bits的数据读写操作。

值得注意的是,由于PWM内部包含了3个完全一样的独立通道,因此,为了更方便的对控制字进行操作,通过对控制字寄存器的分析,可用控制逻辑电路自动将当前被操作通道的控制寄存器信息存储在对应的控制寄存器中备份。这样既方便在编程中灵活地操作各通道,又可避免读写过程中的误修改非相干通道的控制信息。

2.3 读写逻辑

该模块用于处理外部数据Data[15:0](包括外部为16位或8位数据总线连接方式)到内部DataInternal[15:0]的转换。当DataWidth为1时,采用16 bits的数据传输;当DataWidth为0时,采用8 bits数据传输。通过PWM能完成对外部8 bits或16 bits的信息传输要求,准确的读写内部16bits的Regs。具体实现时,如采用16 bits传输,由于内部数据采用16 bits传输,可以采用每个地址对应16 bits数据,每个数据位一一对应的传输方式;而采用8 bits传输时,由于内部数据采用16bits传输,故可通过分析地址的奇偶特性来确定数据高低字节的存放,也就是通过ControlLogic反馈的字节选择位,来使读写逻辑电路能够自适应地把16 bits的Regs数据信息分割加载到合适的数据通道上,从而完成数据的输入输出控制。

为了精简数据线,实现数据的双向流通,本模块通过片选和读写使能信号所控制的双向三态门接口电路来隔离读写信息。

2.4 通道

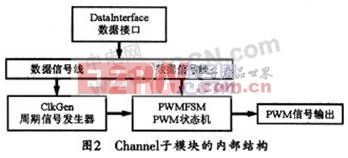

Channel是PWM芯片的核心部分,每个Channel模块都由3个子模块组成,图2所示是各Channel子模块的内部结构图。

2.5 数据接口

数据接口用于完成通道内寄存器的读写功能。该模块通过组合通道片选、内部寄存器片选信号及模块读写使能信号来产生各寄存器的读写使能信号。其读写操作可通过三态门与内部数据通道进行数据交换。

写入本模块的寄存器信息将进行数据校验。只有校验合格的数据才能载入内部寄存器的一级缓冲器(Buf)中,内部寄存器的一级缓冲器(Buffer)数据将输出到PWMFSM模块,以提供PWM的特征数据。

2.6 周期信号发生器

周期信号发生器可生成PWM的周期控制信号,其周期的长短由数据接口传过来的周期寄存器值(CyeleReg)决定。该模块将通过内部计数器计数时钟,并与CycleReg比对,从而产生PWM的周期控制信号CycleScale。

2.7 状态机

状态机是产生PWM信号的核心功能模块。通过加载Data Interface模块接收到的通道内部寄存器Buffer值,由状态机来进行运转。PWMFSM模块中包含有一个自运转状态机。当符合条件的寄存器值写入Channel寄存器后,状态机将在CycleScale信号的起始信息的引导下,在时钟的上升沿将内部寄存器一级Buffer写入到本模块中的PWM信息寄存器Buf中,以便在下一个运行周期内载入到PWM的状态机中。状态机启动后,它将根据当前状态输出脉冲驱动信号。其状态机的运转图如图3所示。

其运转流程如下:

(1)从复位或停止工作状态进入IDLE状态;

(2)在合法的数据写入通道寄存器且CycleScale的启始信号被接收后,状态机将当前通道内部寄存器Buffer的值载人状态机定时器,同时进入正向脉冲状态,以便准备输出正向电机驱动信号;

(3)在正向脉冲状态下,定时器开始减计数,直到到达完成正向驱动所需要的时间,同时在结束正向驱动的输出后,进入死区状态;

(4)在死区状态,关闭正向、负向电机驱动信号,并通过定时器等待死区时间结束,然后进入负向电机驱动状态(负向脉冲);

(5)在负向脉冲状态下,定时器开始减计数,直到到达完成负向驱动所需要的时间,到在结束负向驱动的输出后,进入死区状态;

(6)在死区状态,关闭正向、负向电机驱动信号,并通过定时器等待死区时间结束,然后进入空闲等待状态。等待下一次的启动信号。[p]

3 PWM编程

PWM的工作模式由外部引脚与内部控制字寄存器决定。

3.1PWM芯片的工作模式

PWM芯片的工作模式可由PWMh_b来设定:

当其为1时,为全局使能输出,此时为正常工作模式,但各Channel工作模式可取决于其PWMEN位的值;而当PWMh_b为0时,全局禁止输出,此时整个芯片不工作,芯片进入低功耗模式,同时时钟被禁止输入到内部通道模块。

3.2 PWM芯片的控制字寄存器

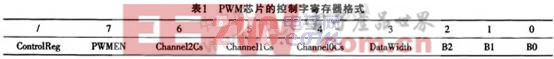

对于控制字寄存器ControlReg[7:0]:在其地址[A1,A0]=00的情况时,其操作格式如表1所列。

由于控制字寄存器仅有一个,但实际各通道都有一个备份的控制字寄存器来控制对应的通道。因此并不会由于对某通道控制字的操作而影响其它无关的通道。本格式中的各位定义如下:

由于控制字寄存器仅有一个,但实际各通道都有一个备份的控制字寄存器来控制对应的通道。因此并不会由于对某通道控制字的操作而影响其它无关的通道。本格式中的各位定义如下:

PWMEN:当芯片全局使能输出时,此位可决定各通道PWM的输出使能,当PWMh_b为1时,各通道的输出正常,为0时,则通道禁止输出;

Channel2Cs:选通Channel2。使能对Channel2模块的操作,并将控制字信息存储到通道2的备份控制字;

ChannellCs:选通Channell。使能对Channell模块的操作,并将控制字信息存储到通道1的备份控制字;

Channel0Cs:选通Channel0。使能对Channel0模块的操作,并将控制字信息存储到通道0的备份控制字;

[B2,B1,B0]:内部寄存器片选译码。每个通道的PWM内部都有8个寄存器地址。通过ChannelX的选通结合[B2,B1,B0]的译码,可产生内部通道Regs的片选信号。

3.3 PWM编程

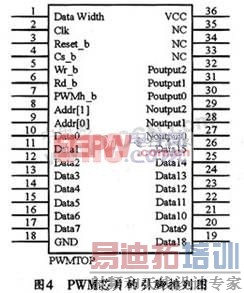

PWM芯片的引脚排列如图4所示,当其在上电加载时钟后,所有通道都禁止输出。系统通过采样DataWidth来确定外围数据接口的宽度,如果采用16bits传输(DataWidth=1),则Data[15:0]都使用;如果采用8bits传输(DataWidth=0),则仅使用Data[7:0],而将高8bits接地。

复位(Reset_b)结束后,在片选(Cs_b)有效的情况下,可以对芯片进行读写操作。对通道的一次完整的读写包括写控制字与读写通道寄存器两个过程,写控制字选中通道内寄存器,读写通道寄存器则可获取通道寄存器信息,只有当合理的数据写入后,且在PWMH-_b有效(PWMH_b=1)时,PWM内部通道才使能输出信号。一般情况下,各通道的输出使能由各通道的控制字寄存器的PWM_EN位决定。

采用控制字自动备份的方式可使控制字的编程更加灵活。它既可以使同一个类型的寄存器(不同通道)一起写控制字,亦可对同一个通道一块操作。但是所有控制字命令都可以在PWM的控制字命令列表中查询。

4 PWM的仿真及验证

PWM的仿真是PWM功能验证的必要环节。可以Modelsim结合脚本文件进行仿真,并采用89C51结合FPGA验证板对整个设计进行验证。[p]

4.1 PWM的仿真

ModeslSim仿真主要观察PWM电路的双向IO端口以及PWM的Regs读写控制时序。对于双向端口的数据交换,可以采用读写控制结合三态门来完好地解决。而对于大量的Regs读写操作,则应通过模拟单片机对外围器件进行操作,并利用Task调用的方式来实现。本文的读写操作仿真结果如图5所示。

从图5可以看到,当采用16 bits读写时,各寄存器通过内部DataInternal数据总线的传输过程与电路设计要求完全一致。RWLogic与DataInterface模块的功能完全符合设计预想。

从图6所示的PWM波形仿真结果可见,PWM输出信号在ClkGen的CycleScale信号控制下,其周期输出编程设定的PWM波形与之完全一致,同时还能异步响应ChannelHold_b信号的输出控制。

4.2 PWM的验证

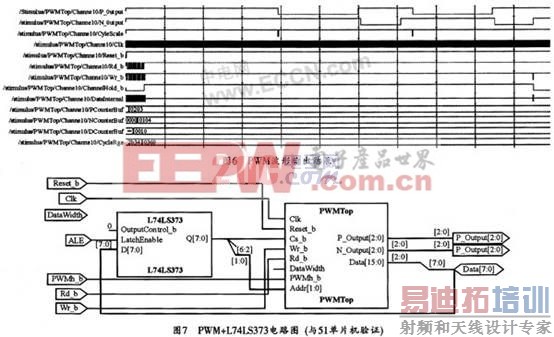

PWM的FPGA验证可采用8 bits数据接口,并用89C51做外围控制器(12 MHz)来对PWM进行操作。为了方便与单片机的接口,可将74LS373锁存器内置到PWM中,其整个数字部分设计如图7所示。

5 结束语

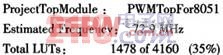

通过Synplify Pro编译后,其最后的结果为:

该方案的整个电路设计占用FPGA资源的35%。对于51系列的单片机而言,该PWM电路可运行的频率远远超过系统频率。因此,在读写时序上完全可以保证整个设计的可靠性。

如果将编译后的pof文件下载到APEX20KEEP20K100E TQ144-2X(Altera)fpga验证板,并采用40 MHz的FPGA时钟,那么,根据软件仿真的步骤,再将读写操作转换为单片机程序烧录到单片机,就可通过示波器清楚的看到,其实际输出与设计完全一致,非常好地实现了当初的设计要求。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...