- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于数字控制器IC的数字电源控制系统设计考量

多年来,电源设计师在如何选择模拟电源控制器才能满足规范要求方面取得了非常丰富的经验知识。但随着数字控制器的引入,这种选择的难度有所增加。数字控制器要求设计师注重更加复杂的IC模块。抗混叠滤波器、模数转换器和数字脉冲宽度调制器是数字控制器IC的核心。对这些模块进行重点考虑是获得卓越的系统总体性能的关键。

高性能微处理器的电源要求正变得越来越高(见图1)。在奔腾系列处理器出现之前,处理器核心工作电压直接来自AC/DC银盒的5V电源输出。随着内核电压的下降和电流要求的提高,业界转而将来自银盒的12V电压输入到同步降压转换器并产生核心电压Vcore。为了尽量降低从12V调整到Vcore所产生的高纹波,从奔4系列处理器开始,多相降压转换器就成为了标准配置。为了满足软启动、顺序上电、电压识别(VID)和线载(LL)、等各种处理器电源规范,业界已有像Intersil公司的HIP6301这样的基于模拟PWM技术的专用多相控制器集成电路。

|

图1:处理器核心电压/电流演变图。 |

除了电压和电流控制外,新的多相控制器还需要满足许多其它规范要求,如VID编程、线载调节、顺序上电、相位电流平衡以及监视与保护等。多相控制器中的PWM功能变成只是所有控制器功能中的一小部分。对控制器提出的更多功能要求以及数字技术的不断发展使得许多公司十分看好数字多相控制的前景。目前已有许多推荐解决方案,从使用数字处理器(DSP)、微处理器和微控制器,到Intersil公司推出的最新软件可编程的混合信号集成电路ISL6592。

数字控制的好处

与模拟控制器相比,数字控制器有许多优势:更高的系统可靠性、灵活性和易于集成和优化。总之,它们能够提供很好的解决方案来满足Vcore电源调整规范中的诸多要求。

基于数字控制器的系统使用更少的元器件,因此可以增加系统的平均无故障工作时间(MTBF)。例如,省去了反馈环路中的所有器件;测试选择和基于设计规范来选择元器件也被软件编程所代替。为了满足新要求而对设计做修改时不需要重新做电路布板,因此可以节省许多工程时间。这些设计修改可以用软件来实现。

新增加的监视保护和预防功能同样会提高系统的可靠性。例如,工程师可以选择监视系统温度来降低电流限制值,或打开风扇。这种方案可以减轻对电源器件和风扇的压力,从而有利于提高系统可靠性,消除对器件规格的额外要求。

通过软件修改控制器能使基于数字控制器的系统变得相当灵活。为了满足新要求,或优化和校正系统,数字控制器可以增加、删除和修改任何系统参数。例如,可以在不修改任何硬件的前提下对同一电压调节器模型(VRM)进行编程,以满足线载、VID、电流或电压要求等不同的处理器规格要求。由于能够非常方便地集成通信功能,因此数字控制器能够容易实现多个系统的集成和级联。例如在多VRM电路板中,不用增加任何硬件即可通过标准通信总线实现电流共享。

数字控制IC的实现

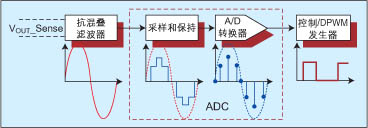

为了选出理想的数字控制器IC,电源供电设计工程师必须考虑模拟控制器IC中一般不会有的许多数字IC模块的性能和功能。数字控制器的核心主要由三个特殊模块组成,它们是:抗混叠(anti-aliasing)滤波器、模数转换器(ADC)和数字脉冲宽度调制器(DPWM),如图2所示。

1. 抗混叠滤波器

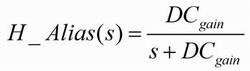

采样理论指出,只有当连续信号中没有高于采样速率一半以上的频率分量时,这个连续信号才能被正确采样。因此,如果采样速率为2MHz,那么实用的抗混叠滤波器在1MHz处就应该有-20dB的增益。抗混叠滤波器的重要性在于它对整个系统带宽的控制效应。例如,如果我们只有一个RC类型的低通滤波器,其传输函数是:

那么为了在2MHz采样频率的一半1MHz处获得-20dB的增益,H_Alias极点应该在100kHz,从而会在100kHz处引入45°的相位延迟。如果电源部分的开关频率为1MHz,那么就很容易获得交越频率为200kHz的模拟控制环。在采用这种数字实现方法时,如果我们利用抗混叠滤波器禁止在反馈环路中引入任何相位延迟,那么交越(crossover)频率将被限制在100kHz以下。为了解决这个问题,我们可以使用具有更多极点的有源滤波器,或提高采样频率。

2. A/D转换器

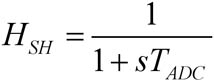

A/D转换器模块主要由二个分电路组成:采样保持和ADC本身。根据,采样保持模块将增加环路中的延时。

可以近似表达为:

其中为A/D转换器的采样周期。

为了减少延时,即减少相位滞后,需要延长A/D转换器的采样周期。

有很多种类的ADC架构可供选择,它们的区别主要在分辨率、带宽、精确度和电源要求方面。主流的ADC架构有闪速(所有判决同时进行)架构、逐次逼近架构(SAR,其中逐次逼近移位寄存器是关键的定义单元)和具有多个闪速电路级的管道式架构。每种架构都有各自的优缺点。

闪速架构:利用2n-1个比较器直接以n位的分辨率测量模拟信号。闪速架构具有速度非常快的优势,因为转换过程在一个周期内就能完成。缺点是它需要大量的比较器,一个n位ADC所需的比较器数量等于2n-1个。例如,一个10位A/D转换器需要1,023个比较器,因此即使对于一个集成控制器硬件电路也会相当复杂。

逐次逼近架构:这种方法使用一个比较器在多个周期内完成转换过程。逐次逼近转换器只需一个比较器就能实现高分辨率的ADC,但它需要n个比较周期才能达到n位的分辨率。SAR的主要缺点是模拟信号的转换过程要花很长的时间,会在反馈环路中引入很大的相位延迟。例如,一个10位转换器将引入的延迟。

|

图2:主要的数字控制器模块。 |

具有多个闪速电路的管道架构:这种架构的性能介于闪速架构和高分辨率逐次逼近架构之间。管道式转换器将转换任务分成p个连续的阶段。每一阶段都是由采样保持电路、n位闪速转换器和n位D/A转换器(DAC)组成。有p个管道阶段、每个阶段有n位闪速转换器的管道式转换器所确定的高速ADC分辨率为位,使用的比较器数量为

。例如,一个10位、2段管道式转换器只需要62个比较器(同样10位的闪速转换器需要1,023个比较器),并且转换过程只需2个采样周期(10位SAR的转换周期需要

)。

从上述有关抗混叠滤波器以及管道式或SAR模数转换器引入的延时的讨论,我们可以明显地看出高采样速率的迫切性。

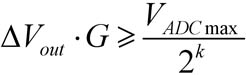

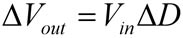

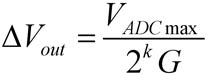

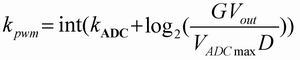

位的数量可以根据要求的测量分辨率决定。为了满足规定的输出电压调整值,ADC分辨率必须能够满足误差小于输出电压允许变化的范围。

如果最大输出电压调整值是,ADC的最大电压是

,通过增益G调整输出电压Vout以满足ADC电压水平,那么ADC的最低有效位必须小于最大波动值和增益的乘积:

,其中k是ADC的位数。

,其中k是ADC的位数。

求解k可以得到:

k=

例如,如果输出电压波动是5mV,输出是2V,ADC的最大输入电压是1V,那么在输入到ADC之前需要G=0.5的增益调整。在这种情况下,至少需要k=10的ADC。

3. 数字脉宽调制器

模拟控制器对所产生的可能脉冲宽度存在固有的限制。而DPWM可以产生离散和有限的PWM宽度集。从稳定状态下的输出角度看,只可能有一组离散的输出电压。由于DPWM是反馈环路中的一部分,因此DPWM的分辨率必须足够高才能使输出不显示众所周知的极限周值。在极限周值中,输出将变成与初始状态无关、并且固定幅度和频率的振荡信号。

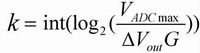

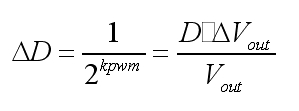

不显示任何极限周值所需的最少位数取决于拓扑、输出电压和ADC分辨率。例如在降压转换器中:,其中D是占空比。

如果对上式求微分,可以得到: ,

,

用代替

,可以得到

。因此,如果PWM调制器是

位,那么最小有效位是:

,

,

根据前文可以得出最小输出波动值为:

,

,

根据上述结果可以得出:

,其中代表ADC的位数。

,其中代表ADC的位数。

就如前例所述的那样,如果输出电压波动Eq13等于5mV,输出电压为2V,ADC的最大输入电压为1V,G=0.5,那么至少需要10位的ADC。当kADC=10位,最小占空比为0.l时,至少需要14位的DPWM。

作者:Zaki Moussaoui

资深应用工程师

Greg Miller

应用工程高级经理

Intersil公司

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...