- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

系统时钟源:PLL合成器与晶振模块的比较

在新电路板设计或再设计中,时钟源应该使用晶体振荡器(XO)模块还是锁相环路(PLL)合成器?无论系统是机架板上的控制板,如乘法线路卡、带转换器的路由器板、服务器群还是站点网络,都需要时钟。那么PLL能节约空间并降低成本吗?也许可以。

典型系统计时时钟信号的产生和分配由一系列功能组成,如驱动增益放大器的振荡器源、转换为标准逻辑电平的部分以及时钟分配网络。这些功能可由元件芯片组或独立封装高度集成元件实现。

系统计时时钟源要求可靠、精确的计时参考,通常为一个晶振。让我们比较一下系统计时时钟的两种晶振源:XO模块和PLL合成器。这两种源的一些关键特性包括成本、板面积、频率精确度和边缘抖动(或相位噪声)。

晶体振荡器时钟

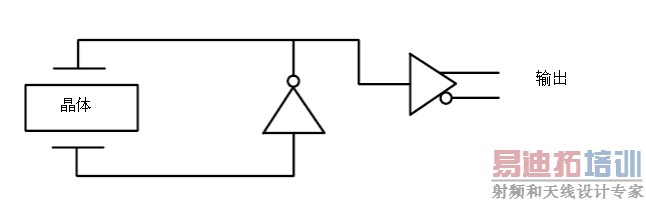

一个典型系统时钟振荡器源通常采用石英晶体谐振器。为使振荡器工作,石英晶振必须处于动态信号环路中,由增益放大器补偿晶振损耗并必须能恰当考虑相位偏移。增益放大器也必须驱动信号到标准逻辑输出电平的转换,以便系统时钟分配网络使用,且最终由时钟接收器使用。

XO时钟通常是密封的或“预制”的,为转换器和输出缓冲器采用的带内部晶振和集成电路的模块。晶体振荡器时钟通常在一个频率工作,而且经常只有一个单端逻辑输出引脚,或一个互补差动输出对。振荡工作可能在晶振基本模式或谐振超调模式中进行。对于晶体振荡器时钟,器件引脚数和封装覆盖面积尽量减小。

图1:典型晶体振荡器时钟

晶体振荡器频率精确性(针对特定数据表目标)一般表示以+/-PPM(每百万零件)范围偏差的均值。更精确的晶体振荡器可能更昂贵,如更高频晶体振荡器。

单独的频率精确度特性由有效位数和不确定性偏差范围,单位以PPM表示。有各种精确性和精度的晶体振荡器模块。

晶体振荡器的边缘抖动或相位噪声是精确性和精度的独立参数。晶体振荡器时钟模块总时钟抖动的单位是ps,而相位噪声仅当规定超过边带频率范围时有效。

PLL合成器

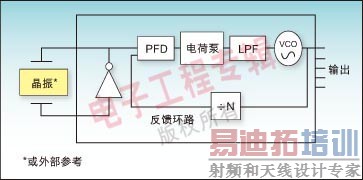

更复杂的系统时钟振荡器源是PLL路合成器时钟生成器,提供更大的设计灵活性和可降低成本。通用的PLL合成器时钟器件一般需要外部晶振并提供额外的特性,如一个以上的输出和单晶振频率倍数的输出频率。通过“向上合频”晶体振荡,系统现在可以使用更高的谐振频率信号。有了额外的内部“向下分频”电路,较低频率链可作为输出。而且,可选输出能将各种输出转换到在插槽中激活(启动)或不激活(关闭)。

先进的芯片电路集成让PLL合成器提供宽泛的扇出功能,用于时钟信号副本的分配。如PLL合成器能提供20个互补差动输出对,或运行到40个单端时钟接收器。可选插槽扇出启动功能可结合可选向上合频或向下分频,得到独立封装中广泛输出的灵活性。

与所有PLL输出相同,VCO输出相位延迟误差相比输入(晶振)参考信号(零相位延迟缓冲),非常接近零。当PLL反馈环路从外部可访问时,输出边缘相位误差是可调整的。这样可以让所选相位边缘位置在给定范围内,包括零延迟。

图2:典型PLL合成器时钟

在实际操作中,PLL合成器的石英晶振也必须处于带有增益放大器的环路中,以补偿晶振损耗并将转换阻抗,这与XO相同。因为PLL频率合成器锁定在晶振信号的相位和频率上,它保留了晶振输入频率的特定频率精确性和精度范围。

当在PLL合成器中进行频率合频时,用PPM表示的精度偏差是一个常数,而绝对范围值做相应乘法。一个10MHz+/-20PPM源可以在PLL中乘以10倍,得到100MHz+/-20PPM信号。PLL中的频率向上合频或向下分频对频率精度影响很微。

与晶体振荡器模块相似,PLL合成器输出边缘抖动或相位噪声是输出精确性和精度的一个独立参数。与晶振输出参考信号和抖动相比,PLL合成器的输出将会产生额外总抖动(RMS)。

在频率范围中低于PLL环路带宽的PLL输入相位噪声(-3dB滚降点)将通过PLL几乎无衰减地传输,而当PLL输入相位噪声较高频率,环路带宽一般以-20dB/decade或更快速度衰减。这样就使PLL合成器能消除输入抖动并减小总抖动和相位噪声。相位噪声可能在各种反馈除法器值范围内明显偏移,而且PLL环路带宽发生变化。PLL低通滤波器可在外部调整环路带宽。

PLL合成器的潜在优点

对于特定的时钟应用频率,采用PLL合成器时钟提供采用较便宜的晶振的可能性,与相同应用的晶体振荡器模块相比,可以工作在一些较低的谐波频率上。一般较高频率的晶振较昂贵,而且供货周期较长。用PLL合成器代替晶体振荡器模块可以缩短供货周期并简化材料单。

采用几个晶体振荡器模块的设计可以分析其公共更高谐波频率。如果此更高谐波频率代由PLL合成器产生,然后进行分频,那么所需的信号频率可以由PLL合成器中的每个时钟接收器使用,而不需要一个或多个晶体振荡器模块。这样就节约了多个晶体振荡器模块的成本,同时腾出板面积。

下一个可能不需要的是各种相应的扇出缓冲器。根据PLL合成器的特性,之前使用晶体振荡器模块和扇出缓冲的任何设计可以从集成在合成器中的扇出受益。因此,元件数量减少,成本下降,所需板面积也减小。

PLL合成器电路也包括频谱散布电路,以降低电磁干扰(EMI)。一个PLL合成器可以提供几个低频时钟信号的多个谐波副本,而且系统或背板上的EMI减小。之后的子卡接收器可采用第二个PLL合成器,在更高时钟频率产生并分配本地纯净信号。

作者:Paul Shockman

高级应用工程师

安森美半导体公司

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:8MHz极速开关调整器技术

下一篇:基于数字控制器IC的数字电源控制系统设计考量