- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

低功率全集成、部分集成和分立开关电源方案比较

便携式设备适配器设计需要综合考虑高效率、低空载功耗、宽交流电压输入、电磁干扰、PCB尺寸以及成本等多方面的要求,全集成架构具有较高的性能但成本较高,而分立方案成本低但开关频率不稳定以及开关损耗高,部分集成方案有效综合了全集成和分立方案的特点。本文对这些不同架构进行了深入分析。

随着手机及PDA等便携式设备的应用日益增加,对低功率电源适配器的需求也在不断增加。这些电源的典型特性包括符合安全标准的交流隔离、1至5瓦的输出功率、5Vdc ( 5%的输出电压、符合Blue Angel(EN6100-3-2)要求的低空载功耗、低电磁干扰(EMI),以及其他开关电源(SMPS)所需的故障保护等。其中大多数还要求具有85至265Vac的交流输入电压。

采用交流电频率(30~80Hz)变压器与整流器的线性电源性价比很高,且能满足隔离、故障保护及EMI要求。但这些器件不仅笨重,还不能满足宽输入电压及空载功耗要求,且一般不能满足电压调整要求。而由整流器与回扫转换器所组成的SMPS则能满足以上要求,但其成本要远高于线性电源,尤其当采用全集成芯片架构时。

由于输出功率较小以及电压调整要求相对较宽松,且与系统成本相比,功率密度及效率不是主要的约束条件, 因此SMPS可用分立半导体器件来实现以降低系统成本。尽管这种方法可满足基本的电压要求,但却不是固定频率设计,因为PWM频率会随输出电流及输入交流电压的变化而改变。此外,谐波也会在某些应用中引起噪声问题。由于导通及关断速度较慢,故其开关损耗也较大,因为没有用于高压MOSFET的驱动器。由于未采用空载跳周期(cycle skipping)模式,因此也可能不满足Blue Angel标准的要求,并且也难以实现一些基本的保护功能,如过热保护、过压保护及欠压保护等,而这些功能通常都是SMPS所要求的。

基于以上这些原因,人们开发出了一种部分集成的解决方案,这种解决方案不仅能消除分立解决方案有关的局限性,而且成本还低于全集成方案。

其他SMPS架构

面向低功率及通用输入电压应用的典型SMPS架构尽管都用一个由回扫拓扑及隔离反馈电路所组成的基本平台,但不同的架构其初级有很大的差异。全集成方案与分立器件方案是目前最流行的两种解决方案。

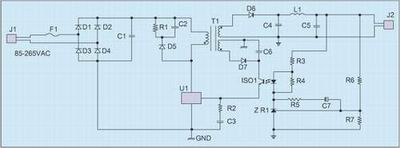

1. 全集成方案

图1为一种典型全集成架构。U1为用于全输入电压范围的高电压IC,该芯片在一个硅片上集成了高电压开关晶体管与控制逻辑,而没有采用目前流行的将两块裸片置于一个封装中的混合设计。图1中反馈信号通过光耦ISO1加于IC的Bias/FB(偏压/反馈)端,变压器的偏置线圈为IC提供电源。

在上电期间,偏置线圈上没有感应电压,IC电源由从高压端至偏压端与储能电容C3的内部电流源提供。当偏压达到工作电平时,IC即开始以不断增加的占空比进行开关(软启动)。启动后,由偏置线圈为IC提供电源,而内部电流源则由控制逻辑关断。IC拥有内部检流电路,以提供逐周期的电流限制。

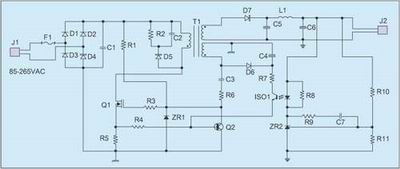

2. 分立器件方案

图2为一种典型分立实现方案。分立高压晶体管最初由直流总线通过R1偏置并由ZR1箝位,当晶体管栅极电压达到导通阀值时,Q1打开。当通过检流电阻的漏电流达到预定值时,被关断的控制晶体管Q2被偏置电压打开,将Q1关断。Q1关断后,储存在变压器中的能量即传递到次级线圈及偏置线圈,并通过C3与 R6构成的RC网络给Q1栅极加一个正偏压,RC网络的时间常数决定关断时间。反馈信号通过光耦取得并加于Q2的基极,以对基极电流进行调整。基极电流调整导致对导通时间间隔的调整,进而实现对输出电压的调整。

由于通用分立器件的生产批量很大,故与专用集成电路(ASIC)解决方案相比,分立解决方案的系统成本是所有架构中最低的,但这种方法也有一定的局限性。首先,开关频率不恒定,由于关断间隔相对恒定,故占空比改变将引起频率改变;其次,开关转换速度缓慢,因为它没有ASIC解决方案中所采用的低阻抗栅极驱动器。故在同一频率、电压及电流上,Q1的开关损耗远高于ASIC解决方案的开关损耗。

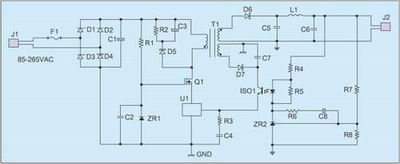

3. 部分集成方案

基于上面对这两种架构的讨论,以下介绍一种部分集成式架构。图3所示的这种架构旨在提供适中的系统成本,同时保留大部分ASIC架构的性能优势。该架构的系统成本之所以较低,是因为采用了通用分立高压晶体管,以及低压工艺控制器IC。

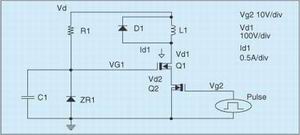

a. 源极开关控制

作为对用于开关高压MOSFET的传统栅-源驱动的一种替代,可在IC输出中采用一种源极开关结构。在这种源极开关结构中,控制器是通过源极来驱动外部MOSFET,而不是传统PWM方法中驱动栅极。如图4所示,外部MOSFET Q1的栅极通过ZR1被箝位在一个恒定电压上,该电压足够高,以使晶体管充分导通,其典型值为14V。而电容C1(远大于栅极输入电容)则用来在每一开关周期暂时储存栅极电荷。Q2的开关极性与Q1同步,当Q2打开时,Q1的源极被拉至接近于0V,而C1中所储存的电荷则被传递到栅极,从而将Q1打开。当Q2关断时,Q1的漏电流继续流向Q2。Q2漏极电压的升高迫使Q1的栅极电容对充电电容放电。当Q2的漏极电压高于其栅极电压减去Q1的栅极阀值电压时,Q1关断。

采用源极开关控制具有许多优势。首先,由于驱动及检流共用一个引脚,故能减少一个引脚,从而简化IC封装;其次,由于IC的栅极驱动器只需驱动具有较低栅极阀值电压的开漏极FET,故能采用低电源电压,而无需使用充电泵电路,典型的PWM IC要求最小10V的电源电压,而建议的IC则只需6V,由于电源电压较低,因此可以采用亚微米工艺来提高裸片面积使用效率;第三,开关及启动电流源只需使用一个外部高压MOSFET,而栅极控制方法则需要用另外的高压器件来提供启动偏置电源。

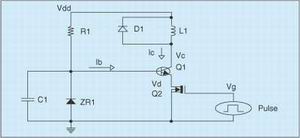

b. 射极开关控制

基于成本考虑,设计工程师有时希望采用双极型晶体管来作为带射极开关控制的高电压开关,如图5所示。Q1的基极在关断状态下被箝位在一个安全电压上,因此Q2上所加的电压为箝位电压减去Q1的Vbe (0.7V)。为打开Q1,先打开驱动场效应晶体管 Q2,然后基极电流再流进Q1与Q2。起始基极电流由电容C1提供,直至Q1完全饱和。导通期间的基极电流由Vdd通过电阻R1及Q2的导通电阻提供。为关断Q1,先关断Q2以迫使集电极电流从基极流向充电电容C1,从而将Q1关断。

Q2,然后基极电流再流进Q1与Q2。起始基极电流由电容C1提供,直至Q1完全饱和。导通期间的基极电流由Vdd通过电阻R1及Q2的导通电阻提供。为关断Q1,先关断Q2以迫使集电极电流从基极流向充电电容C1,从而将Q1关断。

采用射极开关控制,除具有源极开关控制的优点外,还具有以下两个优势:由于集电极电流远大于基极电流,故与传统基极开关方法相比,可以以高得多的速率来消除过量载流子,这能极大地加速关断过程;(2) 射极开关关断下的Q1反向偏置安全工作区要远大于采用栅极关断时的反偏安全工作区,这是因为当射极关断时没有射极电流,故集电极-射极击穿电压BVCEO变成BVCBO,而在基极开关方法中,BVCBO通常都要高于BVCEO极限值。

C. IC/分立器件方案

我们建议的方法采用源极开关方法来控制高压MOSFET,Q1的栅极通过ZR1被箝位在一个高于阀值的电压上。在采用低压MOSFET的开漏极配置中,源极与IC输出相连。采用源极开关技术可减少引脚数,因为输出引脚还用于检流。通过将FB引脚与偏压引脚合并,可以采用TO-92塑料封装,器件只有三个外部引脚,从而减少IC成本及对PCB空间的占用。

这种器件可减少外部器件数,进而减少系统成本及空间。PWM控制器集成了振荡器、检流、参考电压等。反馈电压通过一个内部电压分配器从BIAS输入上获得。BIAS电压由电流源提供,并受电源输出电压的调整,通常用一个与输出耦合的光耦来实现。

全PWM功能可以通过3个外部连接来实现:SW端、BIAS/FB端及GND端。3端组合及低电压工作可使IC采用TO-92等小型封装,以便用于通孔安装。类似低成本封装亦可用于表贴安装,这能极大地减少电源IC的成本及PCB面积。

d. 启动过程

启动时,高电压晶体管Q1的漏极电流通过控制器U1的内部电阻电路及外部电阻R3对电容C4充电(图3)。当Bias/FB端子上的电压达到工作电平时,IC即开始以不断增加的占空比产生PWM脉冲,直至输出电压达到其预定值。然后,再对占空比进行调整以便调整输出电压。一旦控制器开始工作,内部电阻即被IC切断,而转由偏置线圈给IC提供偏置。

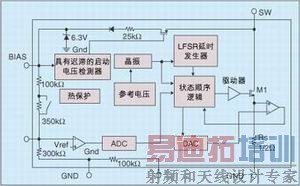

数字实现

PWM控制器的数字实现具有许多优于模拟实现的优势,包括相对复杂算法的精确执行、无需硬件修改的再配置以及便利的参数调整、测试及校准等。数字实现框图如图6所示。我们所建议的数字实现IC采用模数转换器(ADC)来提供反馈电压信号,Δ-Σ ADC则采用过采样及十取一技术来滤除纹波。

主时序发生器控制PWM控制器的所有时序,它由振荡器系统驱动,故所有时序都互相跟踪并同步。时序发生器为一个从零开始并计数至最终值的二进制计数器,计数器在每周期结束时复位,并重复此过程。最终计数值由一个线性反馈移位寄存器确定。最终值至少为64次计数,最高可以达到127次。可以通过改变周期来减少EMI,该操作由抖动控制(dither command)模块来实现,空、最小及最大占空比都由该模块产生。软启动及电压模式控制可减小最大占空比。

由于是数字实现,故IC的许多参数可在晶圆级进行调整,这些调整选项不仅能实现芯片的灵活性及芯片的多样性,而且还能为电源设计工程师提供各种设计选项来缩短产品开发周期。主要调整选项包括:

开关频率:65kHz至256kHz

电流限制 :300mA至500mA

电压/电流模式:可选

频率抖动:开/关

频率抖动

IC拥有旨在减少EMI辐射的工厂可编程频率抖动特性,可对多种抖动进行编程以满足EMI要求。

跳周期模式

当达到最小PWM占空比(约3%)时,IC即进入轻负载的跳脉冲工作模式。跳脉冲工作可显著提高轻负载时的工作效率。

关断与自动重启

如果遇到输出短路或过载情况,则偏置线圈电压会跌至关断阀值(约3.5V)以下,PWM即停止工作并进入重启程序。

应用举例

如图3所示,采用我们所建议的PWM控制器IC开发一种5W通用输入电源以验证其工作及灵活性,图中未绘出EMI线滤波器。我们采用3端PWM控制器U1及通用高压场效应晶体管Q1作为开关元件,且设计已经过成本及空间使用效率优化。如上所述,齐纳二极管ZR1将晶体管Q1的栅极电压箝位在14V上,Q1源极端与控制器的SW引脚相连以用于开关驱动及电流检测。输出电压通过光耦ISO1检测,并通过电阻分压网络R7及R8编程。ZR2提供准确的参考电压以及将输出电压调节到最稳定的电压范围的误差放大器功能。在此应用中,是在130kHz开关频率、400 mA限制及电流模式控制上对控制器进行调整。

图3所示电源的参数如下:

输入交流电压:85至265VAC;输入频率:47至 63 Hz;电压:6.2VDC;电流(连续):800 mA;线路(输入电压)调节: (1%;负载调节: (3%;输出纹波:100mVpp;工作温度:0 至40 (C;效率(满负载,高输入电压):70%;空载功耗:200mW。

实验室评估结果表明,该电源能很好地满足设计指标要求。电源上电的过冲很小,只有大约5ms的上升时间;在高输入及满负载输出稳态工作条件下的输出纹波大约为50mVpp;负载调节大约为(2.7%(包括电缆损耗),输入电压调节约为0.3%;满负载效率约为80%;空载功耗随输入电压的增加而增加,在240Vac输入上测得的指标约为140mW。

作者:Chuck Wong

Mark Dong

Tyco电子公司

Email:cwong@tycoelectronics.com

Shawn Laliberte

Orion设计技术公司

Email:laliberte@orion-design.com

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:热插拔电路的过热保护新方法

下一篇:如何为汽车电子系统设计成本低廉的电源