- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

用于便携音响设备的自适应Q电流控制AB类功率放大器

如今的蜂窝电话、PDA、MP3播放机等便携式设备都需要配备功率放大器来驱动微型扬声器,且要求功率放大器待机功耗低、效率高、失真小,这些放大器可利用传统的线性和开关技术来实现。开关放大器即所谓的D类放大器,能同时满足低功耗(高效率)和高音质的要求,但却需要对输出进行滤波处理,因而增加了运行成本。本文介绍自适应Q电流控制AB类功率放大器,可同时满足对谐波失真、功耗以及成本的要求。

如今的蜂窝电话、PDA、MP3播放机等便携式设备都需要配备功率放大器来驱动微型扬声器,且要求功率放大器待机功耗低、效率高、失真小,这些放大器可利用传统的线性和开关技术来实现。开关放大器即所谓的D类放大器,能同时满足低功耗(高效率)和高音质的要求,但却需要对输出进行滤波处理,因而增加了运行成本。本文介绍自适应Q电流控制AB类功率放大器,可同时满足对谐波失真、功耗以及成本的要求。

为了将大型输出器件硬开关所产生不必要的能量辐射降至最低,设计者必须对PCB布局结构和噪声滤波器的设计做出额外考虑,这些因素使得设计人员倾向采用线性放大器而非D类放大器。在多种模拟放大器中,AB类能满足一定的总谐波失真(THD)和低功耗要求,一般来说,失真减少与输出Q电流(IQ)成正比,但功率效率却与其成反比。为了满足这两方面的要求,自适应Q电流控制(AQC)技术便应运而生。

为了将大型输出器件硬开关所产生不必要的能量辐射降至最低,设计者必须对PCB布局结构和噪声滤波器的设计做出额外考虑,这些因素使得设计人员倾向采用线性放大器而非D类放大器。在多种模拟放大器中,AB类能满足一定的总谐波失真(THD)和低功耗要求,一般来说,失真减少与输出Q电流(IQ)成正比,但功率效率却与其成反比。为了满足这两方面的要求,自适应Q电流控制(AQC)技术便应运而生。

AQC电路能按照输出失真的程度来提高IQ,当没有信号输入或感应不到输出失真时,它不会激活。采用AQC电路设计的功放在以1W功率驱动8Ω负载时,整个音频带宽的THD低于0.3%,且静态下仅消耗2.6mA电流。

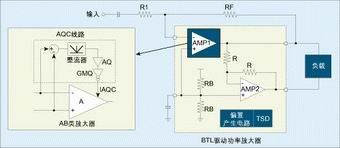

在5V电压下向8Ω负载输出1W功率时,需要采用如图1所示的桥接负载结构(BTL)。AMP1输出显示了由于输出阶段推挽作用所产生的失真,这种失真会被AMP2放大,而AMP2的输出则会受到失真和其自身产生的失真所影响,将使THD性能降低6dB。不过有一个非常简单的方法,即引进BTL驱动电路并改动很少元件就可改变放大器的整体增益。

图1所示的AQC单元由以下几部分组成:微分放大器、整流器、增益级(AQ)和跨导(GMQ)。其中,失真值可通过比较两个放大器的输入而获得。通常+/-输入利用负反馈和高回路增益进行虚拟短接,然而随着输出失真增加,输入会渐渐偏离虚拟接地点,这样失真就会在输入端出现。为了产生IQ控制信号(IAQC),无论所检测的失真极性为何,都要使用整流器。经整流的信号将通过AQ放大,最后由GMQ生成IAQC,并流入AB类放大器的Q偏置电路。

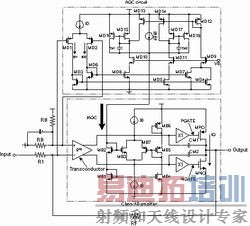

图2是一个AQC AB类放大器,失真电压被转换为源自MD1和MD2的电流ID1和ID2。如果ID1>ID2,MD17-18将被激活;反之,MD15-16则被激活。因此IAQC信号与所检测到的失真绝对值成正比,AQ增益由MD16和MD15(MD18和MD17)的比值决定。最后,IAQC信号被传输到MB2和MB5,这样输出失真就可自适应地控制经过MPO和MNO的IQ电流。

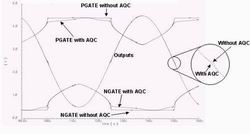

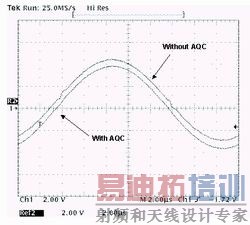

在MPO和MNO之前插入的两个缓冲器也可提升THD性能,这是由于缓冲器不但能增加放大器带宽,还可提高门驱动能力。图3显示了在温度Tj=120℃、8Ω负载、4Vpp 20kHz信号和5V电源情况下,使用BSIM3V3模型 得出的瞬变模拟结果。如不采用AQC,PGATE和NGATE信号分别在MPO与MNO截止态保持恒压;反之如应用AQC,每个信号都会由失真量控制。

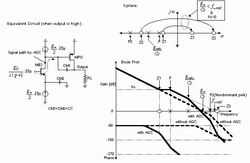

当AQC被激活时,将严重影响放大器的稳定性,特别是在两个输出晶体管中只有一个被激活的情况下,更容易引发稳定性问题。图4所示为高输出电压时的等效电路。AQC模拟为一个单极点系统,在P点有一个极点。由于采用了AQC,整个传递函数具有额外两个极点和两个零点,包括一个次要极点(P2)。两个极点分别被置于P点和gmB3/CM2(P3)点,其中gmB3为MB3的跨导。就零点来 说,两个零点分别被置于P点下方和P3点上方。如果AQC能达到以下两个条件,两个零点即会成为RHP零点,严重影响稳定性。这两个条件是:AQC具有负增益(MD15-16接通);AQC的整体增益频率fuAQC高于主放大器的增益频率。在本设计中,利用Cc1和Cc2使AQC的带宽小于放大器的带宽,因而保证了稳定性。

在功率应用中,由于DMOS技术采用垂直器件结构(如垂直NPN双极晶体管),因此具有很多优点,包括高电流驱动能力、低Rds导通电阻和高击穿电压。然而,DMOS技术需要额外的加工工艺和更高制造成本,故推荐使用传统0.8微米10V BiCMOS工艺经济制造的方案。为了增加输出动态范围,传输高电流的金属线设计得越大越好。此外在VDD、接地端和输出引脚处均采用双焊接线。一般来说,输出晶体管的DCGS比最低设计要求大一些,这是因为DCGS电阻器具有限流电阻器的作用,可提高抗ESD性能。本设计并没有采用增大DCGS的方式,而是在漏极与源极电路大量采用二层金属走线,以减小电阻的集中,因此本芯片能在HBM和MM模型下分别通过±2.5kV和±300V ESD电压测试。

BiCMOS工艺经济制造的方案。为了增加输出动态范围,传输高电流的金属线设计得越大越好。此外在VDD、接地端和输出引脚处均采用双焊接线。一般来说,输出晶体管的DCGS比最低设计要求大一些,这是因为DCGS电阻器具有限流电阻器的作用,可提高抗ESD性能。本设计并没有采用增大DCGS的方式,而是在漏极与源极电路大量采用二层金属走线,以减小电阻的集中,因此本芯片能在HBM和MM模型下分别通过±2.5kV和±300V ESD电压测试。

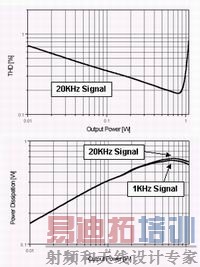

为了说明本设计如何在高频下有效消除交叉干扰失真,图5显示了在8Ω负载、4Vpp和50kHz条件下的输出波形。尽管这里的放大器是针对音频应用,其结果仍表明采用AQC技术来实现低THD高频放大器(如xDSL线路驱动电路)是可行的。图6所示分别为THD+N及功率耗散与输出功率的对比,在频率为20kHz及输出为1W时,THD+N仅为0.3%,1kHz和20kHz信号的功率耗散仅有细微的差别,这是由于AQC在20kHz时才被激活,故功率耗散仅增加了0.03W。

作者: Jong-Tae Hwang

Han-Seung Lee

飞兆半导体公司功率产品部

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...